赛灵思FPGA IO_BUF学习

一、IO_BUF概述

赛灵思7系列FPGA,每个BANK中都存在存储深度低的IN_FIFO和OUT_FIFO(统称IO_BUF),IO_FIFO是为了内存应用设计的,但是也可以作为通用资源使用。一般用于IOLGIC(ISERDES/IDDR、OSERDES/ODDR)的扩展组件使用,也可以用于FIFO资源。

每个BANK包含4个IO_FIFO,即每个字节组有一个IO_FIFO。

每个IO_FIFO有一个768bits的存储阵列,可以排列为12组4bits数据或者10组8bits数据。存储深度为9(1个输入寄存器、7个FIFO存储单元、1个输出寄存器)。

IO_FIFO可以工作在两个模式下,一个是4*4模式(输入输出比为1:1),另一个是4*8 / 8*4模式(输入输出比为1:2 / 2:1)IO_FIFO用作buffer时,输入输出为两个时钟域,与常规的FIFO功能类似。IO_FIFO用作2:1的串行器或者解串器时,可以降低对FPGA内部架构的性能要求。

二、IN_FIFO

4*4模式:该模式有12个4bits输入D,12个4bits输出Q。

D0[3:0]~D9[3:0]分别对应着Q0[3:0]~Q9[3:0];D5[7:4]和D6[7:4]是两个额外的数据输入端口(作为D10[3:0]和D11[3:0]),分别对应着Q5[7:4]和Q6[7:4](作为Q10[3:0]和Q11[3:0])。具体数据对应关系如下表:

4*8模式:该模式有10个4bits输入D,10个 8bits输出Q。4bits输入被组合成8bits输出。

输入数据D与输出数据Q的对应关系如下:

原语介绍

IN_FIFO #(

.ALMOST_EMPTY_VALUE(1), // Almost empty offset (1-2)

.ALMOST_FULL_VALUE(1), // Almost full offset (1-2)

.ARRAY_MODE("ARRAY_MODE_4_X_8"), // ARRAY_MODE_4_X_8, ARRAY_MODE_4_X_4

.SYNCHRONOUS_MODE("FALSE") // Clock synchronous (FALSE)

)

IN_FIFO_inst (

// FIFO Status Flags: 1-bit (each) output: Flags and other FIFO status outputs

.ALMOSTEMPTY(ALMOSTEMPTY), // 1-bit output: Almost empty

.ALMOSTFULL(ALMOSTFULL), // 1-bit output: Almost full

.EMPTY(EMPTY), // 1-bit output: Empty

.FULL(FULL), // 1-bit output: Full

// Q0-Q9: 8-bit (each) output: FIFO Outputs

.Q0(Q0), // 8-bit output: Channel 0

.Q1(Q1), // 8-bit output: Channel 1

.Q2(Q2), // 8-bit output: Channel 2

.Q3(Q3), // 8-bit output: Channel 3

.Q4(Q4), // 8-bit output: Channel 4

.Q5(Q5), // 8-bit output: Channel 5

.Q6(Q6), // 8-bit output: Channel 6

.Q7(Q7), // 8-bit output: Channel 7

.Q8(Q8), // 8-bit output: Channel 8

.Q9(Q9), // 8-bit output: Channel 9

// D0-D9: 4-bit (each) input: FIFO inputs

.D0(D0), // 4-bit input: Channel 0

.D1(D1), // 4-bit input: Channel 1

.D2(D2), // 4-bit input: Channel 2

.D3(D3), // 4-bit input: Channel 3

.D4(D4), // 4-bit input: Channel 4

.D5(D5), // 8-bit input: Channel 5

.D6(D6), // 8-bit input: Channel 6

.D7(D7), // 4-bit input: Channel 7

.D8(D8), // 4-bit input: Channel 8

.D9(D9), // 4-bit input: Channel 9

// FIFO Control Signals: 1-bit (each) input: Clocks, Resets and Enables

.RDCLK(RDCLK), // 1-bit input: Read clock

.RDEN(RDEN), // 1-bit input: Read enable

.RESET(RESET), // 1-bit input: Reset

.WRCLK(WRCLK), // 1-bit input: Write clock

.WREN(WREN) // 1-bit input: Write enable

);三、OUT_FIFO

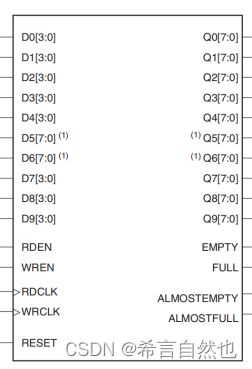

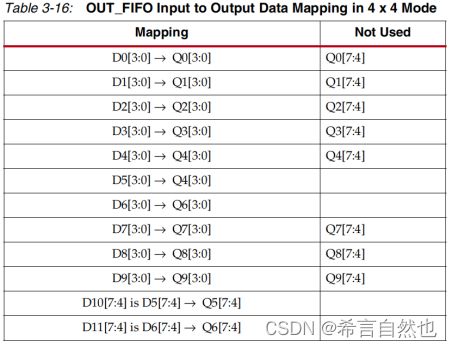

4*4模式:该模式有12个4bits输入D,12个4bits输出Q。

D0[3:0]~D9[3:0]分别对应着Q0[3:0]~Q9[3:0];D5[7:4]和D6[7:4]是两个额外的数据输入端口(作为D10[3:0]和D11[3:0]),分别对应着Q5[7:4]和Q6[7:4](作为Q10[3:0]和Q11[3:0])。具体数据对应关系如下表:

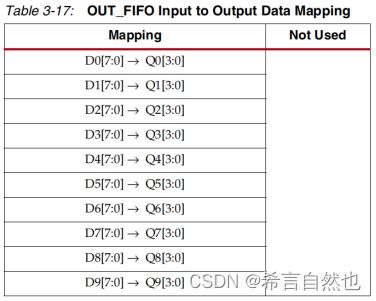

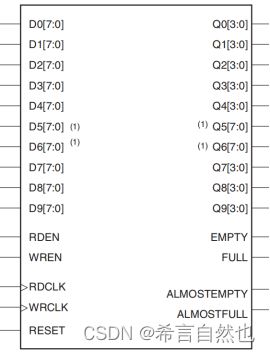

8*4模式:该模式有10个8bits输入D,10个 4bits输出Q。8bits输入被分解成4bits输出。

输入数据D与输出数据Q的对应关系如下:

原语介绍

OUT_FIFO #(

.ALMOST_EMPTY_VALUE(1), // Almost empty offset (1-2)

.ALMOST_FULL_VALUE(1), // Almost full offset (1-2)

.ARRAY_MODE("ARRAY_MODE_8_X_4"), // ARRAY_MODE_8_X_4, ARRAY_MODE_4_X_4

.OUTPUT_DISABLE("FALSE"), // Disable output (FALSE, TRUE)

.SYNCHRONOUS_MODE("FALSE") // Must always be set to false.

)

OUT_FIFO_inst (

// FIFO Status Flags: 1-bit (each) output: Flags and other FIFO status outputs

.ALMOSTEMPTY(ALMOSTEMPTY), // 1-bit output: Almost empty flag

.ALMOSTFULL(ALMOSTFULL), // 1-bit output: Almost full flag

.EMPTY(EMPTY), // 1-bit output: Empty flag

.FULL(FULL), // 1-bit output: Full flag

// Q0-Q9: 4-bit (each) output: FIFO Outputs

.Q0(Q0), // 4-bit output: Channel 0 output bus

.Q1(Q1), // 4-bit output: Channel 1 output bus

.Q2(Q2), // 4-bit output: Channel 2 output bus

.Q3(Q3), // 4-bit output: Channel 3 output bus

.Q4(Q4), // 4-bit output: Channel 4 output bus

.Q5(Q5), // 8-bit output: Channel 5 output bus

.Q6(Q6), // 8-bit output: Channel 6 output bus

.Q7(Q7), // 4-bit output: Channel 7 output bus

.Q8(Q8), // 4-bit output: Channel 8 output bus

.Q9(Q9), // 4-bit output: Channel 9 output bus

// D0-D9: 8-bit (each) input: FIFO inputs

.D0(D0), // 8-bit input: Channel 0 input bus

.D1(D1), // 8-bit input: Channel 1 input bus

.D2(D2), // 8-bit input: Channel 2 input bus

.D3(D3), // 8-bit input: Channel 3 input bus

.D4(D4), // 8-bit input: Channel 4 input bus

.D5(D5), // 8-bit input: Channel 5 input bus

.D6(D6), // 8-bit input: Channel 6 input bus

.D7(D7), // 8-bit input: Channel 7 input bus

.D8(D8), // 8-bit input: Channel 8 input bus

.D9(D9), // 8-bit input: Channel 9 input bus

// FIFO Control Signals: 1-bit (each) input: Clocks, Resets and Enables

.RDCLK(RDCLK), // 1-bit input: Read clock

.RDEN(RDEN), // 1-bit input: Read enable

.RESET(RESET), // 1-bit input: Active high reset

.WRCLK(WRCLK), // 1-bit input: Write clock

.WREN(WREN) // 1-bit input: Write enable

);四、IO_FIFO的使用

1、IO_FIFO的复位信号是异步复位。

为了能够成功复位,需要复位信号至少保持4个读写时钟中较慢的那个时钟的周期数。另外在复位有效时,读写信号RDEN、WREN必须保持低电平。

另外,读写数据之前,必须保证读写时钟稳定,若时钟不稳定,则必须复位一下IO_FIFO。

2、EMPTY和FULL标志。

前面说到,一个FIFO有9个字的深度,分别为一个输入寄存器,7个FIFO缓存和1个输出寄存器。

当FULL有效时,表示输入寄存器与7个深度的FIFO满了,输出寄存器被忽略。

EMPTY指示输出寄存器的状态,当EMPTY有效时,表示输出寄存器无数据。

3、ALMOSTEMPTY和ALMOSTFULL。

.ALMOST_EMPTY_VALUE(1), // Almost empty offset (1-2)

.ALMOST_FULL_VALUE(1), // Almost full offset (1-2)

数值配置成1的时候表示,IO_FIFO内只有1个字可以被写入或者被读出。

数值配置成2的时候表示,IO_FIFO内只有2个字可以被写入或者被读出。