Verilog基本语法之循环语句(六)

循环语句分为以下4种:

for语句——通过三个步骤来决定语句的循环执行:

1.给控制循环次数的变量赋初值;

2.判定循环执行条件,若为假则跳出循环;若为真,则执行指定语句后,转到第三步

3.修改循环变量的值,返回第二步

repeat——连续执行一条语句n次;

while——执行一条语句,直到循环条件不满足;若一开始条件不满足,则该语句一次也不能执行

forever——无限连续的执行语句,可用disable语句中断。

for语句

形式:

for(循环变量赋初值;循环执行条件;循环变量增值) 执行语句

例:用for语句描述7人投票表决器:超过4人投赞成票,则表决通过

module vote7(

output pass,

input [6:0] vote

);

reg [2:0] sum; //sum 为reg变量,用于统计赞成的人数

integer i;

reg pass;

always @(vote)

begin

sum = 0; //sum初始值为0

for(i=0;i<=6;i++) //for语句

if(vote[i]) sum=sum+1; //只要有人投赞成票,sum加1

if(sum[2]) pass =1; //若超过4人,pass为1

else pass =0;

end

endmodule 例:用for语句初始化memory

begin:init_mem

reg [7:0] tempi; //存储器的地址变量

for(tempi=0;tempi例:用for语句实现两个二进制数乘法

module mult_for (outcome,a,b);

parameter size =8;

output [2*size:1] outcome;

input [size;1] a,b;

reg [2*size:1] outcome;

integer i;

always@(a or b)

begin

outcome = 0;

for(i=1;i<=size;i=i+1)

if(b[i]) outcome = outcome +(a<<(i-1));

end

endmodulerepeat语句(不可综合)

无条件连续执行一条或多条语句n次

格式:

repeat(循环次数表达式)语句

例:用repeat语句和移位操作实现两个8位二进制数乘法

module mult_repeat(outcome,a,b);

parameter size=8;

output[2*size:1] outcome;

input [size:1] a,b; //a 为被乘数,b为乘数

reg [2*size:1] outcome;

reg [2*size:1] temp_a; //中间变量,存放操作数a左移移位的结果

reg [2*size:1] temp_b; //中间变量,存放操作数b右移移位的结果

always@(a or b)

begin

outcome = 0;

temp_a = a;

temp_b = b;

repeat(size)

begin

if(temp_b[1]) //如果tem_b的最低位是1,则执行下面加法

outcome = outcome + temp_a;

temp_a = temp_a <<1; //操作数a左移一位,以便代入上式,求部分积

temp_b = temp_b >>1; //操作数b右移一位,以便取temp_b【1】

end

end

endmodule while 语句

有条件的执行一条或多条语句

首先判断循环执行条件表达式是否为真。若为真,则执行后面的语句或语句块;然后再回头判断循环执行条件表达式是否为真,若为真,再执行一次后边的语句;如此不断,直到条件表达式不为真.

格式:while(循环执行条件表达式) 语句

注1:首先判断循环执行条件表达式是否为真,若为假,则其后的语句一次也不执行

注2:在执行语句中,必须有一条改变循环执行条件表达式的值的语句

注3:while语句只有当循环块有事件控制(即@(posedge clk))时才可综合。

例:用while语句对一个8位二进制中值为1的位进行计数

module count1s_while(count,rega,clk);

output [3:0] count;

input [7:0] rega;

input clk;

reg [3:0] count;

always@(posedge clk)

begin:count1

reg[7:0] tempreg; //用作循环执行条件表达式

count =0; //count初始值为0

tempreg = rega; //tempreg初值为rega

while(tempreg) //若tempreg非0,则执行下边语句

begin

if(tempreg[0]) count = count + 1;

//只要tempreg最低位为1,则count加1

tempreg = tempreg >>1; //右移1位

end

end

endmodule例:用for语句对一个8位二进制中值为1的位进行计数

module count1s_for_good(count,rega);

output [3:0] count;

input [7:0] rega;

reg [3:0] count;

always@(rega)

begin:block

integer i;

count = 0;

for(i=0;i<=7;i++)

if(rega[i]) count = count +1;

end

endmoduleforever语句

无条件连续执行forever后面的语句或语句块。

格式:forever 语句;

常用在测试模块中产生周期性的波形,作为仿真激励信号。

常用disable语句跳出循环。

注:不同于always语句,不能独立写在程序中,一般用在initial语句块中。

语句的顺序执行

在always模块内,逻辑按书写的顺序执行。

顺序语句——always模块内的语句

在always模块内,若随意颠倒赋值语句的书写顺序,可能导致不同的结果

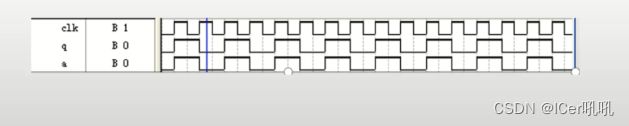

module serial2(q,a,clk);

output q,a;

input clk;

reg q,a;

always @(posedge clk)

begin

a = ~q;

q = ~q;

end

endmodulealways模块,assign语句,实例元件都是同时执行的,它们在程序中的先后顺序对结果并没有影响。

module parall1(q,a,clk);

output q,a;

input clk;

reg q,a;

always @(posedge clk)

begin

q = ~q;

end

always @(posedge clk)

begin

a = ~q;

end

endmodulemodule parall2(q,a,clk);

output q,a;

input clk;

reg q,a;

always @(posedge clk)

begin

a = ~q;

end

always @(posedge clk)

begin

q = ~q;

end

endmodule