关于SoC设计概论

目录

晶体管:

芯片制造流程:

集成电路分工:

Soc设计的发展趋势:

SoC设计:

此为一个学习记录文,内容可能从书上《SoC设计方法与实现,郭炜等电子工业出版社》来,也可能从网络来。

晶体管:

晶体管泛指一切以半导体材料为基础的单一元件,包括各种半导体材料制成的二极管、三极管、场效应管、晶闸管(后三者均为三端子)等。

其响应速度快,准确性高,晶体管可用于各种各样的数字和模拟功能,包括放大,开关,稳压,信号调制和振荡器。晶体管可独立包装或在一个非常小的区域,可容纳一亿或更多的晶体管集成电路的一部分。

1947年12月,晶体管出现后,人们就能用一个小巧的、消耗功率低的电子器件,来代替体积大、功率消耗大的电子管了。晶体管的发明又为后来集成电路的诞生吹响了号角。

半导体(semiconductor)指常温下导电性能介于导体与绝缘体之间的材料,它导电性可控,范围从绝缘体到导体之间的材料。(我们通常把导电性差的材料,如煤、人工晶体、琥珀、陶瓷等称绝缘体。而把导电性比较好的金属如金、银、铜、铁、锡、铝等称为导体。)

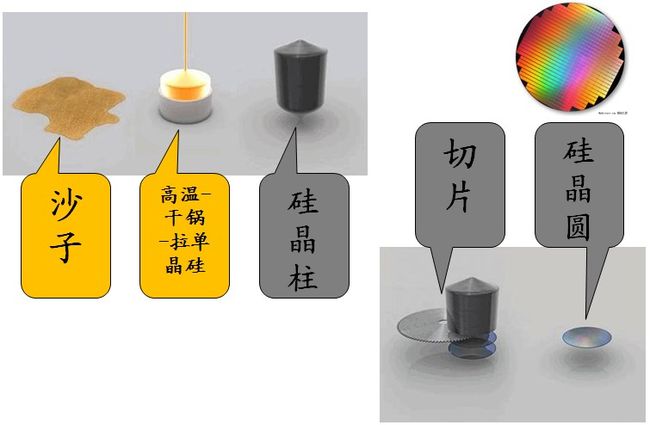

硅晶圆:晶圆便是硅元素加以纯化(99.999%),接着是将这些纯硅制成长硅晶棒,成为制造积体电路的石英半导体的材料,经过照相制版,研磨,抛光,切片等程序,将多晶硅融解拉出单晶硅晶棒,然后切割成一片一片薄薄的晶圆。硅晶圆的直径越大,代表著这座晶圆厂有较好的技术。

硅晶圆指 硅半导体电路制作所用的硅晶片。

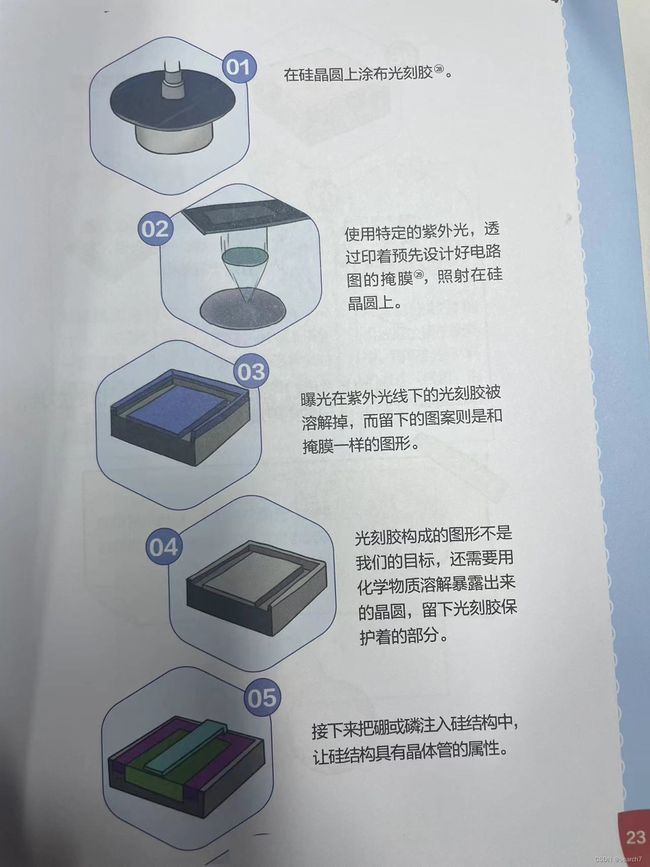

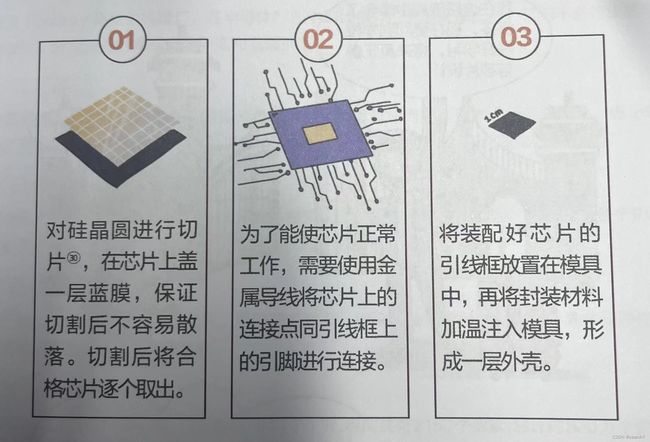

芯片制造流程:

漫画来自 华为麒麟著《看懂芯片原来这么简单》

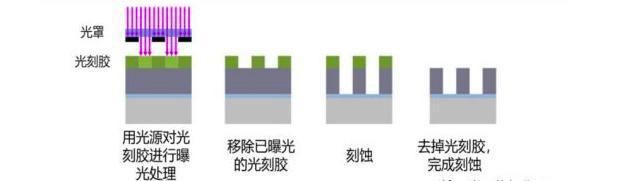

硅晶圆 + 掩膜(电路图)+ 光刻胶 ——> 有电路图的晶圆

有电路图的晶圆 + 硼/磷 ——> 各类晶体管

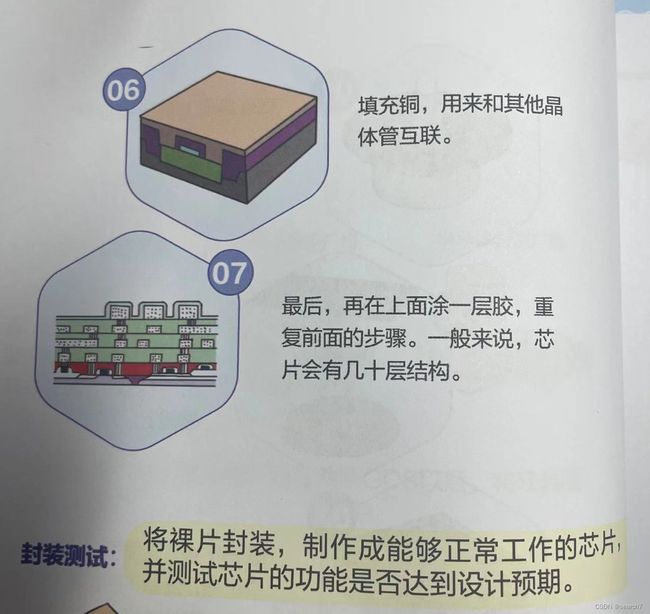

各类晶体管 + 铜 + 涂胶——> 晶体管互联起来

重复以上N次,芯片有几十层结构。

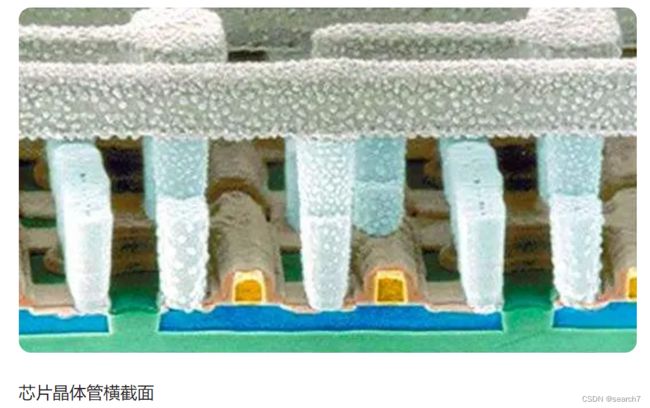

其它一些图片:

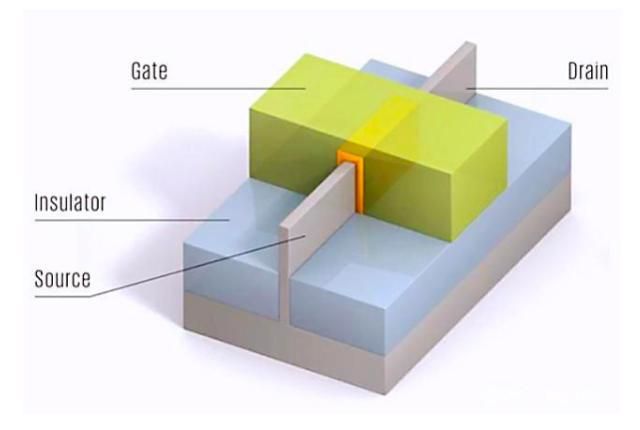

芯片制造的两个趋势,一个是晶圆越来越大,这样就可以切割出更多的芯片,节省效率,另外就一个就是芯片制程,制程这个概念,其实就是栅极的大小,也可以称为栅长,在晶体管结构中,电流从Source流入Drain,栅极(Gate)相当于闸门,主要负责控制两端源极和漏级的通断。电流会损耗,而栅极的宽度则决定了电流通过时的损耗,表现出来就是手机常见的发热和功耗,宽度越窄,功耗越低。而栅极的最小宽度(栅长),也就是制程。缩小纳米制程的用意,就是可以在更小的芯片中塞入更多的电晶体,让芯片不会因技术提升而变得更大。

但是我们如果将栅极变更小,源极和漏极之间流过的电流就会越快,工艺难度会更大。

晶体管越多就可以增加处理器的运算效率;再者,减少体积也可以降低耗电量;最后,芯片体积缩小后,更容易塞入行动装置中,满足未来轻薄化的需求。

到了3nm之后,目前的晶体管已经不再适用,目前,半导体行业正在研发nanosheet FET(GAA FET)和nanowire FET(MBCFET),它们被认为是当今finFET的前进之路。

三星押注的是GAA环绕栅极晶体管技术,台积电目前还没有公布其具体工艺细节。三星在2019年抢先公布了GAA环绕栅极晶体管,根据三星官方的说法,基于全新的GAA晶体管结构,三星通过使用纳米片设备制造出MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),该技术可以显著增强晶体管性能,取代FinFET晶体管技术。

1毫米=0.1厘米;1mm=0.1cml厘米=0.01dm分米=0.001m米=0.000001km千米=1 000μm微米=1 000 000nm纳米

发展:晶体管->芯片->集成电路->微电子技术

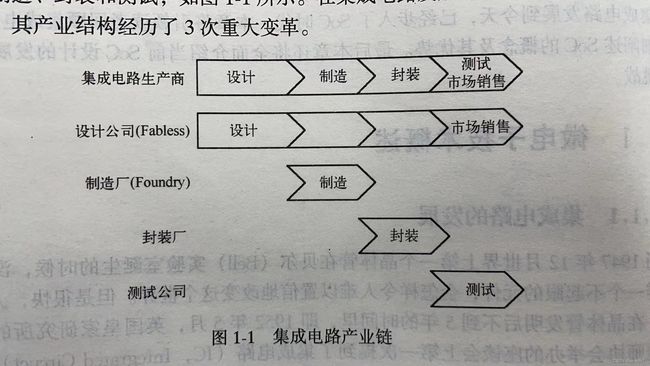

集成电路分工:

目前集成电路产业链主要包括设计、制造、封装、测试。

Foundry 是芯片代工厂的简称。Foundry 不搞设计,也没有自己的 IC产品,它为 Fabless提供完全意义上的代工,这使得 Fabless 可以放心地把产品交给 Foundry 而无须担心知识产权外流。

Fabless 是半导体集成电路行业中无生产线设计公司的简称。Fabless 开拓出市场后(或根据市场末来的需求进行风险投资后)进行产品设计,将设计的成果外包给 Foundry 厂家进行芯片生产,生产出来的芯片经过封装测试后由设计公司自己销售。

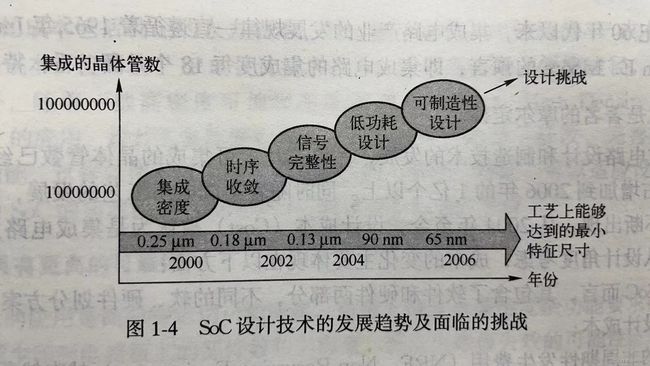

Soc设计的发展趋势:

集成密度:指芯片单位面积上所含的元件数,其朝着密度越来越高的方向发展,也意味着集成电路的规模越来越大,复杂性越来越高。随着科技的进步和人们生活需求的提高,整机系统不断地朝着多功能、 小体积方向发展,如手机、PDA、MP4 等消费类通信移动终端。这就要求系统中的芯片在满足功能需求的同时,体积能够尽可能的小。

不难发现,这一挑战来自两方面,即硅器件的复杂性和设计的复杂性。

硅器件的复杂性是指工艺上的最小特征尺寸缩小及新器件结构所带来的影响,以前可以忽视的现象现在对于设计的正确性存在着相当大的影响:

•对于器件而言,无法确定各 个参数理想的缩小比例(包括电源电压、國值电压等);

•尺寸缩小使得寄生电容、电感的影响无法忽略,对于制造工艺的可靠性造成一定的影响。

设计的复杂性主要体现在芯片验证和测试难度的提高,以及IP复用、混合电路设计的困难加大。

(1)芯片验证更为复杂

集成度越高,实现的功能越丰富,所需要的验证过程就越烦琐,验证向量的需求也就更多。目前,越来越多的设计厂商在设计复杂 SoC芯片的时候采 用基于 IP 核复用的方法,就IP核功能而言,有处理器核、DSP 核、多媒体专用处理核等,就电路类型而言,有数字逻辑核、存储器核、模拟 /混合核等。IP核的多样性造成了验证的复杂性。

(IP是构成SoC的基本单元,IP可以理解为满足特定规范,并能在设计中复用的功能模块,又称IP核)

(2)芯片测试更为复杂

集成密度的提高同样给芯片测试带来了困难。芯片规模的增大,往往会导致外围引脚的增加,并且内部逻辑越来越复杂,会生成海量的测试矢量。这就对芯片测试设备提出了更高的要求。ATE (Automatic Test Equipment)所能提供的测试通道深度和测试时间都是“稀缺资源”,随着集成度不断提高,测试日渐成为复杂 SoC 设计流程中的瓶颈。

(3)混合电路设计更为复杂

SoC 集成密度提高的另外一个挑战是数字电路和模拟电路的混合设计。在目前的技术水平下,典型的 SoC 有数十个系统单元组成,而且数量在未来可能增加到上百个。整个系统包括数字部分和模拟部分,其中,数字部分主要由处理器,存储器、外围接口组成,模拟部分包含了射频电路及模数、数模转换电路。模拟电路不像数字电路,受外界因素的影响较明显,集成度也远低于数字电路。要在高密度下实现数字电路和模找电路的集成及信号交互,就必须重新考虑设计方法、设计工具、制造封装方法等因素。

时序收敛:一般指前端和后端设计时序能够达到设计需求。

时序收敛的目的是满足设计的时序要求,让(FPGA )硬件design 按预设的逻辑正常的工作。

1. 什么是时序,时间顺序,有先有后,不能错乱。时序收敛就指的是某一系统电路能按既定的顺序来执行特定功能。

2. 系统内不同单元电路的处理速度和走线延迟等是造成时序无法收敛的因素。

设计工具的时序准确性不足,版图设计后的时序收敛问题,是两大关键障碍。

信号完整性:指一个信号在电路中产生正确响应的能力。

良好的完整性,指在需要的时间段,该信号产生一定的电压值。

soc设计中,信号之间的耦合作用会影响信号的完整性,若信号之间产生串扰,可靠性、可制造性、系统性能会降低。

随着工艺技术的发展,金属布线层数持线增加,从0.35 微米工艺的4层或者5层增加到0.13 微米工艺中的超过7层的金属布线层。随着布线层数的增加,相邻金属层的沟道电容也会增加。另外,目前复杂设计中的电路门数的剧增使得更多、更长的互连线成为必要。长的互连线不仅使得耦合电容会增加,长线上的电阻也会增加。而越来越细的金属线同样也会导致电阻的增加,这是因为互连线的横断面减小的缘故。即使采用现有的铜线互连工艺也并不能解决这方面的问题。

低功耗设计:SoC的低功耗设计已成为重大挑战之一,在特定领域,功耗指标甚至成为第一大要素。

近年来,随着IC 工作频率、集成度、复杂度的不断提高,IC 的功耗快速增加。由此带来了一系列的现实问题及设计挑战:

1、功耗增加引起的 IC运行温度上升会引起半导体电路的运行参数漂移,影响 IC 的正常工作,即降低了电路的可靠性和性能;

2、功耗增加引起的 IC运行温度上升会缩短芯片寿命,而且对系统冷却的要求也相应提高,不仅增加了系统成本,而且限制了 系统性能的进一步提高,尤其是对现在流行的移动计算;

3、为了进行低功耗设计,选择了不同性能参数的器件,如多阈值电压的 MOS 管、不同电源电压的器件,这样一来大大增加了设计复杂度。

可制造性设计及成品率:过去,成品率完全取决于代工厂的制造工艺水平,而现在更多的依赖于设计本身的特征。在65nm 及以下的工艺,可制造性设计尤为重要。

从总体看,可制造性设计、低功耗设计、信号完整性,为设计优化的主要任务。

SoC设计:

SoC的设计应该是一个软件、硬件协同设计的过程,这也是 SoC 系统一个非常重要的标志。

传统的集成电路设计方法一般都是将系统设计分为两个阶段:系统级软件开发阶段、电路级硬件设计阶段。需要特别指出的是,软件开发和硬件设计往往是相对独立进行的。

在系统级,软件开发人员使用如 C/C++ 等的高级编程语言进行系统描述和算法仿真,并分析系统在软件层面的各项指标,撰写系统设计书,然后移交给硬件设计工程师。

在电路级,硬件设计师首先要花大量的时间理解系统设计书,之后才能利用 VHDL或 Verilog 硬件描述语言进行电路设计。在此手工转换的过程中,可能还会引入人为的错误因素。另外,为了验证软件开发的正确性,必须等到硬件全部完成之后才能开始进行软件测试和系统集成,大大延长了设计的进程。传统的设计方法使得在软件和硬件之间很难进行早期的平衡和优化,并有可能严重影响开发成本和开发周期。

根据有关统计从系统级设计到电路级设计所花费的时间一般是系统级设计所花时间的 3 倍左右。因此在系统级设计与电路级设计之问架设一座桥梁,提高设计效率,保证设计成功,己经成为集成电路设计领域极为迫切的任务。