system verilog基础知识总结与复习(数组、队列、数据结构)

本文章大多以提问的形式给出问题,并尝试解答,主要目的是为了帮助自己复习sv基础知识,不足之处还请指正,以便共同学习!

一、数组、队列、数据结构

1.sv新增的数据类型logic,与wire,reg相比它有什么特点?

wire: 表示物理器件之间的连线,不存储值,常用于assign引导的连续赋值语句。

reg:表示存储结构,可以短暂存储数据直到下一个变化的值到来,常用于always表示的时序逻辑里面。(如果用always(*)的方式来表示组合逻辑,也需要用reg)。

logic:logic是SV中新引进的,它出了可用于reg表示的寄存器变量之外,还可像wire一样被连续赋值(可以说是对wire和reg的综合改进,更加偏向于软件环境构建),一般情况下logic可以取代reg和wire的大多数使用场景。但需要注意,logic不能有多个驱动。

2.区分四值逻辑二值逻辑有符号数以及无符号数。

二值逻辑:bit,int,byte,longint(默认返回0)

四值逻辑:logic,wire,net_type(如wire)(默认返回X)

有符号数:byte,int

无符号数:bit,logic,reg,net_type

3.定宽数组以及多维数组的表示?

定宽数组: int din[16] / int din[0:15] -----16个整数

多维数组:int dout[4][8] / int dout[0:3][0:7] dout[3][7] = 1(设置最后一个元素为1)

4.数组的基本操作? 赋值、比较等

数组的基本赋值 如 int din[6] = `{1,2,3,4,5,6}

数组支持直接比较 int d1[5]=`{1,2,3,4,5};

int d2[5]=`{5,4,3,2,1};

if( d1==d2) $display("d1==d2");

else $display("d1!=d2");

至于这里赋值时转译符号的添加,自己目前是认为如果存储是不连续的,则需要加转译符号,如果存储是连续的(如队列,合并数组等),则赋值的时候不需要加转译符号。如有更好的解释和理解方法,欢迎指导。

5.合并数组与非合并数组的区别?

合并数组 bit [3:0][7:0] din_a 必需完整申明数组大小

非合并数组 bit [7:0] din_b[4]

din_a中数据的存储是连续的,使用了一个32比特的字节。

din_b中的数据存储不是连续的,使用了4个32比特字节,每个字节的高24比特都没有被使用。

合并数组的存放方式:

![]() 非合并数组的存放方式:

非合并数组的存放方式:

![]()

![]()

![]()

![]()

6.动态数组,队列的初始化,赋值以及区别?

动态数组:其数组大小在申明时可以不确定,在程序运行时才肯定具体的大小。动态数组使用需要new[]来分配空间。

队列:在使用过程中可随意增加减少元素个数,队列不需要new。

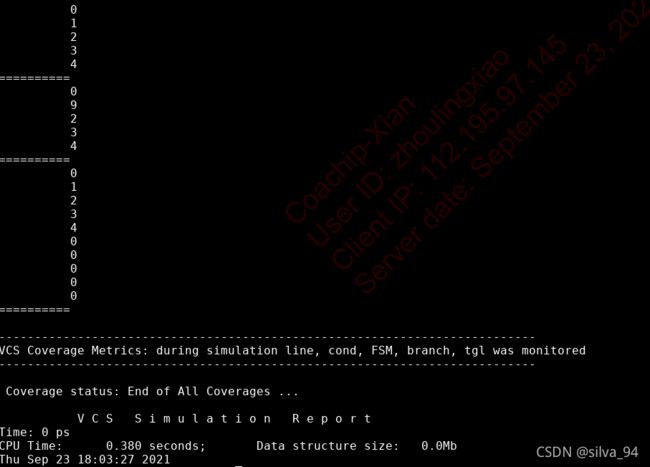

动态数组的基本操作以及仿真结果:

队列的基本操作以及仿真结果:

队列有什么优势?

答:队列集成了数组和链表的优点,首先它与链表相似,可以在任意位置增加或删除元素。其次,它可以像数组一样通过索引实现对任一元素的访问,而不需要像链表一样遍历所有元素。

7.压缩结构体与联合结构体的区别?

struct通常与typedef连用连创建新的数据类型,联合结构体(union)的特点通过下段代码来展示。

由仿真结果可以看出,联合结构体中的成员变量pixel_rgb_t和pixel_yuv_t总位宽需要相等 ,如果不相等会报以下错误:

同时在联合结构体中对成员变量pixel_rgb_t中r,g,b进行重新赋值,相应成员变量pixel_yuv_t中的y,u,v的值也会发生变化,说明rgb与yuv只是解析方式不同(可理解为联合结构体公用内存)。