第1章:计算机组成原理与体系结构

考点1 数据的表示(★★★★)

考点1.1 进制的转换

【考法分析】

本考点的基本考法是与内存地址计算 IP地址计算结合考查。

【要点分析】

1 十进制转R进制(短除法);

2 R进制转十进制(按权展开法);

3 二进制转八进制 转十六进制(分组快速转换)。

【备考点拨】

- 掌握二进制数与十进制数的互转,熟练计算IP地址转换;

- 掌握二进制与十六进制的互转,熟练掌握内存地址转换。

考点1.2 原码/反码/补码/移码表示

【考法分析】

本考点的主要查考方式有:给定一些描述,让考生判断是否正确;计算某种码制的表示范围或表示数值的个数;不同码制的表示。

【要点分析】

1 原码/反码/补码/移码的转换规则;

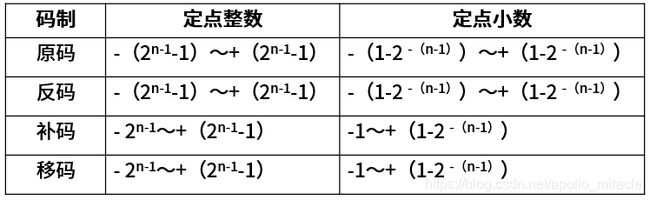

2 原码/反码/补码/移码的表示范围和表示个数(如下图所示):

【注:对于原码和反码,存在+0和-0两种表示0的方式,对于补码和移码存在人为定义-0的补码为其-2n-1的补码,以n=0为例,人为定义10000000是-128的补码】

3 对于0的特殊化:0在原码和反码中有+0和-0两种表示方式,而对于补码和移码其表示方式一致。

【备考点拨】

- 掌握原码/反码/补码/移码的准换;

- 掌握原码/反码/补码/移码的表示范围和能够表示数的个数;

- 注意在补码和移码中-0的特殊性和人为定义。

考点1.3 浮点数的表示

【考法分析】

本知识点的考查方式为:给定一些描述(关于浮点数构成 浮点数运算规则等)让学员判断是否正确;判断尾数和解码对浮点数的影响。

【要点分析】

1 浮点数各部分表示意义:N = 尾数*基数指数

(1)一般尾数用补码,阶码用移码;

(2)阶码的位数决定数的表示范围,位数越多范围越大;

(3)尾数的位数决定数的有效精度,位数越多精度越高。

2 浮点数运算规则:对阶 > 尾数计算 > 结果格式化

(1)对阶时,小数向大数看齐;

(2)对阶是通过较小数的尾数右移实现的。

【备考点拨】

1 掌握浮点数各部分的意义,重点掌握阶码 尾数的意义;

2 掌握浮点数运算的过程和简单规则。

考点2 运算器与控制器(★★★★)

【考法分析】

本考点主要的考查形式有:给定部件判断部件所属运算器或控制器;给定一定功能描述,判断具体描述的部件。

【要点分析】

1 运算器:

①算术逻辑单元ALU:数据的算术运算和逻辑运算

②累加寄存器AC:通用寄存器,为ALU提供一个工作区,用在暂存数据

③数据缓冲寄存器DR:写内存时,暂存指令或数据

④状态条件寄存器PSW:存状态标志与控制标志(争议:也有将其归为控制器的)

2 控制器:

①程序计数器PC:存储下一条要执行指令的地址

②指令寄存器IR:存储即将执行的指令

③指令译码器ID:对指令中的操作码字段进行分析解释

④时序部件:提供时序控制信号

【备考点拨】

1 掌握运算器 控制器分类所属的部件,并熟悉各个部件的功能和特点能够加以区分。

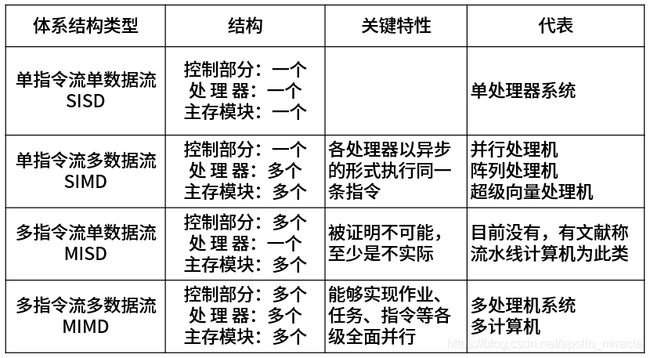

考点3 Flynn分类法(★★)

【考法分析】

本题考查形式主要是根据题干描述判断所属分类或判断各个分类的典型系统。

【要点分析】

【备考点拨】

1 掌握Flynn分类法四种类型的特点及其相关典型系统

2 常考典型系统:阵列处理机 超级向量处理机;常考类型:SIMD MISD

考点4 CISC与RISC(★★)

【考法分析】

本考点的基本考法是给出一些CISC与RISC的特点,让考生判断说法的正确性。

【要点分析】

1 CISC:复杂指令集;RISC:精简指令集。

2 CISC的特点:指令数量多,指令频率差别大,多寻址,使用微码。

3 RISC的特点:指令数量少,操作寄存器,单周期,少寻址,多通用寄存器,硬布线逻辑控制,适用于流水线。

【备考点拨】

熟记CISC与RISC特点差异。

考点5 流水线技术(★★★★)

【考法分析】

本考点涉及的考查形式有:

(1)流水线相关理论概念;

(2)流水线相关计算。

【要点分析】

流水线相关概念:

(1)流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理是针对不同指令而言的,它们可同时为多条指令的不同部分进行工作,以提高各部件的利用率和指令的平均执行速度。

(2)流水线建立时间:1条指令执行时间。

(3)流水线周期:执行时间最长的一段

2 流水线相关计算:

(1)流水线执行时间(理论公式):(t1+t2+..+tk)+(n-1)*∆t

(2)流水线执行时间(实践公式):k*∆t +(n-1)*∆t

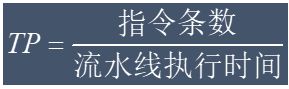

(3)流水线吞吐率:

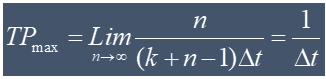

(4)流水线最大吞吐率

(5)流水线加速比:顺序执行时间/流水线执行时间

【备考点拨】

了解流水线相关理论概念;

2 掌握流水线相关计算公式。

考点6 存储系统(★★★★)

考点6.1 分级存储体系

【考法分析】

本考点主要考查的形式一般为判断相关概念描述的正确性,考查较为频繁的概念有局部性原理 各层次的速度比较 Cache的位置。

【要点分析】

(1)关于多级存储体系的分布;

(2)关于多级存储体系不同层次的大小 速度 成本等对比;

(3)关于多级存储体系的理论支持体系(局部性原理)。

【备考点拨】

掌握相关理论概念。

考点6.2 Cache

【考法分析】

一般以选择题形式考查,要求判断相关概念描述是否正确,Cache映射方式的对比区分,Cache映射方式的控制由硬件直接控制。

【要点分析】

1 Cache的相关概念:理论依据(局部性原理),大小 速度 成本等对比。

2 Cache映射方式:全相联 组相联 直接相联映像的对比(冲突率依次增高,电路复杂度依次降低)。

【备考点拨】

1 掌握Cache相关概念;

2 掌握Cache相联映象方式的对比。

考点6.4 内存

【考法分析】

本知识点的考查主要是对相关参数的计算:内存总容量 芯片单位容量 芯片片数。总片数=总容量/每片的容量。

【要点分析】

1 内存单元数计算:最大地址+1-最小地址

2 内存总容量:按字节编址,内存单元数*8bit;按字编址,内存单元数*机器字长。

3 已知芯片单位容量,求所用芯片的片数,总容量/单位容量;

4 已知所用芯片的片数,求取芯片单位容量,总容量/芯片片数。

【备考点拨】

1 掌握相关计算,注意结合二进制与十六进制 十进制之间的相互转化,注意编址方式的选择会影响内存总容量。

考点7 总线系统(★)

【考法分析】

本知识点考查形式主要是判断总线的分类。

【要点分析】

1 数据总线(Data Bus):在CPU与RAM之间来回传送需要处理或是需要储存的数据。

2 地址总线(Address Bus):用来指定在RAM(Random Access Memory)之中储存的数据的地址。

3 控制总线(Control Bus):将微处理器控制单元(Control Unit)的信号,传送到周边设备,一般常见的为 USB Bus和1394 Bus。

【备考点拨】

1 掌握总线的分类,能够区分数据总线 控制总线 地址总线的区别。

考点8 可靠性(★)

【考法分析】

本知识点主要考察关于不同系统类型的可靠性计算。

【要点分析】

1 串联系统计算:R总=R1*R2;

2 并联系统计算:R总=1-(1-R)2;

3 N模混联系统:先将整个系统划分为多个部分串联R1 R2…等,再计算R1 R2内部的并联可靠性,带入原公式。

【备考点拨】

1 掌握可靠性的计算。

考点9 校验码(★★★)

【考法分析】

本考点主要考查形式有:给定校验码相关基本概念,判断正误;区分不同校验方式的特点;对于海明校验码的计算问题,包括校验码的位数计算,校验码的位置计算。

【要点分析】

1 奇偶校验:掌握校验原则等相关概念,只检奇数位错,不能纠错。

2 循环校验码CRC:可查错,不可纠错,运用模二除法计算校验码。

3 海明校验:要求掌握相关概念,可查错,可纠错;要求掌握海明校验码校验位计算:2r>=r+m-1。

【备考点拨】

1 掌握奇偶校验的规则,掌握其特性;

2 了解CRC校验的规则,了解模二除法,掌握其特性;

3 掌握海明校验的规则,重点掌握其校验位计算公式2r>=r+m-1。了解其编码过程。