【软考-软件设计师精华知识点笔记】第一章 计算机网络概论

前言

由于笔记复制到CSDN样式失效,没有精力再重新完整的检查并设置一遍样式,有积分的可以前往下载word、pdf、有道云笔记版本。

需要说明的是,下载的内容与本篇分享内容一致,只有样式的区别【比如重点记忆、常考内容有颜色、字号、自重等样式,目录结构更完善,表格不是图片,等】

下载地址:

https://download.csdn.net/download/chengsw1993/85491609

如果发现文章存在读不通、显示异常等内容,请评论区告知以便修改,应该都是CSDN的markdown语法导致的。

系列文章

上一篇:【软考-软件设计师精华知识点笔记】考试大纲及题型介绍

下一篇:【软考-软件设计师精华知识点笔记】第二章 程序设计语言基础知识

计算机硬件组成

运算器、控制器、存储设备、输入设备、输出设备

存储器:内部存储器(内存,存储临时数据)、外部存储器(硬盘、固态、光盘,长期存储数据)

输入设备、输出设备合称 外部设备

主机: CPU + 主存储器

中央处理单元CPU

组成:运算器、控制器、寄存器组、内部总线

功能:程序控制、操作控制、时间控制、数据处理等

运算器组成:算术逻辑单元ALU、累加计算器AC【简称累加器,源操作数和结果暂存在此】、数据缓冲寄存器DR、状态条件寄存器PSW

运算器功能:算术运算、逻辑运算及逻辑测试

控制器组成(最重要部件):指令寄存器IR Instruction Register【暂存CPU指令】、程序计数器PC Program Counter【存储指令的地址】、地址寄存器AR Address Register【CPU访问的内存地址】、指令译码器ID Instruction Decoder【分析指令操作码】

控制器功能:控制整个CPU的工作,最为重要,包括程序控制、时序控制等

进制转换

二进制BIN,0b

八进制OCT,7O

十进制DEC,9

十六进制0x或H, 0x18F 18FH

X进制转10进制:

例如18FH,1*16^2+8*16^1+15*16^0=399

10进制转X进制:除X取余,余数倒数。200转八进制

M转N:先转到10进制

直接转换

二进制转八进制(2^3 = 8):每三位二进制可转为一位八进制,不够在前面补0。

01101b → 001 101 → 1*2^0 1*2^0+1*2^2 = 15(八进制)

二进制转16进制(2^4 = 16):

101101 → 0010 1101 → 1*2^1 + (1*2^0+1*2^2+1*2^3) = 2D

小数部分的转换:不考

数的表示

机器数:二进制 0 1,有符号,无符号

真值:机器数对应的实际数值

数的编码方式

带符号数:8位寄存器

原码:正常二进制表示,最高位表示符号位。0的源码:+0(0 0000000)、-0(1 0000000)

反码:正数的反码就是原码;负数的反码是在原码基础上,除符号位以外按位取反。0的反码:+0(0 0000000)、-0(1 1111111)

补码:正数的补码还是原码;负数的补码是在原码的基础上,除符号位以外,按位取反再加1,即反码+1,可能会出现进位。0的补码只有一种形式 +0(0 0000000)、-0(1 1111111 + 1 →10 0000000→9位,溢出,存不进去,还是 0 0000000)

移码:用作浮点运算的阶码,无论正负数,原码的补码的首位(符号位)取反

±0的补码和移码相同

浮点数

N = F * 2^E,E阶码(带符号纯整数),F尾数(带符号纯小数)

阶符 阶码 数符 尾数

数值范围由阶码确定,数值精度由尾数确定

尾数采用规格化方法

浮点数的运算:

- 对阶,使两数阶码相同,小阶看齐大阶,尾数右移

- 尾数计算

- 结果规格化,转换成1.0xxx或者0.1xxx

算术运算和逻辑运算

逻辑与 &

逻辑或 |

亦或⊕:相同为0,不同为1

逻辑非

左移<<:二级制数整体左移n位,高位若溢出则舍去,低位补0

右移>>:二级制数整体右移n位,低位若溢出则舍去,高位补0

校验码

码距:A码转换到B码‘需要改变的位数。例如00到11,需要改变两位,则码距为2。一般而言,码距越大,越利于纠错和检错。

奇偶校验码:在编码中增加1位校验位使编码中1的个数为奇数(奇校验)或者偶数(偶校验)。缺陷:只能检测到1位错,且无法纠错(01101 | 0 -> 00111 | 0都是3个1,检测不出来)

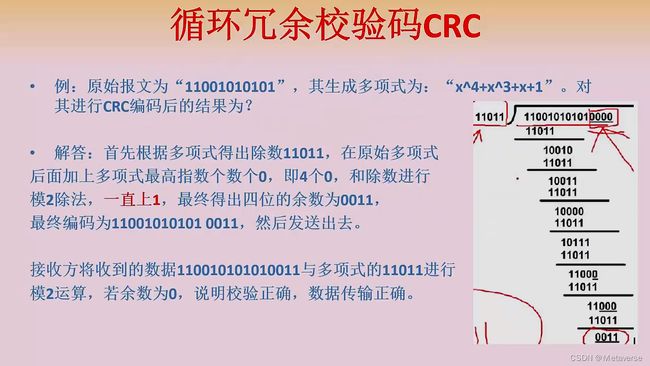

循环冗余校验码CRC:能检错不能纠错

x^4+x^3+0*x^2+x^1+x^0 → 11011

在原始报文后加(多项式位数-1)位的0,因此+4个0

从原报文第一位开始,每次用多项式进行模2除法运算,相同为0,不同为1,不产生借位。每次结果舍弃最高位的0,再补够多项式的位数,一直减到最后一位,得出的结果加在原报文后面,整体就是最终编码。

由于不能除尽的数已经被计算出来了,所以发送的数据一定能被多项式除尽。能除尽表示正确。

海明校验码:利用奇偶性来检错和纠错。数据n位,校验位k位:2^k -1>=n+k。

计算机体系结构

S:simple I:instructions D:data M:multiple

多指令:多个控制部分

多数据:多个处理器处理

存储模块,控制部分、处理器有一个多个,它就多个

计算机指令

组成:操作码(要完成的操作)+操作数/地址码(参与运算的数据及所在地址)。整条指令以二进制编码形式存在存储器中。

计算机指令执行过程:取指令–分析指令–执行指令。首先将程序计数器PC中的指令地址取出,送入地址总线,CPU依据指令地址去内存中取出指令内容存入指令寄存器IR;而后由指令译码器ID进行分析,分析指令操作码;最后执行指令,取出指令执行所需的源操作数。

控制器组成(最重要部件):指令寄存器IR Instruction Register【暂存CPU指令】、程序计数器PC Program

Counter【存储指令的地址】、地址寄存器AR Address Register【CPU访问的内存地址】、指令译码器ID

Instruction Decoder【分析指令操作码】

指令寻址方式(执行方式)

指令寻址方式

- 顺序寻址:

- 跳跃寻址:jump

指令操作数的寻址方式

- 立即寻址方式:指令的地址码字段指出的不是地址,而是操作数本身

- 直接寻址方式:指令的地址码字段直接指出操作数在主存中的地址

- 间接寻址方式:指令的地址码字段所指向的存储单元中存储的是操作数的地址

- 寄存器寻址方式:指令中的地址码是寄存器编号

- …

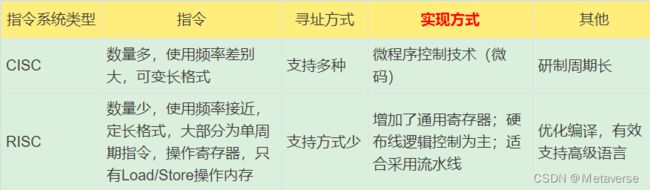

★指令系统

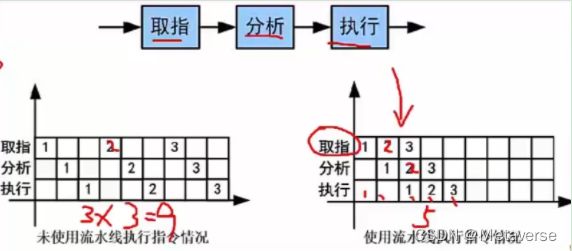

指令流水线

原理:将指令分成不同段,每段由不同的部分去处理,因此可以产生叠加的效果,所有的部件去处理指令的不同段

★流水线相关计算

流水线周期:指令分成不同的执行段,其中执行时间最长的段为流水线周期。

流水线执行时间:1条指令总执行时间+(总指令条数 -1)*流水线周期。

流水线吞吐率:总指令条数/流水线执行时间。

流水线加速比:不使用流水线总执行时间/使用流水线总执行时间。

超标量流水线技术

存储系统

层次结构:

CPU内部通用寄存器

Cache

主存储器(内存)

联机磁盘存储器(外存)(硬盘、固态等)

脱机光盘、磁盘存储器(U盘、光盘等)

从上到下:速度↓价格↓容量↑

计算机采用分级存储体系的目的是为了解决存储容量、成本和速度之间的矛盾问题。

两级存储:Cache-主存、主存-外存

局部性原理:在CPU运行时,所访问的数据会趋向于一个较小的局部空间地址内,包括以下两个方面:

- 时间局部性原理:在相邻的时间里会访问同一个数据项。(例如循环体)

- 空间局部性原理:在相邻的空间地址会被连续访问。(例如数组、列表等数据结构)

使用Cache改善系统性能的依据是程序的局部性原理

高速缓存Cache

高速缓存Cache用于存储当前最活跃的程序和数据,直接与CPU交互,位于CPU和主存(即内存)之间,容量小,速度是内存的5-10倍,由半导体材料构成。其内容是主存内容的副本拷贝,对于程序员来说是透明的。

Cache由控制部分和存储器组成,存储器存储数据,控制部分判断CPU要访问的数据在不在Cache中,在则命中,不在则根据一定的算法从主存中替换。

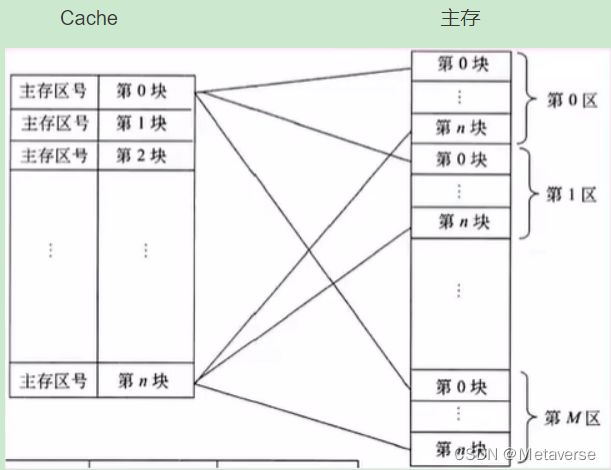

地址映射:在CPU工作时,送出的是主存的单元地址,而读写操作应在Cache存储器中。这就需要将主存单元地址转换为Cache存储器地址,称为地址映射,由硬件自动完成,分为3类:

-

直接映射:地址变换简单但不灵活,容易资源浪费。例如第0块已经映射到Cache中,主存其他第0块映射都会被阻塞,因此最容易发生块冲突

-

全相联映射:主存中任一块都与Cache任一块对应,因此可以随意调入Cache任何位置,但地址变换复杂,速度较慢。因为主存可以调入Cache任一块,只有Cache满了之后才会发生块冲突,因此是最不容易发生块冲突的映射方式。

-

组相联映射:上面两者组合

Cache地址映射的块冲突概率:直接映射 > 组相联映射 > 全相联映射

Cache命中率

当CPU所访问的数据在Cache中,称为Cache命中,从Cache中读取数据,否则在主存中读取数据。

程序中大部分指令是:顺序存储、顺序执行

主存编址

通过以下例题讲解:

例题:(2013年上半年真题)地址编号从80000H到BFFFFH且按字节编址的内存容量为(5 )KB,若用16K*4bit的存储器芯片构成该内存,共需( 6 )片。

解析:

1Byte字节 = 8bit位

K:1024 k:1000

内存单元个数 = 地址编号大 - 小 + 1 = (BFFFFH - 80000H + 1)= 40000H

2^10 = 1024

内存容量 = 内存单元个数 * 每个内存单元的大小 = 40000H * 1B = 40000H个字节 = 4*16^4个字节 = 4* (2^4)^4 = 2^18B = 2^8KB = 256KB

16K*4bit = 8K * 8b = 8KB

256KB / 8KB = 32块

总线结构

从广义上讲,任何连接两个以上电子元器件的导线都可以称为总线,通常分为三类:

- 内部总线:内部芯片级别的总线,芯片与处理器之间通信的总线

- 系统总线:是板级总线,用于计算机内各部分之间的连接,具体分为 数据总线(并行数据传输位数)、地址总线(系统可管理的内存空间的大小,x86 2^32=4G,x64 2^64)、控制总线(传输控制命令)。代表的有ISA总线、EISA总线、PCI总线

- 外部总线:设备一级的总线,微机和外部设备的总线。代表的有RS232(串行总线)、SCSI(并行总线)、USB(通用串行总线,即插即用,支持热插拔)

半双工总线:同一时刻只能由一个方向上传输信息

全双工总线:同一时刻可以在两个方向上传输信息

系统可靠性分析

平均无故障时间 MTTF = 1 / 失效率

平均故障修复时间 MTTR = 1 / 修复率

平均故障间隔时间 MTBF = MTTF + MTTR

系统可用性 = MTTF / (MTTF + MTTR) * 100%

串联系统:一个设备不可靠,整个系统崩溃 R = R1 * R2 * R3 * … * Rn

并联系统:所有设备都不可靠,系统才会崩溃,因此需要用不可靠率计算 R = 1 - (1-R1)(1-R2)(1-R3)* … * (1-Rn)

混合系统:划分串并联再计算

网络安全概述

五大基本要素:

- 保密性:不暴露给未授权者(包括最小授权原则、防暴露、信息加密、物理保密)

- 完整性:保证数据传输过程中无误,接收和发送数据相同,包括安全协议、校验码、密码校验、数字签名、公证等手段

- 可用性:保证合法的用户能以合法手段来访问数据,包括综合保障(IP过滤、业务流控制、路由选择控制、审计跟踪)

- 可控性:整个网络处于可控状态

- 不可抵赖性:保证参与者无法抵赖

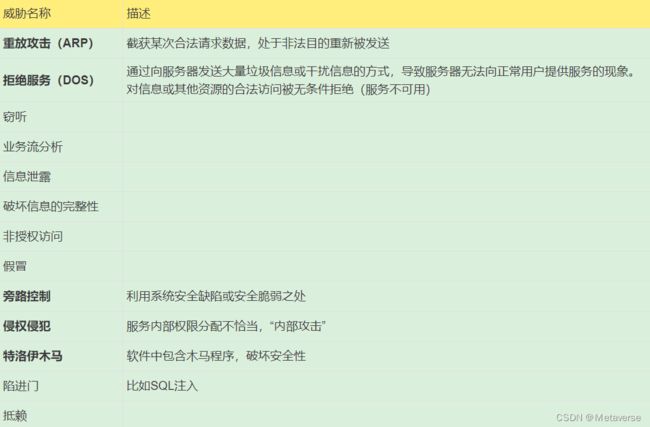

安全威胁分类:

加密技术-保密性

明文

密文

加密

解密

加密算法:一般是公开的,包括两大原则:代换(转换为其他数据)、置换(打乱明文顺序)

密钥

对称加密技术:

加解密密钥相同,也称为共享密钥加密技术,属于不公开密钥加密。

缺点:安全性不够高(只有一个密钥),且密钥分发困难(密钥需要传输给接收方,安全保密问题)

优点:加密速度快,非常适合大数据量的加密

常见对称加密算法:

DES:替换+移位、56位密钥、64位数据块、速度快、密钥易产生

3DES(3重DES):两个56位密钥K1、K2

加密:K1加密 → K2解密 → K1加密

解密:K1解密 → K2加密 → K1解密

AES:用于替换AES,要求是“至少与3DES一样安全”

RC:RC4、RC5

IDEA算法:128位密钥、64位数据块、比DES的加密性好、对计算机性能要求相对低,PGP(优良保密协议)

非对称加密技术:

又称为公开密钥技术,密钥有一对:公钥、私钥,公钥是公开的,私钥只有自己知道,公钥加密、私钥解密

优点:公钥公开不用担心密钥传输的安全问题

缺点:密钥多、计算量大,不适合加密大数据量

常见非对称加密算法:即 公开密钥加密算法

RSA:512/1024位密钥,计算量极大,难破解

Elgamal:其基础是Diffie-Hellman密钥交换算法

ECC:椭圆曲线算法

背包算法

Rabin

D-H

DSA:512/1024位密钥

信息摘要-完整性

消息认证

将数据通过哈希函数生成一段特征信息

信息摘要特点:不管数据多长,产生的摘要信息长度不变;输入数据一旦变更,计算出的信息摘要一定会改变;单向性,只能通过数据产生信息摘要。

算法:MD5(产出128位)、SHA(安全散列算法,产出160位,安全性更高)

问题:由于算法都是公开的,如果原数据和信息摘要都被篡改,接收方就无能为力了。该问题通过数字签名技术解决。

数字签名-不可抵赖性

加密、信息摘要只能保证数据传输过程中的保密性和完整性

数字签名属于非对称加密体制,主要功能:不可否认、报文鉴别、报文的完整性

数字证书

数字证书又称为数字标识,由用户申请,证书签证机关CA对其核实签发的,对用户的公钥的认证。上述加解密、数字签名、信息摘要都是基于原发送方正确的前提下,如果发送方本身就是假的就无法校验了,这就需要数字证书来对发送方身份验证。

现在数字证书版本大多为X.509

原理:发送方向CA申请数字证书数字证书是经过CA数字签名的,也即CA使用私钥加密,接收方先下载CA的公钥,去验证数字证书的真伪。

数字证书格式:序列号、版本号、签名算法、发行者ID、发行者、主体ID、有效期、公钥

PKI公钥基础设施

PKI公钥基础设施是提供公钥加密和数字签名服务的系统或平台,目的是为了管理密钥和证书。一个机构通过采用PKI框架管理密钥和证书就可以建立一个安全的网络环境。

PKI主要包括四个部分:X.509格式的证书、CA操作协议、CA管理协议、CA政策制定

PKI的基础技术包括加密、数字签名、数据完整性机制、数字信封、双重数字签名等。

一个PKI应用系统至少包含以下部分:

- 公钥密码证书管理

- 黑名单的发布和管理

- 密钥的备份和恢复

- 自动更新密钥

- 自动管理历史密钥

- 支持交叉认证