【新手向】Verilog中 判断语句 的执行时序总结

一、时序逻辑

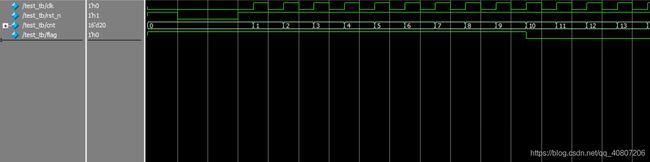

有两个触发器,一个作为计数器使寄存器cnt自加,另一个判断cnt的值并作出响应。

always块中的时序逻辑电路基本拓扑如下图所示,由两个触发器级联构成。

上述两个always块的过程都是在同步时钟下进行的时序逻辑电路。

由触发器的特性可知,在时序电路1中判断时序电路2的状态值,判断的永远是时序电路2的上一个时钟周期所对应的值。所以可以由此结论推断各判断语句对应的触发时间。

(cnt初始等于0,flag高电平表示事件触发,低电平表示未触发。)

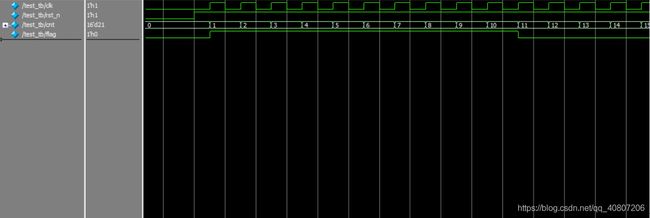

if(cnt==N)

由上述结论可以推得,当cnt的计数值等于N+1时才可以使判断cnt==N成立。即第N+1个脉冲时触发if下的事件。

if(cnt

由结论可推,当cnt的计数值计到N+1时,if条件才不满足。即前N个脉冲都触发,从第N+1个脉冲开始不触发。

if(cnt≤N)

由结论可推,当cnt的计数值计到N+2时,if条件才不满足。即前N+1个脉冲都触发,从第N+2个脉冲开始不触发。

if(cnt≥N)

由结论可推,当cnt的计数值计到N+1时,if条件才满足。即前N个脉冲不触发,从第N+1个脉冲开始才触发。

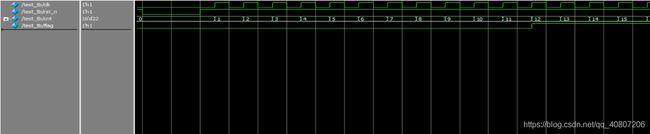

if(cnt>N)

由结论可推,当cnt的计数值计到N+2时,if条件才满足。即前N+1个脉冲不触发,从第N+2个脉冲开始才触发。

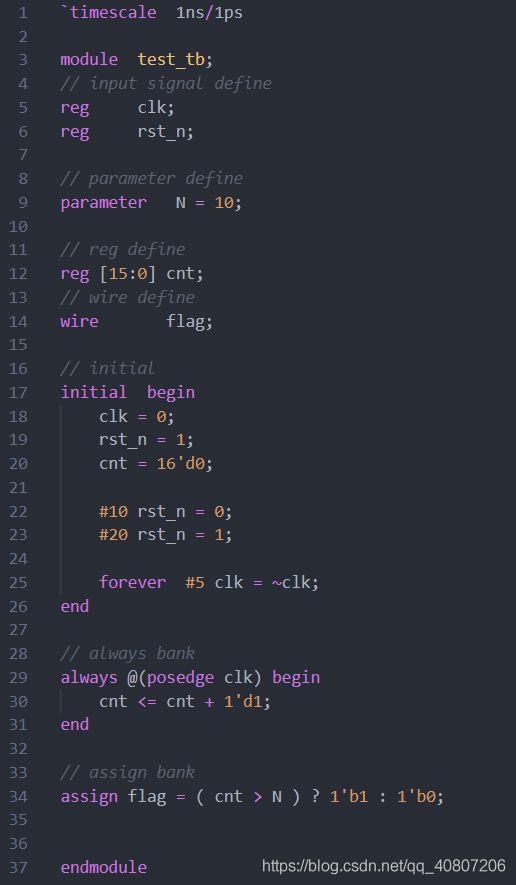

二、组合逻辑

用纯组合逻辑电路判断时序逻辑电路的状态值,本质上只有一个触发器,自然不会出现两个触发器级联所产生的判断延迟一周期的特性。

所以在组合逻辑中判断时序逻辑的状态值,所有触发时间减1,即向左提前一个周期。

(cnt==N)?

由上述结论可推得,第N个脉冲时触发assign下的事件。

(cnt

由上述结论可推得,前N-1个脉冲都触发,从第N个脉冲开始不触发。

(cnt≤N)?

由上述结论可推得,前N个脉冲都触发,从第N+1个脉冲开始不触发。

(cnt≥N)?

由上述结论可推得,前N-1个脉冲不触发,从第N个脉冲开始触发。

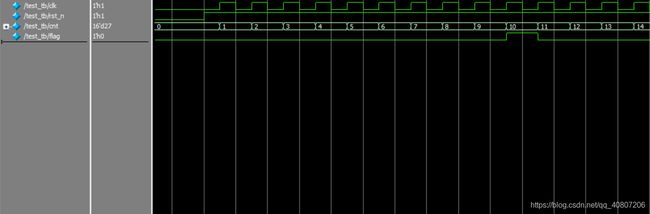

(cnt>N)?

由上述结论可推得,前N个脉冲不触发,从第N+1个脉冲开始触发。

新手写verilog时序时经常会不知道到底是用 N 还是 N-1 ,或者是用>还是≥、<还是≤。如果你想清楚上面这些判断情况,就可以游刃有余了。