硬件扫盲系列-接口

硬件扫盲系列-接口

- 1.前言

- 2. 概念

-

- 2.1 PCIE接口

- 2.2 HDMI接口

- 2.3 SATA接口

- 2.4 Serdes接口

- 2.5 LVDS接口

- 2.6 1553B接口

- 2.7 Spacewire接口

1.前言

一直很奇怪为何要弄那么多接口,那么多协议,看了一些文章,发现有些是历史继承性的问题,用久了,生态环境好,用户多,不是那么容易都转到一种来,另一方面会从应用场景,价格,速率等方面做折中考虑。

2. 概念

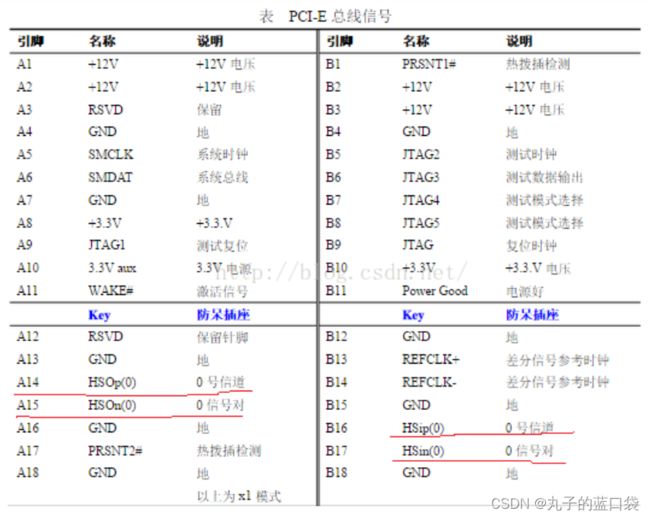

2.1 PCIE接口

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准。

PCI-E有 x1/x4/x8/x16等多种插槽模式。

信号的定义如下:

HSOP/N发送信号对

HSIP/N接收信号对

PCIe是从PCI发展过来的,PCIe的”e”是express的简称,快的意思。PCI使用并口传输数据,而PCIe使用的是串口传输。虽然串口传输,但是没有外部时钟,而用编码体现时钟,所以传的快。

目前PCIE版本已经发展到PCIE6.0。

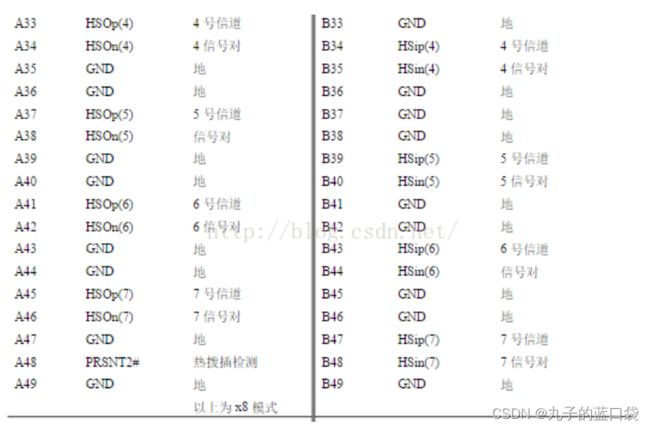

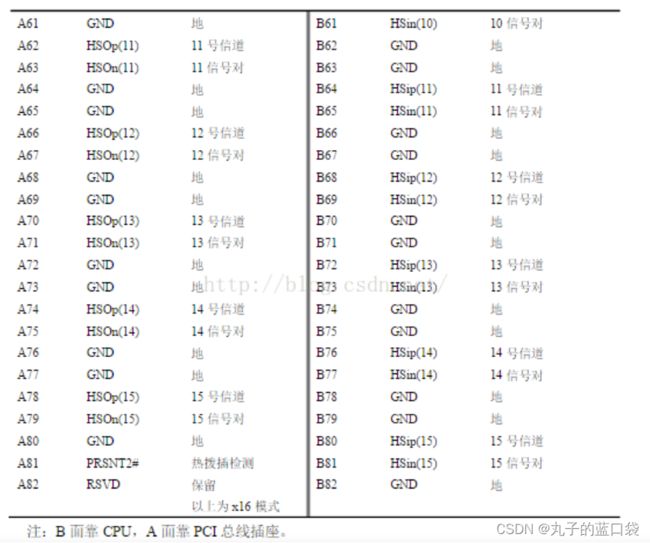

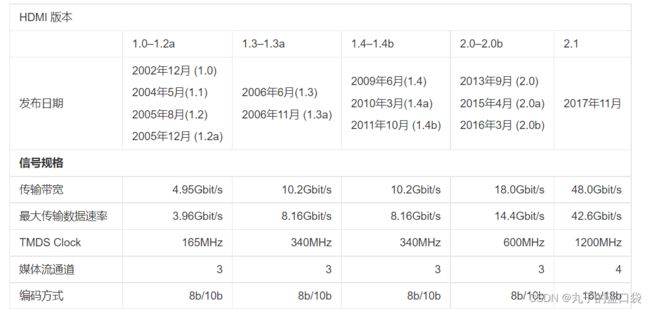

2.2 HDMI接口

HDMI英文全称High Definition Multimedia Interface,是一种数字化视频/音频接口技术,HDMI2.1最高数据传输速度为48Gbps。

HDMI不同版本对比如下表:

HDMI的传输距离一般在15米内。

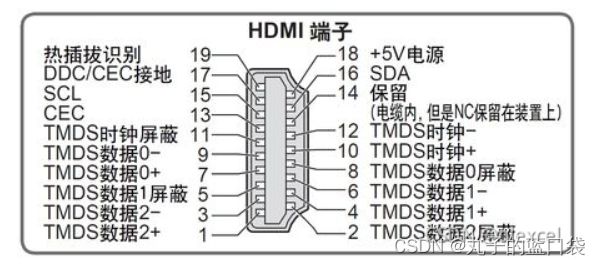

HDMI接口有A,B,C,D,E五种引脚类型,最常用的是A型。接口定义如下:

CEC(consumer electronic control)类似一种扩展的HDMI功能,它是一种专用控制总线,使设备能够自动控制其他连接的设备。

I2C引脚,用于DDC(Display Data Channel,主要用于EDID与HDCP的传输)传输。

EDID(Extended Display Identification Data)扩展显示标识数据

HDCP(High -bandwidth Digital Content Protection)高带宽数字内容保护技术

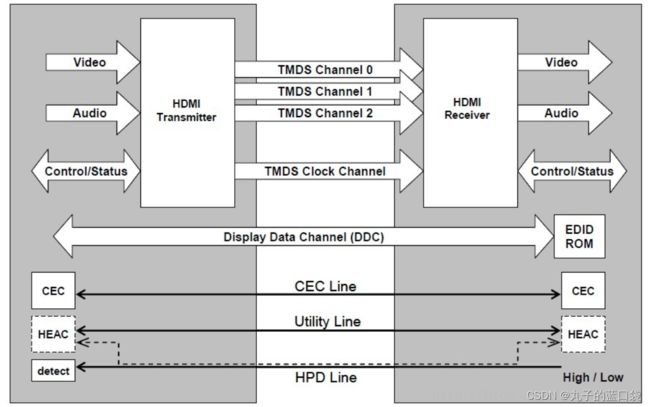

下图是传输示意图:

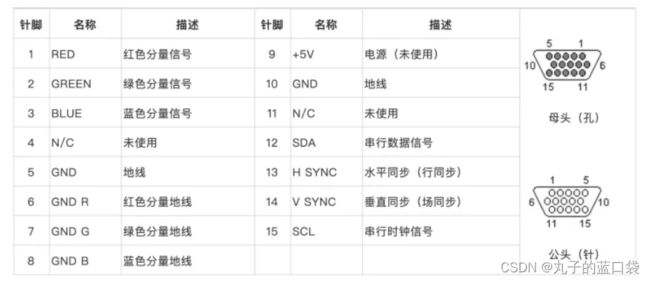

VGA(Video Graphics Array)接口,是模拟信号,只能传输视频信号。

VGA接口定义如下:

VGA接口与CPU进行通信时,需要使用DAC将数字信号转换为RGB模拟信号,和行、场同步信号,再输出到显示设备成像。

VGA与HDMI接口比较:

- HDMI接口是数字接口;VGA接口是模拟接口。

- HDMI接口支持数字音频和视频同步传输,VGA接口只支持视频传输

- HDMI接口在信号传输时抗干扰;VGA接口在信号传输时容易受其他信号干扰。

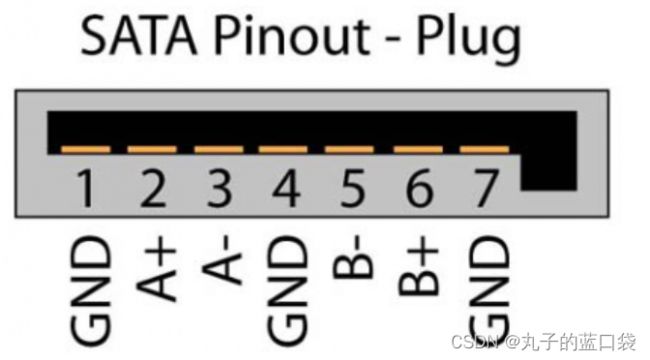

2.3 SATA接口

SATA:Serial ATA(Serial Advanced Technology Attachment)串行ATA,是一种硬盘接口规范,是一种总线接口。

SATA接口有三个级别,SATA是第一代速度为1.5Gb/s,SATA2是第二代的每秒3Gb速度,SATA3是每秒6Gb速度.

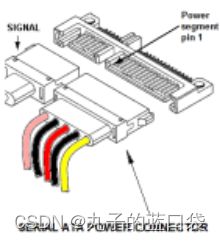

SATA接口包括:数据接口和电源接口。

数据接口的定义如下:

电源接口的定义如下,三路电源是为了兼容不同的负载:

- SATA(串行ATA)是SSD(Solid State Disk)使用的一种连接接口

- PCIe(Peripheral Component Interconnect Express)可以视为与主板更直接的数据连接。它通常用于显卡等设备

- PCIe相对来说速率更快

2.4 Serdes接口

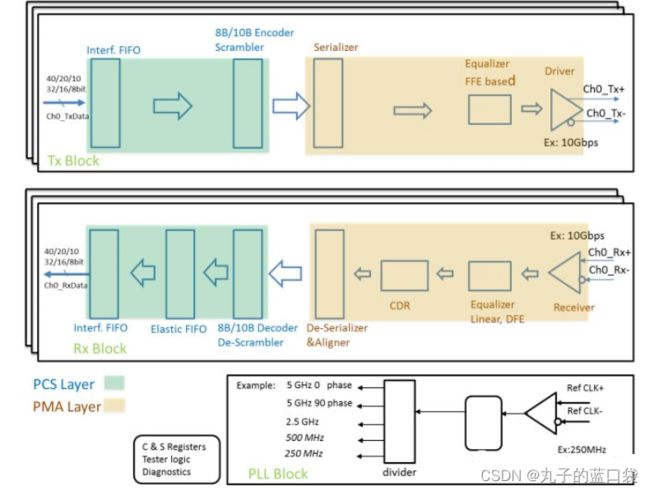

SerDes(Serializer-Deserializer):是串行器和解串器的简称.串行器Serializer把并行信号转化为串行信号。Deserializer把串行信号转化为并行信号。

Xilinx公司的许多FPGA已经内置了一个或多个MGT(Multi-Gigabit Transceiver)收发器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。

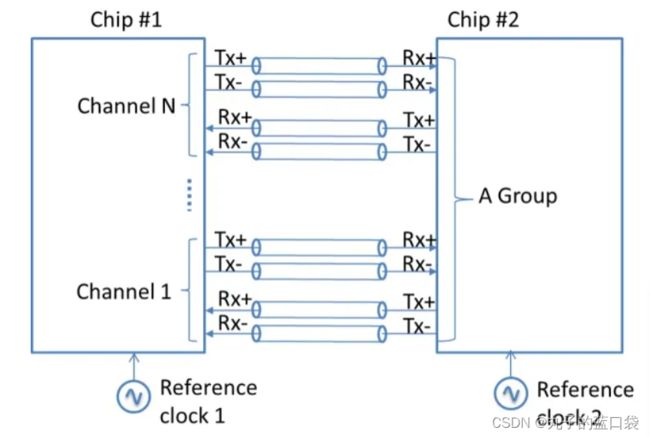

SerDes不传送时钟信号,SerDes采用差分方式传送数据。SerDes用到的通道少,但是速率高。

SerDes的主要构成可以分为三部分,PLL模块,发送模块Tx,接收模块Rx。

基本框图如下:

serdes连接示意图:

由于串行信号速率太高,必须有信号均衡Equalizer技术来保证信号完整性。

相比源同步接口,SerDes的主要特点包括:

1 在数据线中时钟内嵌,不需要传送时钟信号。

2 通过加重/均衡技术可以实现高速长距离传输,如背板(路由器输入端与输出端之间的物理通道)。

3 使用了较少的芯片引脚。

(注:关于serdes的传输速率和距离介绍较少,之后看到补充)

2.5 LVDS接口

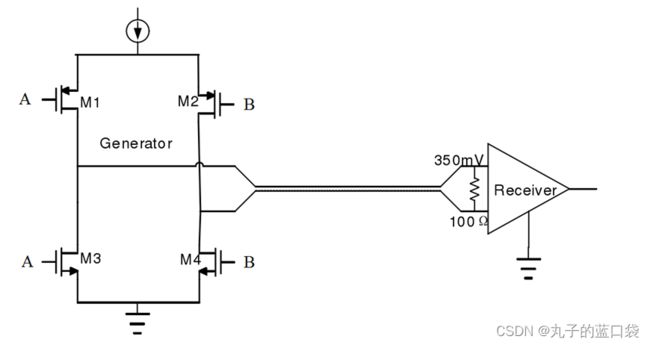

LVDS:low voltage differential signal低压差分信号。

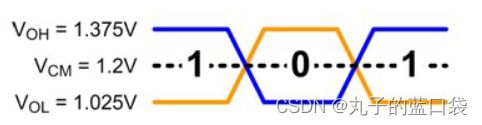

LVDS信号是一种高速接口标准。LVDS包括驱动器和接收器,终端电阻是100Ω,驱动器的恒流源是3.5mA,所以当两路差分信号差为350mV时,代表逻辑1,为-350mV,代表逻辑0。

驱动器的输出电压在1.2V左右摆动

LVDS信号的特点是:

- 推荐的最高数据传输速率是655Mbps,而理论上可以达到1.923Gbps。

- 低功耗—低误码率—低串扰—低抖动—低辐射

- 良好的信号完整性。

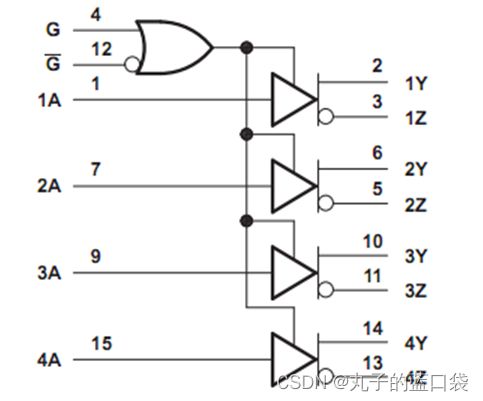

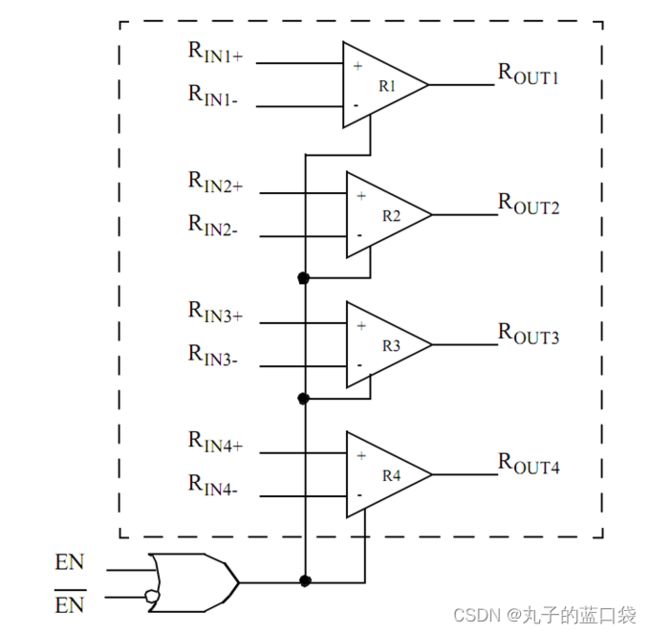

LVDS 驱动器的框图如下:

LVDS 接收器的框图如下:

其他差分信号。

2.6 1553B接口

1553B总线是 MIL-STD-1553B总线的简称,B是BUS。是美国空军电子子系统联网的标准总线,是一种中央集权式的串行总线,由于1553B总线具有极高的可靠性,因而在航空、航天、军事等领域的电子联网系统中得到广泛应用。

1553B 是总线接口规律和信号特性的标准,传输速度为1Mbps传输方式为半双工方式。总线本身是一个二冗余的结构,包括总线A和总线B,二者互为冗余备份。1553B总线耦合方式有直接耦合和变压器耦合,考虑到终端故障隔离,采用变压器耦合,编码方式为曼彻斯特码。

曼彻斯特编码又称曼彻斯特相位编码,它通过相位变化来实现每个位.通常,用一个时钟周期中部的上升沿表示“1”,下降沿表示“0”.周期末端的相位变化可忽略不计。

1553B控制器包括总线控制器BC、远程终端RT、总线监视器MT。总线上只能有一个总线控制器BC和不多于31远程终端RT(某些文献也称其为远程终端或者远程单元),总线监视器是可选的,用于监视总线通讯,一般不参与通讯。

总线控制器: bus controller,负责总线的调度、管理,是总线通讯的发起者和组织者。

远程终端:remote terminal,只能被动的接收或者发送和自己有关的数据。

总线监视器:bus monitor terminal,能够全部或选择性的监视总线的通讯过程,对通讯状态进行分析和判断,给出参与总线通讯的总线控制器和各个远置终端的运行状态和健康状态。

特点是分布处理、集中控制和实时响应。每条消息最长由32个字组成,所有的字分为三类:命令字、数据字和状态字。每类字的长度为20位,有效信息位是16位,每个字的前3位为单字的同步字头,而最后1位是奇偶校验位。

1553B总线上消息传输的过程是:总线控制器向某一终端发布一个接收/发送指令,终端在给定的响应时间范围内返回一个状态字并执行消息的接收/发送。BC通过验收RT回答的状态字来检验传输是否 成功并做后续的操作。

FC-AE-1553 是 Fiber Channel-Avionics Environment-Upper Layer Protocol MIL-STD-1553B Notice 2 的简称。FC-AE-1553 网络既具有 MIL-STD-1553B 网络的基本特性,又具有光纤通道的良好网络性能。MIL-STD-1553B传输媒介为屏蔽双绞线。1553B 总线采用异步数据传输方式,采用曼彻斯特II型码,差分传输。

FC-AE-1553总线可采用交换式和总线式的拓扑结构,交换式结构支持2^24个节点,总线式结构支持32个节点,交换式和总线式结构均支持1/2/4Gbps的网络传输速率且误码率不大于1/10.

FC-AE-1553 网络的主要构成包括网络控制器(NC:Network Controller),若干网络终端(NT:Network Terminal)及兼容传统1553B总线的RT (Remote Terminal ,远置终端) 的桥设备(Bridge,BG),网络监视器(NM: Network Monitor)以及FC-AE交换机或若干光纤耦合器(OC: Optical Coupler)组成的光纤分配网络(ODN: Optical Distribution Network),

与MIL-STD-1553B相比,FC-AE-1553支持的网络节点数从32个增加到2的24次方个,子地址数也从32个扩展到2的24次方,每条消息传输最大数据量从32个字,增加到2的32次方个字。

CAN与1553B比较:

- 1553B是集权的通信协议,CAN是分权

- 1553B可靠性高,不会被总线的其他设备干扰

- 两者的速率均可达到1Mbps.

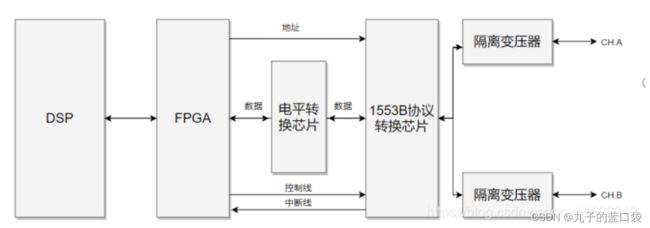

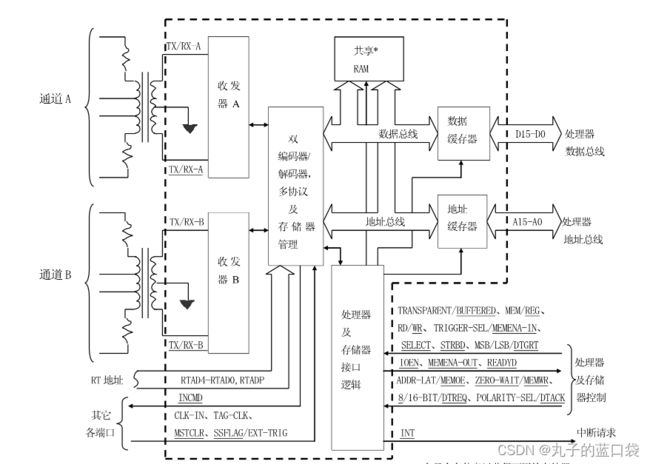

硬件连接框图如下:

1553B使用隔离变压器的原因:实现短路保护,直流隔离和阻抗匹配。总线接口与终端距离小于0.3048m,只用使用隔离变压器,否则还需要使用变压器耦合。变压器的匝数与终端电源有关。

用的比较多的是BU-61580及其对标的国产芯片。

内部框图如下:

2.7 Spacewire接口

SpaceWire总线(ECSS-E-ST-50-12C标准)是一种中高速、双向、全双工、点对点的串行总线,其传输速率为2Mbps~400Mbps。

SpaceWire接口是用于处理航天器上的有效载荷数据的点对点电缆总线。

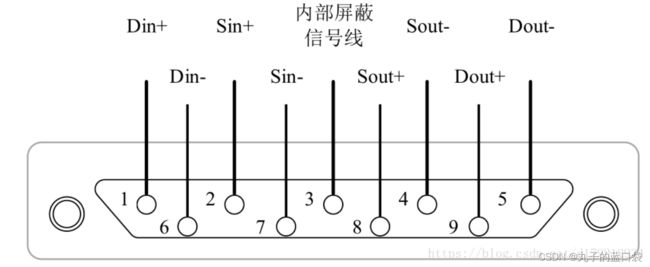

SpaceWire连接器信号定义如下,8根信号线即数据-选通(Data-Strobe)编码中的四对差分信号线。数据-选通(Data-Strobe)编码,将时钟和数据共同编码成选通信号,在接收端对这两个信号进行简单的异或,即可恢复出时钟信号。

信号采用LVDS双绞线方式传输,SpaceWire标准中采用数据-选通(Data-Strobe)编码方案。即将时钟和数据共同编码成选通信号,在接收端对这两个信号进行简单的异或,即可恢复出时钟信号。

SpaceWire链路包括两对差分信号,一对在一个方向上传输D和S信号,另一对在相反方向传输D和S信号。每个双向链路总共需要八条电线。