Serdes原理

Serdes原理

1.为什么需要SerDes?

电子系统中,传送数据的方式一般有两种方式,串口或者并口,具体定义不区分。先来说一下同步与异步通信。二者的区别在于是否有时钟线来对齐数据,采样数据。一般而言,并行通信都会有时钟线用来采样,现在的系统中最常见的就是DDR。

对于系统的互联,随着性能的提高,速率当然要求越来越高。对于理想状态而言,自然是并口要快于串口,其缺点也很明显,就是需要更多的接口资源。

在不断提高信号速率的过程中,有几个条件会限制并行通信速率的提高

-

时钟到达两个芯片的传播延时不相等(clock skew)

-

并行数据各个bit的传播延时不相等(data skew)

-

时钟的传播延时和数据的传播延时不一致(skew between data and clock)

数据可以正确的采样的条件是要满足建立保持时间,当时钟线与数据线之间存在skew时,随之而来的是保持时间的减少,这就导致了数据采样出错概率增大,当数据线的位宽越大时,保持时间的窗口是各个数据线之间与的关系,也就是说数据线越多,数据有效窗口就越小。如下图:

以DDR为例,DDR3的读写速率可以达到1066~2400Mhz,在时钟速率的提高还有一个现象会成为瓶颈,就是同步开关噪声(SSN)。

要提高接口的传输带宽有两种方式,一种是提高时钟频率,一种是加大数据位宽。那么是不是可以无限制的增加数据的位宽呢?这就要牵涉到另外一个非常重要的问题-----同步开关噪声(SSN)。

这里不讨论SSN的原理,直接给出SSN的公式:

SSN = L *N* di/dt。

L是芯片封装电感,N是数据宽度,di/dt是电流变化的斜率。

并行通信中数据位宽就意味着要同时开关更多的接口,因此开关的同时电流的变化的变化也更大,并且速率的提高也同时导致di/dt增大。

因此也不可能靠无限的提高数据位宽来继续增加带宽。一种解决SSN的办法是使用差分信号替代单端信号,使用差分信号可以很好的解决SSN问题,代价是使用更多的芯片引脚。使用差分信号仍然解决不了数据skew的问题,很大位宽的差分信号再加上严格的时序限制,给并行接口带来了很大的挑战。Serdes因此应运而生!

2.什么是SerDes?

串口是系统设计中比较常用的接口,低速串口中比较常见的是UART、SPI、I2C等,我们的目标是提升系统的性能,获得更高的数据带宽,高速的串口接口就要说到Serdes接口,什么是SerDes?

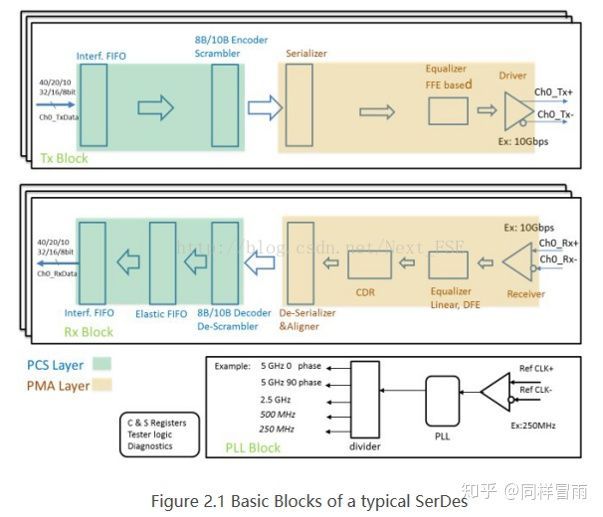

SerDes是一个合成词,全程是串行器/解串器,将低速并行数据转换成串行数据发送出去,接收端再把串行数据解码为并行数据。结构主要包括3部分:发送端、接收端、PLL部分。

底色为浅绿色的子模块为PCS层,负责数据流的编码/解码,是标准的可综合CMOS数字逻辑,可以硬逻辑实现,也可以使用FPGA软逻辑实现。

底色为浅褐色子模块是PMA层,是数模混合CML/CMOS电路,负责负责串化/解串化,是理解SerDes区别于并行接口的关键。

PMD是负责串行信号传输的电气块。

PLL模块(PLL Block)负责产生SerDes各个模块所需要的时钟信号,并管理这些时钟之间的相位关系。

3.SerDes为什么快?

作为串行接口,如何做到比并行接口快呢?主要有以下几方面的原因:

- 串口使用差分线进行传输,因此噪声的抗干扰能力要强很多,并不是说并口不能使用差分线,由于并行线位宽较宽,IO端口数量的再翻一倍,则系统设计更加困难,并且要做到数据线skew,做到等长更加困难。

- SerDes中还有一项重要技术,CDR可以将时钟编码进数据线中,这样就避免时钟与数据线之间的skew对数据传输的影响

- SerDes中还有另一个重要技术:预加重和均衡,对于改善信道质量有很大提升,能有效提高数据传输速度

4.串行器/解串器

串行器Serializer把并行信号转化为串行信号。Deserializer把串行信号转化为并行信号。一般地,并行信号为8 /10bit或者16/20bit宽度,串行信号为1bit宽度(也可以分阶段串行化,如8bit->4bit->2bit->equalizer->1bit以降低equalizer的工作频率)。

接收方向除了Deserializer之外,一般带有还有对齐功能逻辑(Aligner)。相对SerDes发送端,SerDes接收端起始工作的时刻是任意的,接收器正确接收的第一个 bit可能是发送数据的任意bit位置。因此需要对齐逻辑来判断从什么bit位置开始(哪里开始算是第一个数据),以组成正确的并行数据。对齐逻辑通过在串行数据流中搜索特征码字(Alignment Code)来决定串并转换的起始位置,这就需要用到了8b/10b的控制字符集,也就是我们常说的**“K”字符**,常见的什么K28.5、K28.0、K28.3、K28.4等,在JESD204B中他们又称/K/、/R/、/A/、/Q/字符。

5.时钟数据恢复(CDR)

CDR(Clock Data Recovery )即时钟数据恢复,是SerDes设计中非常重要的环节。CDR通常采用PLL实现,当数据经过时,CDR就会捕获数据边沿跳变的频率,如果数据长时间没有跳变,CDR就无法得到精确的训练,CDR采样时刻就会漂移,可能采到比真实数据更多的“0”或“1”。这就是为什么我们在发送的时候会进行扰码或者编码来避免重复出现“0”或者“1”,所以CDR有一个指标叫做最长连“0”或“1”长度容忍。

恢复时钟之后,需要恢复数据。第一步首先要将恢复出来的时钟与数据边缘进行对齐,然后再将数据给读出来。在硬件原理上,使用PLL电路以及触发器即可。

6.均衡与加重

SerDes信号从发送芯片到达接收芯片所经过的路径称为信道(channel),包括芯片封装、PCB走线、过孔、电缆、连接器等元件。从频域来看,信道可以简化为一个低通滤波器模型,如果SerDes的速率大于信道的截至频率,就会一定程度损伤信号(高频被滤掉了,数字信号边沿会变得平滑)。均衡的作用就是补偿信道对信号的损伤。

发送端的均衡器采用FFE(Feed forward equalizers)结构,从频域上看,FFE是一个高通滤波器(容易理解,信道损伤是一个低通滤波器,会抑制高频,那么均衡器就补偿高频)。从时域上看,又叫加重器(emphasis)。加重分为去加重(de-emphasis)和预加重(pre-emphasis)。De-emphasis降低差分信号的摆幅(swing)。pre-emphasis增加差分信号的摆福。

接收端均衡器的目标和发送均衡器目标是一致的。对于低速(<5Gbps)SerDes,通常采用连续时域、线性均衡器实现如尖峰发达器(peaking amplifier),均衡器对高频分量的增益大于对低频分量的增益。

7.引用

https://zhuanlan.zhihu.com/p/113737215

https://zhuanlan.zhihu.com/p/115422685