Verilog基本语法之运算符(三)

运算符分类

运算符按功能分为9类:

算术运算符

逻辑运算符

关系运算符

等式运算符

缩减运算符

条件运算符

位运算符

移位运算符

位拼接运算符

运算符按操作数的个数分为3类:

单目运算符:带一个操作数 逻辑非!,按位取反~,缩减运算符,移位运算符

双目运算符:带两个操作数 算术,关系,等式运算,逻辑,位运算符的大部分

三目运算符: 带三个操作数 条件运算符

算术运算符:

| 算术运算符 | 说明 |

| + | 加 |

| - | 减 |

| * | 乘 |

| / | 除 |

| % | 求模 |

进行整数除法时,结果值略去小数部分,只取整数部分

%为求模运算符,要求%两侧均为整型数据

求模运算结果值的符号位取第一个操作数的符号位

例: -11%3 结果为-2

进行算术运算时,若某操作数为不定值x,则整个结果也为x

逻辑运算符:

逻辑运算符把它的操作数当成布尔变量;

非零的操作数被认为是真(1’b1);

零被认为是假(1’b0);

不确定的操作数如4‘bxx00,被认为是不确定的(可能为零,也可能是非零);但4‘bxx11,被认为是真

| 逻辑运算符 | 说明 |

| &&(双目) | 逻辑与 |

| ||(双目) | 逻辑或 |

| !(单目) | 逻辑非 |

进行逻辑运算后的结果为布尔值(1或0)

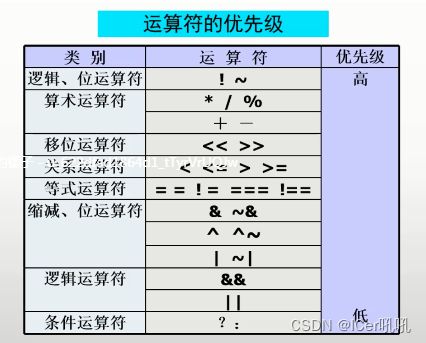

&&和||的优先级除高于条件运算符外,低于关系运算符,等式运算符等几乎所有运算符

逻辑非!优先级最高

例:(a>b)&&(b>c) 可简写为:a>b && b>c

(a==b)||(x==y) 可简写为:a==b || x==y

(!a) || (a>b) 可简写为: !a || a>b

建议采用带括号形式

位运算符:

| 位运算符 | 说明 |

| ~(单目) | 按位取反 |

| &(双目) | 按位与 |

| | (双目) | 按位或 |

| ^(双目) | 按位异或 |

| ^~,~^(双目) | 按位同或 |

位运算其结果与操作数位数相同。位运算符中的双目运算符要求对两个操作数的相应位逐位进行运算。

两个不同长度的操作数进行位运算时,将自动按右端对齐,位数少的操作数会在高位0补齐

例 a=5'b11011 b=3'b001 a&b = 5'00001

关系运算符(双目):

| 关系运算符 | 说明 |

| < | 小于 |

| <= | 小于等于 |

| > | 大于 |

| >= | 大于等于 |

运算结果为1位的逻辑值1或0或x.关系运算时,若关系为真,则返回值为1;若关系为假,则返回值为0;若某操作数为不定值x,则返回值为x。

所有关系运算符优先级别相同。

关系运算符的优先级别低于算术运算符。

例:a

等式运算符:

| 等式运算符 | 说明 |

| == | 等于 |

| != | 不等于 |

| === | 全等 |

| !== | 不全等 |

运算结果为1位的逻辑值1或0或x.

等于运算符(==)和全等运算符(===)的区别:

使用等式运算符时两个操作数必须逐位相等,结果才为1;若某些位为x或z,则结果为x;

使用全等运算符时,若两个操作数的相应位完全一致(如同是1,0,x,z)则结果为1;否则为0.

所有的等式运算符优先级别相同

===和!==运算符常用于case表达式的判别,又称为"case等式运算符".

| == | 0 | 1 | x | z |

| 0 | 0 | 0 | x | x |

| 1 | 0 | 1 | x | x |

| x | x | x | x | x |

| z | x | x | x | x |

| === | 0 | 1 | x | z |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| x | 0 | 0 | 1 | 0 |

| z | 0 | 0 | 0 | 1 |

缩减运算符 (单目)

| 缩减运算符 | 说明 |

| & | 与 |

| ~& | 与非 |

| | | 或 |

| ~| | 或非 |

| ^ | 异或 |

| ^~,~^ | 同或 |

对单个操作数进行递推运算,即先将操作数的最低位于第二位进行与,或,非运算,再将运算结果与第三位进行相同运算,一次类推直至高位。

最后运算结果缩减为1位二进制数

例:reg[3:0] a;

b =|a; //等效于b=((a[0] | a[1]) |a(2)) | a[3]

移位运算符(单目)

| 移位运算符 | 说明 |

| >> | 右移 |

| << | 左移 |

A >>n 或A<< n

将操作数右移或左移n位,同时用n个0填补移出的空位

左移会扩充位数,右移位数不变,但数据会丢失

条件运算符(三目)

信号 = 条件?表达式1:表达式2

当条件为真,信号取表达式1的值,条件为假,则取表达式2的值

位拼接运算符

运算符号{ },用于将两个或多个信号的某些位拼接起来,表示一个整体信号。

{信号1,信号2}

output [3:0] sum;

output cout;

input [3:0] ina, inb;

input cin;

assign {cout,sum} =ina + inb + cin; //进位与和拼接在一起算术运算符

用重复法简化表达式,如:{4{w}} //等同于{w,w,w,w}

还可用嵌套方法简化书写,如{b,{3{a,b}} //{b,a,b,a,b,a}

在为拼接表达式中,不允许存在没有指明位数的信号,必须指明信号的位数;若未指明,则默认为32位的二进制数;

如{1,0}=64’h00000001_00000000, 不是2‘b10