ARMV8 B2 The AArch64 Application level memory mdel

ARMV8 B2 The AArch64 Application level memory mdel

ARM memory model 允许指令的observation 和 completion 按不同的顺序进行,因此是一种弱有序的存储架构,本章的章节主要给出ARMV8 存储架构详细的定义,ARMV8 存储架构的主要原则如下

- 提供一个存储模型,该模型与C或Java等高级编程语言使用的内存模型具有类似的弱点(weakness)。例如,允许独立内存访问按照其他观察者看到的顺序重新排序。

- 避免了大多数存储类型的mult-copy

- 在必要的情况下,提供指令和内存屏障(memory barriers)以弥补multi-copy的不足

- 在创建顺序时使用地址、数据和控制依赖项,以避免在程序员或编译器需要某些顺序的常见情况下出现过多的障碍或其他明确指令。

- 如果实现并启用了FEAT_MTE,则应用于数据访问和数据的内存模型定义也应用于分配标签访问和分配标签。

- 此外还有两个概念:Address space, Memory type overview

Address space: 64bit, 高8位会被supervisory软件作为memory tag

这个tag在判断地址是否有效时不加入判断;不propagated to PC

Memory type overview:

(1).Normal:bulk memory operation,both read/write and read-only operation

(2).Device:不允许投机读

device memory 还有以下的特点:

1 它们防止多次读/写操作的merge,从而保持指定内存访问的数量和大小

2 它们保持了访问单个外围设备的访问顺序和同步要求

3 它可以确认一个写操作是否到达end of point

文章目录

- ARMV8 B2 The AArch64 Application level memory mdel

- 第一节 ARM 架构中的原子操作

- 第二节 cache and memory hierarchy

- 第三节 Alignment support

- 第四节 Endian support

- 第五节 memory types and attributes

第一节 ARM 架构中的原子操作

原子特性是一种内存访问时的特性,也被称为原子访问。ARM架构将原子操作分成两种,分别为单原子操作和多原子操作,原子操作就是多线程程序中“最小的且不可并行化的”操作。对于在多个线程间共享的一个资源而言,这意味着同一时刻,多个线程中有且仅有一个线程在对这个资源进行操作,即互斥访问

(附上对automic解释较好的一篇博文:atomic)

atomic 的一些重要概念的理解:

Observer: An Observer refers to a processing element or mechanism in the system, such as a peripheral device, that can generate reads from, or writes to, memory.

这里的observer可以理解ARM体系内可以对memory发起read或者write的对象

Common Shareability Domain:For the purpose of this section, all Observers are assumed to belong to a Common Shareability Domain. All read and write effects access only Normal memory locations in a Common Shareability Domain,

这里的Shareability domain可以理解为所有Observers 所共享的内存位置

coherence order:There is a per-location Coherence order relation that provides a total order over all writes from all coherent Observers to that Location, starting with a notional write of the initial value. The Coherence order of a Location represents the order in which writes to the Location arrive at memory

一个比较重要的概念Coherence order:对于某个特定的location, coherence order 指的是对所有observer 看到的对该location写操作顺序是coherent的一种总的顺序,总的顺序是因为每个observer看到的顺序不都是全的。

Reads-from:

The Reads-from relation couples reads and writes to the same Location such that each read is paired

with exactly one write in the execution of a program. A read R2 from a Location Reads-from a write W1 to the same Location if and only if R2 takes its data from W1.

reads-from将read和write组成了相对关系,相对关系建立在read从他read-from的location上取得数

Coherence-after:A write W2 to a Location is Coherence-after another write W1 to the same Location if and only if W2 is sequenced after W1 in the Coherence order of the Location.

A write W2 to a Location is Coherence-after a read R1 of the same location if and only if R1 Reads-from a write W3 to the same Location and W2 is Coherence-after W3

可以理解为写1 coherence-after写2的是指在coherence-order上写1是在写2的前面,中间没有其他的写

读1 coherence-after 写1是指

Single-atomic copy: A read or write operation is single-copy atomic only if it meets the following conditions:

- For a single-copy atomic store, if the store overlaps another single-copy atomic store, then all of the writes from one of the stores are inserted into the Coherence order of each overlapping byte before any of the writes of the other store are inserted into the Coherence orders of the overlapping bytes.

- If a single-copy atomic load overlaps a single-copy atomic store and for any of the overlapping bytes the load returns the data written by the write inserted into the Coherence order of that byte by the single-copy atomic store then the load must return data from a point in the Coherence order no earlier than the writes inserted into the Coherence order by the single-copy atomic store of all of the overlapping bytes.

ARMV8 对Single-atomic copy的定义:A memory access instruction that is single-copy atomic has the following properties:

- For a pair of overlapping single-copy atomic store instructions, all of the overlapping writes generated by one of the stores are Coherence-after the corresponding overlapping writes generated by the other store.

- For a single-copy atomic load instruction L1 that overlaps a single-copy atomic store instruction S2, if one of the overlapping reads generated by L1 Reads-from one of the overlapping writes generated by S2, then none of the overlapping writes generated by S2 are Coherence-after the corresponding overlapping reads generated by L1.

早期这个的定义包括两方面:1. store overlaps single-copy atomic,overlap是指所操作的location 有重叠,这样对于store overlaps single-copy atomic可以理解为两笔有overlap的store,每笔store的所有写操作是插入到这个coherence order,意思是这笔store对应的所有写操作是原子不可分割的,也就是在此期间任何observer都只能是两笔store中某一笔完成写操作后的状态,而不能是两笔store的混合状态。2.如果一笔store和一笔load有重叠,则这笔load得到的是一个store完成所有写操作的的值,或者完全没有写过的值,也是就是store的原子性

在ARMV8中更新的定义表达的更加清晰:1.两个store之间的关系是coherent-after的,也就是每一笔的store是原子不可打断的;2.如果一个load(L1)和一个store(S2)之间有overlaping,并且现在确定overlap的一部分是read-from这个S2的,也就是说L1应该是coherence-afters2的,那么可以说,S2绝不会coherence-after到L1。总结来说就是相互overlap的L1和S2,各自是原子的不可分割,不可能出现中间状态。

Multi-atomic copy:In a multiprocessing system, writes to a memory location are multi-copy atomic if the following conditions are both

true:

• All writes to the same location are serialized, meaning they are observed in the same order by all observers, although some observers might not observe all of the writes.

• A read of a location does not return the value of a write until all observers observe that write

Multi-atomic copy特指在多核环境中,多个store的顺序以及不同observer的交互,1.对同一location的所有写入都被序列化,这意味着所有observer都会以相同的顺序观察到它们,尽管有些observer可能不会观察到所有写入,这说明除了single-atomic 描述的load的coherent, 还提出了对store的coherent。2.对一个地址进行的load操作会被block,直到该地址的值对所有的observer都是可见的。

基于以上基本概念的理解可以对ARM中对atomic的要求和属性进行学习

- single-copy atomic

(1) 对齐的load或者store操作是Single-copy atomicity的。针对byte的内存操作总是Single-copy atomicity的,2B的load或者store操作如果地址对齐在2上,那么也是Single-copy atomicity的

(2) 对齐的load pair或者store可以看作是两个Single-copy atomicity load或者store

(3) load/store exclusive pair 是Single-copy atomicity (2 32bit quantities)的

(4) 对齐的SMID&FP load/store 单个64 bit的或者更小的quantity(量)

(5) 对其的SMID&FP 部分元素的store/load也是Single-copy atomicity的

在某些实现中,对于某些内存类型,原子属性只能通过PE之外的功能来满足,一些系统实现可能不支持所有内存区域的原子指令,这尤其适用于:1.不支持硬件cache coherency的任何存储;2.Device,non-cacheable memory,或者被看作是non-cacheable的memory,

第二节 cache and memory hierarchy

内存系统的实现在很大程度上取决于微体系结构,因此内存系统的许多细节都是由实现定义的。Armv8定义了与内存系统的应用程序级接口,包括具有多级缓存的分层内存系统。本节介绍此系统的应用程序级视图。它包含以下小节:

1.cache介绍

2.存储层次结构

3.对缓存相关功能的应用程序级访问

4.缓存对应用程序程序员的影响

5.预加载缓存

-

cache介绍

利用时间局部性,空间局部性 ,但引入很多问题:内存的访问可能发生在程序员预期之外的时间,以及数据可能存在多份copy -

存储层次结构

描述cache一致性的术语理解:

Point of Coherency (PoC) : 对于任何内存类型或可缓存存储的访问,保证所有可以访问内存的agent都能看到相同的内存location copy的点。在许多情况下,这实际上是主系统内存,尽管体系结构不禁止在PoC之外实现缓存,这些缓存对内存系统agent之间的一致性没有影响。可以理解为某一时间点上,所有的observer(agent)都能看到同一份数据

Point of Unification(PoU):

PE的PoU是指确保该PE的指令和数据缓存以及转换表能够看到内存位置的相同副本的点。在许多情况下,统一点是指单处理器内存系统中指令和数据缓存以及翻译表的合并点。

内部可共享共享性域的PoU是指确保该内部可共享共享性域中所有PE的指令和数据缓存以及转换表能够看到内存位置的相同副本的点。定义这一点允许自我修改软件,以确保未来的指令获取与软件的修改版本相关联,方法是使用以下标准正确性策略:

1.按地址清除数据缓存条目。

2.按地址使指令缓存项无效。

PoC和PoU的主要是意思指的是一个区域内所有agent都能看到某个location的copy,区别在于PoC所指的是所有可以访问内存(L2 cache,L3 cache)的agent,而PoU特指了PE的指令和数据缓存以及转换表,因此可以认为PoC的范围可以比PoU更大。

Point of Persistence(PoP):TBD

Point of Deep Persistence(PoDP):TBD

以下两个概念主要是用在多核的环境中:

Cache-ability:该处存储的数据是否可以装入cache,分为Inner和Outer的cache-ability

Share-ability: memory location 是否在不同的agents是共享的,如果是共享的那么这些agent对这个location必须保证是coherent的。分为Inner和Outer的Share-ability -

.对缓存相关功能的应用程序级访问

工作在操作系统的应用程序怎么感知和维护cache架构以及cache的coherent呢?当系统配置了某些bit后便可以:当SCTLR_EL1.UC1 = 1则DC CVAU, DC CVAC,DC CVAP,DC CVDP,DC CIVAC; -

缓存对应用程序程序员的影响

尽管绝大多数情况下程序对cached的存在是不可见的,但是在某些情况下会发生变成可见,例如cache not coherent时:1.当memory location 没有通过硬件一致性管理机制的方式被其他的agent 更新;2.在没有通过硬件一致性管理机制方式的情况下,被应用程序更新的memory location 必须被其他agent可以访问时。

具体的实际情况可能是:1.没有通过DMA一致性管理机制的情况下,PE更新了数据,但是DMA仍然拿的老数据;2,在harvard cache实现中,存在分离的指令cache和data cache,当新的指令数据写入到data cache中时,但是指令cache仍然包含着旧的指令数据

那么在这些情况下,程序能做什么可以维护cache的一致性?

1.当出现一致性违例时不使用cache,可以通过使用non-cacheable 存储,或者使用write-through的cache memory;或者不使能cache

2.使用维护cache一致性的指令,如上文所述 -

预加载缓存

这部分有也就是微架构中HWP(hardware prefetch)来源,ARM架构提供了内存系统的提示(hint),如PRFM,LDNP,STNP等,软件使用这些提示分析预期会使用的内存位置并传递信息给硬件,这样硬件可以将这些部分预取到cache,减少了cache的miss

第三节 Alignment support

分为指令对齐和数据的对齐;

- 指令对齐

指令必须32bit对齐,非对齐的指令访问会导致PC alignment fault - 数据对齐

对于非对齐的数据访问受系统寄存器的控制:

1.load/store of single or multiple register

(1)SCTLR_ELX =1; 则会产生fault

(2)SCTLR_ELx =0;则会进行一个非对齐的访问,如果FEAR_LSE2未配置,则产生falut,否则,当访问的地所有字节都位于16字节对齐的16字节数量内,并且都是正常的内部回写以及外部回写的可缓存内存,那么该内存访问时单拷贝原子的。对于load pair或者store pair 时,也是single-copy的

否则不保证时single copy

同理,load-exclusive/store-exclusive也是如此

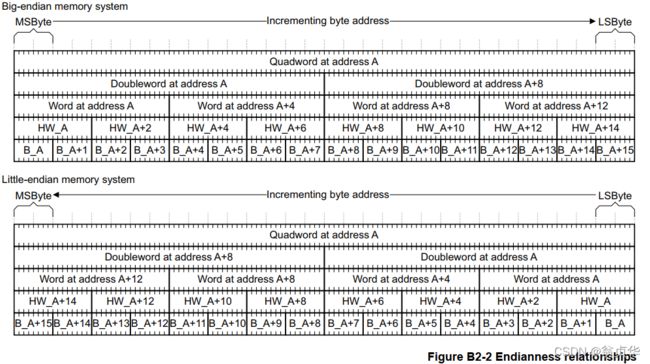

第四节 Endian support

大小端时指字节的排序方式,顺序和逆序,ARM 默认小端,可以使用大小端转换指令对数据进行转换

第五节 memory types and attributes

“正常内存类型”属性适用于系统中的大多数内存。它表示体系结构允许硬件对这些位置执行推测性数据读取访问,而不管这些位置的访问权限如何。普通内存类型具有以下属性:

- 对具有Normal属性的内存位置的写入在有限时间内完成。

- 对正常内存类型的内存位置进行写入,该内存类型为Non-cacheaolikble or Write-through cacheable 内部和外部可缓存性必须在有限时间内到达内存系统中该位置的结束点。对同一位置的两次写入(其中至少有一次使用normal内存类型)可能会在到达结束点之前合并,除非两次写入之间存在排序优先关系。

- 如果系统配置为生成normal内存访问,则未对齐内存访问可以访问normal内存。

- PE之外的内存系统不需要能够识别多寄存器加载/存储指令访问的元素。

- List item

memory attribute 的理解

shareable

- Shareable normal memory: inner shareable,shareable, and outer shareable normal memory

shareable 主要是对某个location的data coherent的定义

inner shareable domain包含一组observers,这些observers 对该区域内的某个location 的访问都是coherent的,该集合的任何成员都具有内部可共享属性。

同理,outter shareable domain包含一组observers,这些observers 对该区域内的某个location 的访问都是coherent的,该集合的任何成员都具有外部可共享属性。

Inner 也是 outer的一个子集

Because all data accesses to Non-cacheable locations are data coherent to all observers, Non-cacheable locations are always treated as Outer Shareable. - Non-shareable normal memory

表示该location 只能被一个PE所用

对于non-shareable normal memory的部分,硬件不需要保证data coherent,但是,当该location同时也是non-cacheable的时候,如果其他observer也来共享该location, 则软件需要使用cache maintenance 指令来维持data coherent,如果发现可能会导致coherent 问题则需要barrier 指令来保持顺序

cacheaility attribute normal memory