文章目录

-

- MMU总览

-

- MMU限制

-

-

- size

-

-

- 第一个size相关 : TCR.TGx

- 第二个size相关 : TCR.TxSZ

- 第三个size 相关 : TCR.IPS

- 内存属性

-

-

- Level 2

- Level 1 Shareability

- Level 1 Cacheability

- Cacheability 和 Shareability 的自由组合

- translation table walks 涉及的内存的内存属性

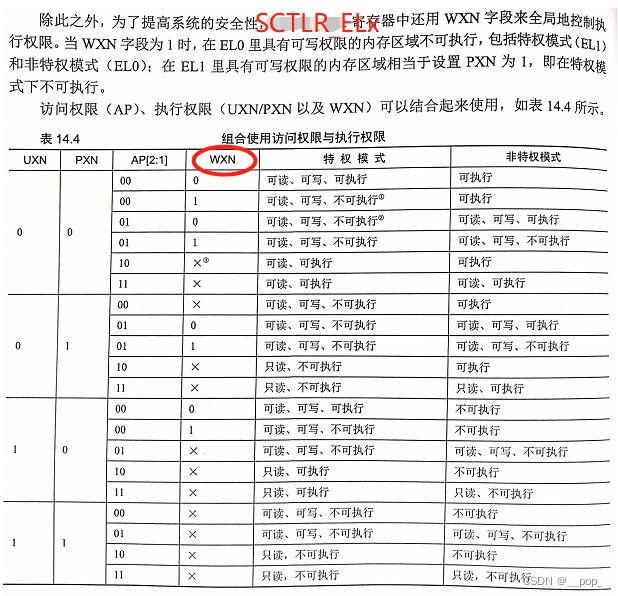

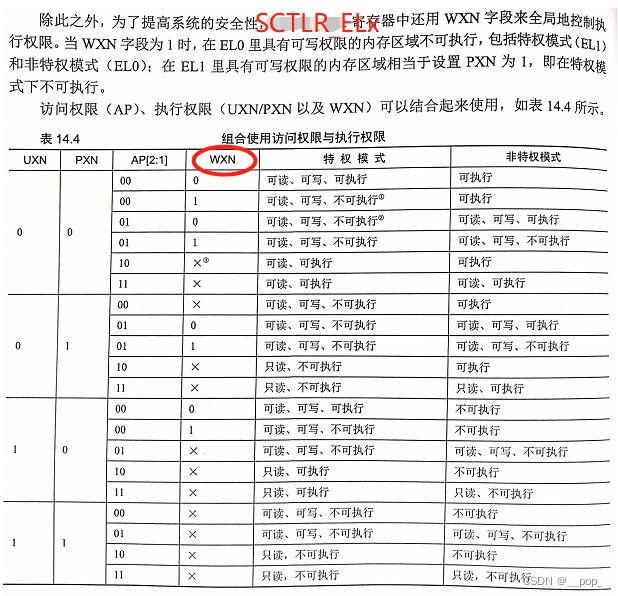

- 权限

- MMU 控制

-

-

- 寄存器

-

-

- MAIR

- TCR

- TTBL0/TTBL1

- SCTLR

- 页表

-

-

- 所有可能存在的页表

- L0/1/2 页表的描述

- L3 页表的描述

- Linux 对MMU的应用

-

-

- linux 对MAIR的应用

- Linux 对 内存属性(Shareability & Cacheability) 的应用

MMU总览

armv8 的 MMU 为 code 增加了一个新概念 : 虚拟地址 ,在这个概念之上,加了很多限制

目前好像是无法在物理地址上直接加限制的

相关的限制

size :有效位数 颗粒度

内存属性 :共享 缓冲缓存 内存顺序模型(普通/设备)

权限 :el0/1读写执行

相关的控制

寄存器

直接寄存器

TTBL0/TTBL1

TCR

SCTLR

间接寄存器

MAIR

页表

L0

L1

L2

L3

MMU限制

size

ARMv8 有两套页表机制,索引了两套页表

TTBR1_EL1

TTBR0_EL1

第一个size相关 : TCR.TGx

TGx 字段

0b00 : 4KB

0b01 : 16KB

0b11 : 64KB

第二个size相关 : TCR.TxSZ

TxSZ 字段:

va最大地址 : 2^(64-TxSZ)

第三个size 相关 : TCR.IPS

用来配置 地址转换(va->pa)后,得到的 物理地址(pa)的最大值

内存属性

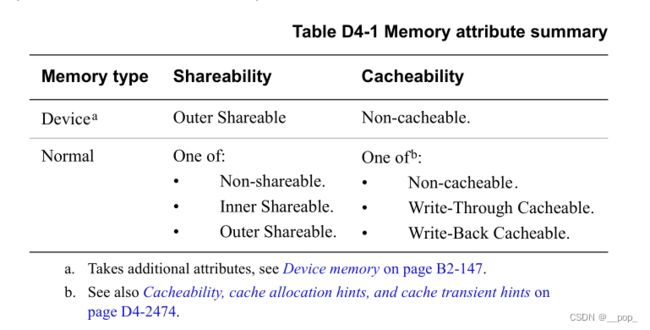

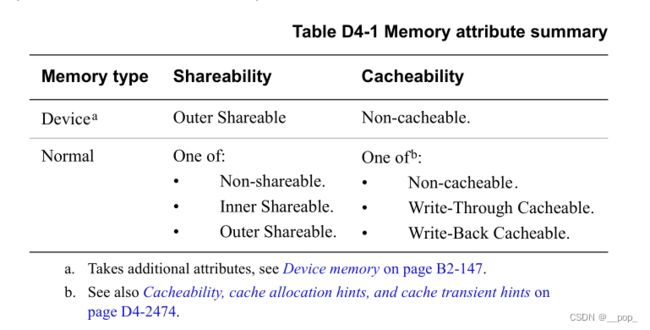

Level 2

内存顺序模型

Device : 更严格的访存方式

Normal : 比较宽松的访存方式

在实际应用中, Device/Normal 是 Cacheability & Shareability 的 封装

Device

Outer Shareable

Non-cacheable

Normal

Non-Shareable 或 Inner Shareable 或 Outer Shareable

Non-cacheable 或 Write-Through Cacheable 或 Write-Back Cacheable

Memory attribute summary P2468

1.为什么把他设置为这个属性

2.实际应用中怎么配置

3.设置了这个属性之后,mmu遇到后会怎么处理

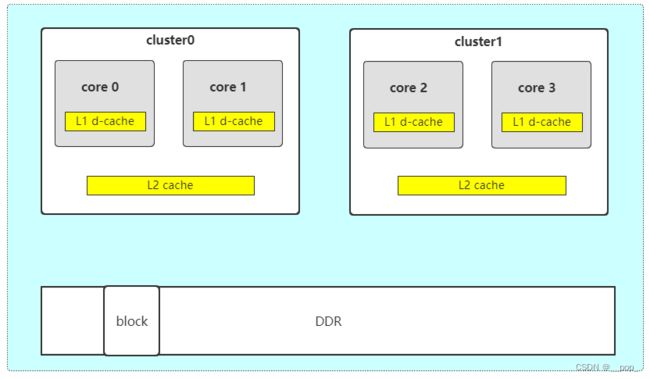

Level 1 Shareability

Shareability

不共享 : 只能被本地cpu能观察到

内部共享 : 只能被 具有"内部共享属性的高速缓存"的CPU 观察到

外部共享 : 能被外部共享的观察者(cpu,gpu,dma) 观察到

page.SH[1:0] :

0b00 没有共享性

0b01 保留

0b10 外部可共享

0b11 内部可共享

---

1.为什么把他设置为这个属性

想让其缓存到哪一层cache

2.实际应用中怎么配置

应该根据 内存的不同位置来配置

3.设置了这个属性之后,mmu遇到后会怎么处理

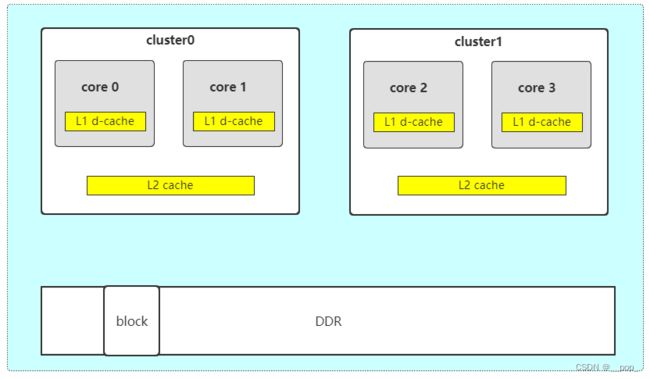

如果将block的内存属性配置成 non-shareable, 那么core0访问该内存时

数据缓存的到Core0的L1 d-cache 和 cluster0的L2 cache,不会缓存到其它cache中

如果将block的内存属性配置成 inner-shareable, 那么core0访问该内存时

数据只会缓存到core 0和core 1的L1 d-cache中, 也会缓存到clustor0的L2 cache,不会缓存到clustor1中的任何cache里。

如果将block的内存属性配置成 outer-shareable, 那么core0访问该内存时

数据会缓存到所有cache中

Level 1 Cacheability

cache 有 共享性 , 和 内存的共享性有什么关系?

TODO

Cacheability

TODO

SCTLR.I

开关icache高速缓存

SCTLR.C

开关data高速缓存

page.AttrIndx[2:0] :

索引 MAIR寄存器的 第 N 个内存属性

---

1.为什么把他设置为这个属性

因为想要读写的时候会不会缓存,什么时候缓存

2.实际应用中怎么配置

如果是设备内存,必须配置 Non-Cacheable

3.设置了这个属性之后,mmu遇到后会怎么处理

遇到 Non-Cacheable 的时候,直接写入内存,从内存读取

遇到 Write-Through Cacheable 的时候,直接写入cache,同时写入内存

遇到 Write-Back Cacheable 的时候, 写入cache,等cache失效的时候写入内存

如果将block的内存属性配置成Non-cacheable,那么数据就不会被缓存到cache,那么所有observer看到的内存是一致的,也就说此时也相当于Outer Shareable。

其实官方文档,也有这一句的描述:

在B2.7.2章节 “Data accesses to memory locations are coherent for all observers in the system, and correspondingly are treated as being Outer Shareable”

如果将block的内存属性配置成write-through cacheable 或 write-back cacheable,那么数据会被缓存cache中。write-through和write-back是缓存策略。

Cacheability 和 Shareability 的自由组合

translation table walks 涉及的内存的内存属性

translation table walk 时,会涉及到 页表 所在的内存

这些内存 的 Shareability 由 TCR.SHx 设置

这些内存 的 Cacheability 由 TCR.ORGNx/TCR.IRGNx 设置

TCR.SHx : 设置默认 Shareability

配置TTBRx 页表相关内存的高速缓存共享属性

0b00 : 不共享

0b10 : 外部共享

0b11 : 内部共享

TCR.ORGNx : 设置默认 Cacheability

配置TTBRx 页表相关内存 中的 外部共享内存

0b00 : 普通内存,外部共享,不高速缓存

0b01 : 普通内存,外部共享,高速缓存策略是 回写 写分配/读分配

0b10 : 普通内存,外部共享,高速缓存策略是 写直通 写不分配/读分配

0b11 : 普通内存,外部共享,高速缓存策略是 回写 写不分配/读分配

TCR.IRGNx : 设置默认 Cacheability

配置TTBRx 页表相关内存 中的 内部共享内存

0b00 : 普通内存,内部共享,不高速缓存

0b01 : 普通内存,内部共享,高速缓存策略是 回写 写分配/读分配

0b10 : 普通内存,内部共享,高速缓存策略是 写直通 写不分配/读分配

0b11 : 普通内存,内部共享,高速缓存策略是 回写 写不分配/读分配

权限

MMU 控制

寄存器

MAIR

描述 Cacheability

64bit寄存器,每8个bit描述一个memory type , 共可设置 8个 memory type(8个框)

用来被 page.AttrIndx[2:0] 索引 8个框 中的哪一个

TCR

TTBL0/TTBL1

SCTLR

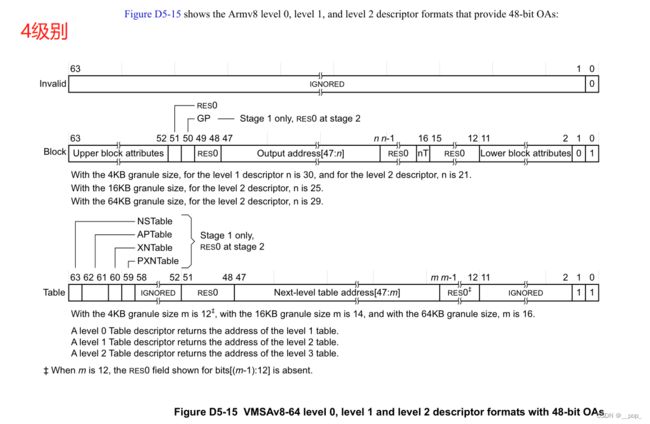

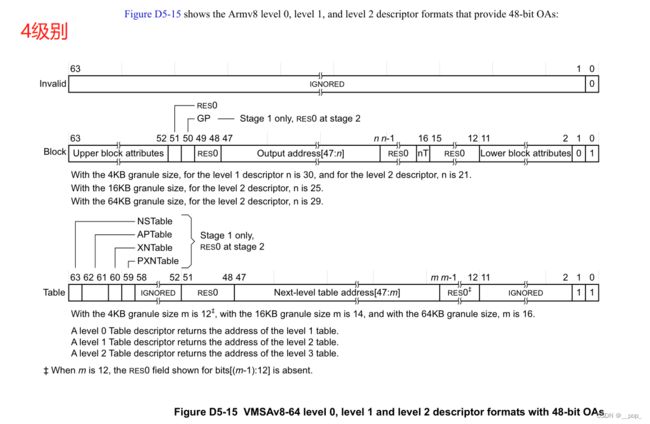

页表

最大支持 4级别(L0 L1 L2 L3)

64KB 的颗粒度为什么不从L0开始,而是从L1开始

因为 最后一个肯定是 L3,且最大为3级别, 所以只能从L1开始

L3 和 L0/1/2 定义不同 , L0/1/2 定义相同

所有可能存在的页表

| 最大级数 |

颗粒度 |

L0 |

L1 |

L2 |

L3 |

索引页面大小 |

| 4 |

4KB |

1 |

|

|

|

512GB(不支持) |

| 4 |

4KB |

1 |

1 |

|

|

1GB |

| 4 |

4KB |

1 |

1 |

1 |

|

2MB |

| 4 |

4KB |

1 |

1 |

1 |

1 |

4KB |

| 4 |

16KB |

1 |

|

|

|

512TB(不支持) |

| 4 |

16KB |

1 |

1 |

|

|

128TB(不支持) |

| 4 |

16KB |

1 |

1 |

1 |

|

32MB |

| 4 |

16KB |

1 |

1 |

1 |

1 |

16KB |

| 3 |

64KB |

|

1 |

|

|

4TB(ARMv8.2-LPA) |

| 3 |

64KB |

|

1 |

1 |

|

512MB |

| 3 |

64KB |

|

1 |

1 |

1 |

64KB |

L0/1/2 页表的描述

- 4级别(颗粒度为4/16KB)的L0/1/2

- 3级别(颗粒度为64KB)的L1/2

L3 页表的描述

Linux 对MMU的应用

linux 对MAIR的应用

ARM64中的 MAIR中的8bit,可以有 2^8个排列组合. 存在于 8 个 框中

但是 linux 只用到了五个框,MT_XXX 是 index(索引了MAIR), 并不是 MAIR 中的编码

---

132 #define MT_NORMAL 0

133 #define MT_NORMAL_TAGGED 1

134 #define MT_NORMAL_NC 2

135 #define MT_DEVICE_nGnRnE 3

136 #define MT_DEVICE_nGnRE 4

封装的API

----------------

MT_NORMAL

PROT_SECT_NORMAL

PROT_SECT_NORMAL_EXEC

PROT_NORMAL

PAGE_KERNEL

PAGE_KERNEL_RO

PAGE_KERNEL_ROX

PAGE_KERNEL_EXEC

PAGE_KERNEL_EXEC_CONT

_PAGE_DEFAULT

PAGE_NONE

PAGE_SHARED

PAGE_SHARED_EXEC

PAGE_READONLY

PAGE_READONLY_EXEC

PAGE_EXECONLY

MT_NORMAL_TAGGED

pgprot_tagged 和 pgprot_mhp

PROT_NORMAL_TAGGED -> 无

MT_DEVICE_nGnRE

pgprot_device

PROT_DEVICE_nGnRE -> ioremap

|-> FIXMAP_PAGE_IO

MT_DEVICE_nGnRnE

pgprot_noncached

PROT_DEVICE_nGnRnE -> ioremap_np

MT_NORMAL_NC

pgprot_writecombine

PROT_NORMAL_NC -> ioremap_wc

Linux 对 内存属性(Shareability & Cacheability) 的应用