数字IC/FPGA面试笔试准备(自用填坑中)

文章目录

-

- 前言

- 常见的IC问题

- 数字电路基础问题

- Verilog & SV

-

-

- 跨时钟域信号处理类

- CRG 同步与异步复位

- 综合与时序分析类

- 低功耗方法

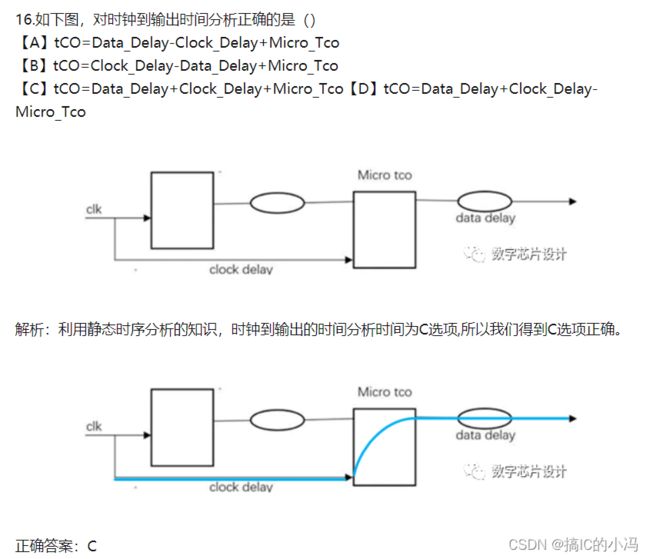

- STA(静态时序分析)

- RTL设计(包含手撕代码)

- 总线问题

-

- AXI

- APB

- AHB

- 体系结构的问题

- RISCV的问题

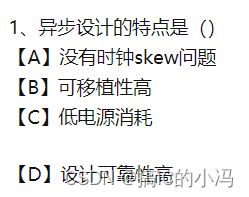

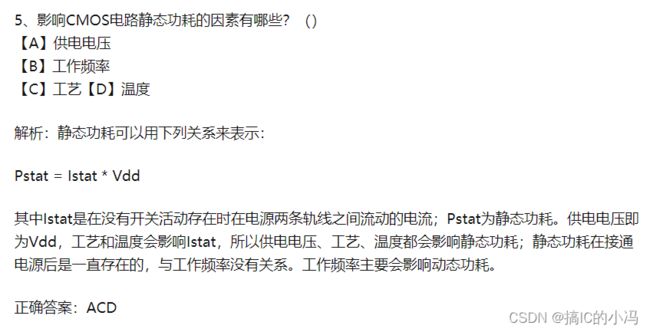

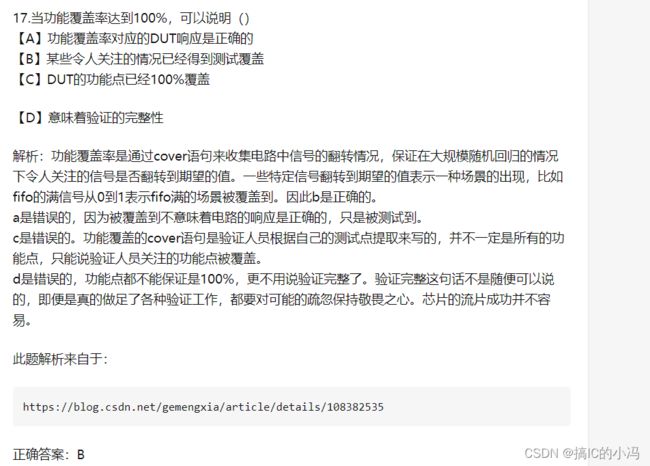

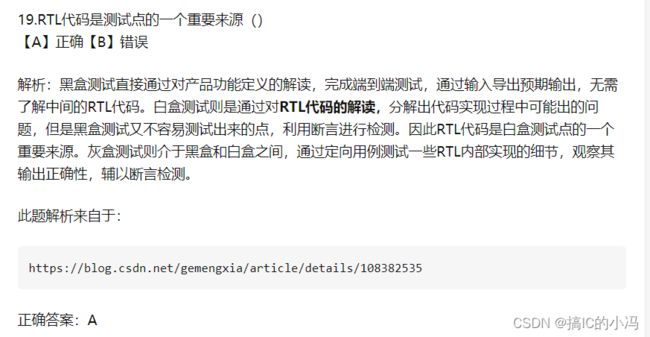

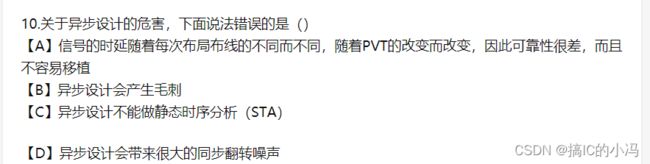

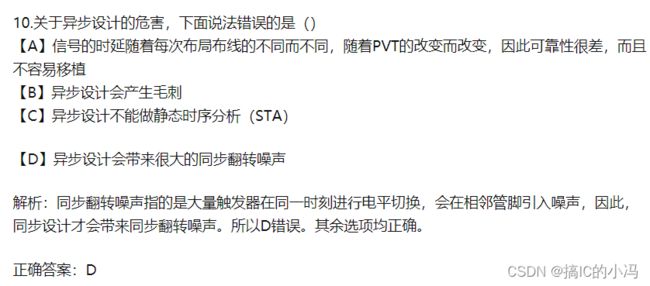

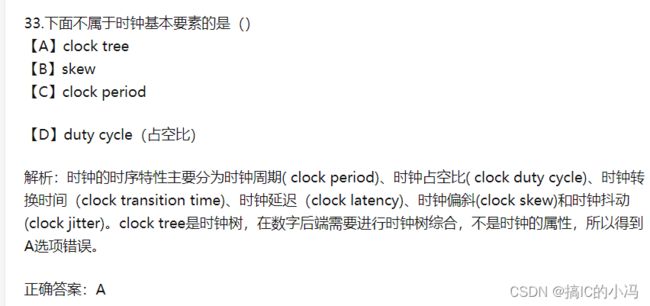

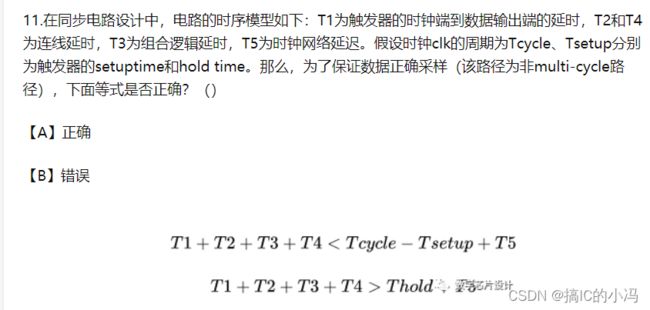

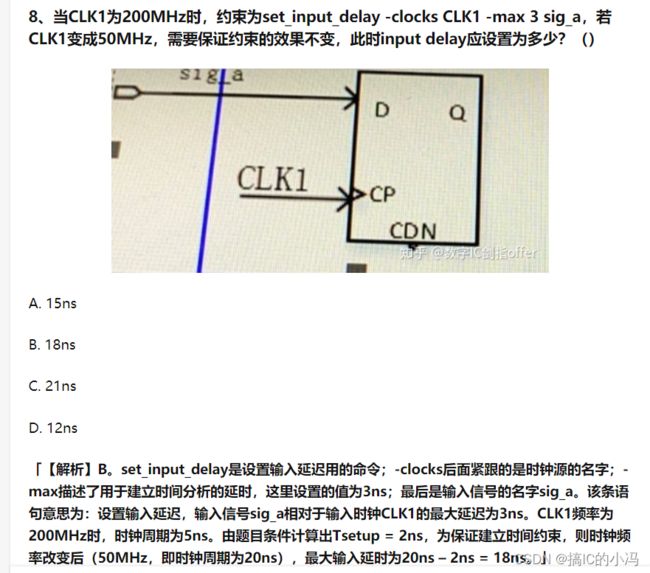

- 一些笔试选择题

前言

这是实验室师兄面试过程中整理的面试和笔试题目,目前只有题目,后续随着提前批和春招的进行,会慢慢填坑,也会把一些博主的题目搬运过来。

基本:笔试面试常出现,需弄透

-

基本逻辑运算、仅用与非或仅用与或非、最小项之和、最大项之积、卡诺图化简、逻辑门的mos管组成,笔试常出现

-

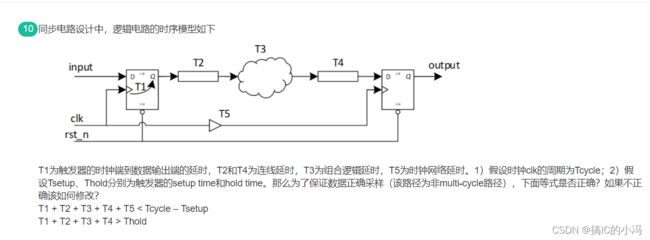

setup、hold time分析,需深入理解,而不是简单会计算,笔试甚至可能出几道问答题

-

FSM(二段三段式),百度面试中问过

-

CDC(快到慢及慢到快): 两级触发器,FIFO(同步异步),握手,笔试会考,面试基本都会问,问得很深,需彻底弄懂,要能写出代码

-

串并转换

-

分频电路(奇数分频,偶数分频),非常基础,华为面试中出现过,不会基本直接挂

-

乒乓buffer

-

超前进位加法器

-

booth乘法器

-

Wallace树,比特大陆笔试题

-

异步复位同步释放电路,OPPO面试中问过,问得比较深

-

脉冲同步器

-

序列检测,华为面试中问过

-

毛刺的成因(竞争冒险)、无毛刺时钟切换,OPPO面试中问过

-

verilog代码与综合后的电路的对应关系(例如if-else语句综合后电路,要能画出来),英伟达笔试题

-

被数整除,除法器,百度面试中问过

-

数字IC设计基本步骤,各个步骤常用软件,OPPO面试问过

加分:面试中偶尔问到

-

体系结构:五级流水、旁路、分支预测、cache,阿里、寒武纪面试问过

-

总线:AMBA2.0/4.0 AHB/AXI/AXI Stream(ARM spec),OPPO面试问过

-

验证方法学:UVM ,验证环境搭建,组成部分,OPPO面试问过

-

各类协议:DDR、PCIE、SPI、IIC

-

低功耗设计方法学、RISC等,常见低功耗设计方法需要知道,我记得面试问过,搞忘哪家了

自己要掌握的一些能力

- 脚本语言:Python、Perl脚本语言,能够开发相关脚本。TCL、Makefile语言,主要实现文本梳理(比如正则表达式)和流程控制。

- Linux操作:Linux下各种常见命令要熟练使用,能熟练使用VCS、Verdi、DC、gvim等开发工具。

常见的IC问题

DFT:可测性设计,插入用于测试的硬件逻辑,提高芯片的可测性。主要包括内部扫描、内建测试和边界扫描三种。

形式验证:保证综合后的网表功能与RTL一致,或者网表与版图的一致。静态验证的一种。

时序约束和分析:通过计算各通路的延迟,确保setup、hold、skew、clockfrequency等指标符合要求,并优化面积、功耗性能。包括STA静态时序分析DTA动态时序分析。

工具:

- 时序分析:PrimeTime

- Verilog/SystemVerilog编译仿真:VCS+Verdi/

- 形式验证 formality

- 综合工具:DC

- 各种工具的自动化:TCL脚本

- Linux自动化:SHELL/Python脚本

- 编译过程自动化:Makefile

- 文本处理等:Python/Perl

数字电路基础问题

参考链接

-

什么是冒险,什么是竞争,怎么消除

信号由于经由不同路径传输达到某一汇合点的时间有,先有后的现象,就称之为竞争。

同一线被不同值驱动称为冒险。

由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为竞争冒险。

FPGA设计中最简单的避免方法是尽量使用时序逻辑同步输入输出。

另外:加滤波电容,消除毛刺的影响- 加选通信号,避开毛刺

- 增加冗余项,消除逻辑冒险。

- 卡诺图化简与消除竞争冒险

参考

将卡诺图中相邻的未被圈的 数量为2^N的”1“圈起来。

-

系统最高速度计算(最快时钟频率)和流水线设计思想

同步电路的速度是指同步系统时钟的速度,同步时钟愈快,电路处理数据的时间间隔越短,电路在单位时间内处理的数据量就愈大。假设Tco是触发器的输入数据被时钟打入到触发器到数据到达触发器输出端的延时时间;Tdelay是组合逻辑的延时;Tsetup是D触发器的建立时间。假设数据已被时钟打入D触发器,那么数据到达第一个触发器的Q输出端需要的延时时间是Tco,经过组合逻辑的延时时间为Tdelay,然后到达第二个触发器的D端,要希望时钟能在第二个触发器再次被稳定地打入触发器,则时钟的延迟必须大于Tco+Tdelay+Tsetup,也就是说最小的时钟周期Tmin =Tco+Tdelay+Tsetup,即最快的时钟频率Fmax =1/Tmin。FPGA开发软件也是通过这种方法来计算系统最高运行速度Fmax。因为Tco和Tsetup是由具体的器件工艺决定的,故设计电路时只能改变组合逻辑的延迟时间Tdelay,所以说缩短触发器间组合逻辑的延时时间是提高同步电路速度的关键所在。由于一般同步电路都大于一级锁存,而要使电路稳定工作,时钟周期必须满足最大延时要求。故只有缩短最长延时路径,才能提高电路的工作频率。可以将较大的组合逻辑分解为较小的N块,通过适当的方法平均分配组合逻辑,然后在中间插入触发器,并和原触发器使用相同的时钟,就可以避免在两个触发器之间出现过大的延时,消除速度瓶颈,这样可以提高电路的工作频率。这就是所谓"流水线"技术的基本设计思想,即原设计速度受限部分用一个时钟周期实现,采用流水线技术插入触发器后,可用N个时钟周期实现,因此系统的工作速度可以加快,吞吐量加大。注意,流水线设计会在原数据通路上加入延时,另外硬件面积也会稍有增加。 -

impulse 和 pulse脉冲(前者为冲击响应,后者为脉冲响应)

-

逻辑表达式的化简

-

最小周期的计算(最大的主频)这里去要注意Tclk-q也被称为clock output delay,被叫做Tco

-

奇偶校验在硬件上该怎么搞(异或就可以了)

-

门电路的与非门、或非门、二选器转化

-

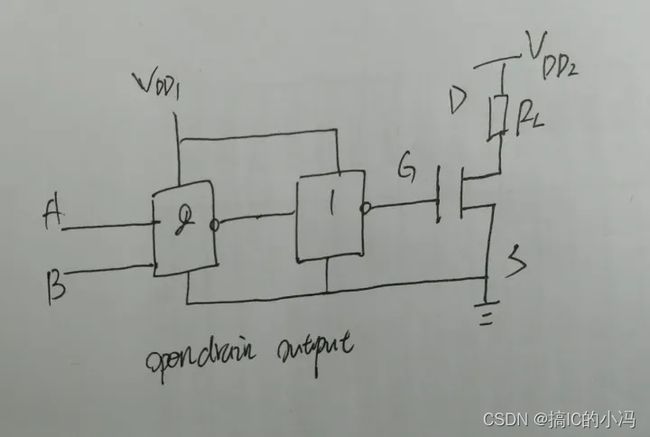

什么是open-drain output?

Open-Drain Output漏极开路输出,称为OD门,两个OD门并联可以实现线与功能,输出端外接的上拉电阻提高驱动能力

-

锁存器(latch)和触发器(flip-flop)区别:

电平敏感的存储器件称为锁存器。可分为高电平锁存器和低电平锁存器,用于不同时钟之间的信号同步。有交叉耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发。可以认为是两个不同电平敏感的锁存器串连而成。前一个锁存器决定了触发器的建立时间,后一个锁存器则决定了保持时间。

-

IC设计过程中将寄生效应的怎样反馈影响设计师的设计方案

所谓寄生效应就是那些溜进你的PCB并在电路中大施破坏、令人头痛、原因不明的小故障。它们就是渗入高速电路中隐藏的寄生电容和寄生电感。其中包括由封装引脚和印制线过长形成的寄生电感;焊盘到地、焊盘到电源平面和焊盘到印制线之间形成的寄生电容;通孔之间的相互影响,以及许多其它可能的寄生效应。理想状态下,导线是没有电阻,电容和电感的。而在实际中,导线用到了金属铜,它有一定的电阻率,如果导线足够长,积累的电阻也相当可观。两条平行的导线,如果互相之间有电压差异,就相当于形成了一个平行板电容器(你想象一下)。通电的导线周围会形成磁场(特别是电流变化时),磁场会产生感生电场,会对电子的移动产生影响,可以说每条实际的导线包括元器件的管脚都会产生感生电动势,这也就是寄生电感。

在直流或者低频情况下,这种寄生效应看不太出来。而在交流特别是高频交流条件下,影响就非常巨大了。根据复阻抗公式,电容、电感会在交流情况下会对电流的移动产生巨大阻碍,也就可以折算成阻抗。这种寄生效应很难克服,也难摸到。只能通过优化线路,尽量使用管脚短的SMT元器件来减少其影响,要完全消除是不可能的。

-

你知道那些常用逻辑电平?TTL与COMS电平可以直接互连吗?

常用逻辑电平:TTL、CMOS、LVTTL、LVCMOS、ECL(Emitter Coupled Logic)、PECL(Pseudo/Positive Emitter Coupled Logic)、LVDS(Low Voltage Differential Signaling)、GTL(Gunning Transceiver Logic)、BTL(Backplane Transceiver Logic)、ETL(enhanced transceiver logic)、GTLP(Gunning Transceiver Logic Plus);RS232、RS422、RS485(12V,5V,3.3V);也有一种答案是:常用逻辑电平:12V,5V,3.3V。

TTL和CMOS 不可以直接互连,由于TTL是在0.3-3.6V之间,而CMOS则是有在12V的有在5V的。CMOS输出接到TTL是可以直接互连。TTL接到 CMOS需要在输出端口加一上拉电阻接到5V或者12V。

用CMOS可直接驱动TTL;加上拉电阻后,TTL可驱动CMOS.

-

高阻态的意义和用法

- 该点输入电阻(输出电阻)无穷大,相当于断路,管角悬空,既不是高电平也不是低电平,其电平随外部电平高低而定。

- 应用实例1:在总线连接的结构上。总线上挂有多个设备,设备与总线以高阻的形式连接。这样在设备不占用总线时自动释放总线,以方便其他设备获得总线的使用权。

- 应用实例2:大部分单片机I/O使用时都可以设置为高阻输入,如STM32,AVR等等。高阻输入可以认为输入电阻是无穷大的,认为I/O对前级影响极小,电平随外部电平高低而定,除了高电平/低电平还能读中间的值,可用于AD连接。

-

什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求?

线与逻辑是两个输出信号相连可以实现与的功能。在硬件上,要用oc门来实现,由于不用oc门可能使灌电流过大,而烧坏逻辑门. 同时在输出端口应加一个上拉电阻。oc门就是集电极开路门。od门是漏极开路门。 -

mealy机和Moore机的区别

- Moore状态机的输出仅与当前状态值有关,且只在时钟边沿到来时才会有状态变化。

- Mealy状态机的输出不仅与当前状态有关,而且与当前输入值有关。

-

用CMOS搭建逻辑门(注意可以只用与非门or或非门or二选来搭建任意的门电路)

-

CMOS反相器的功耗(注意背一下静态功耗,是扩山区和衬底之间的反向偏执电流引起的)

-

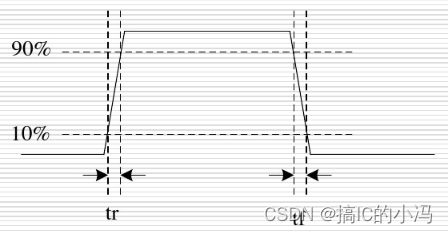

反相器的翻转时间(也叫transition time)和传播时间(propagation time)

-

基本逻辑运算

~(a ^ b) = (a & b) | (~a & ~b); a ^ b = (~a & b) | (a & ~b) -

格雷码与独热码

格雷码:相邻之间只变1bit,编码密度高。功耗低;可用于CDC。状态机中可节省状态寄存器,适合写适合写条件不复杂但是状态多的状态机。;

独热码:任何状态只有1bit为1,其余皆为0,编码密度低。但译码方便,节省组合逻辑;稳定性强,任意1bit错误都不会产生毛刺,适合写条件复杂但是状态少的状态机;(对于FPGA,可用资源数固定,资源足够就用独热码)

- 二进制与格雷码的转换

- 自然二进制码转换成二进制格雷码,其法则是保留自然二进制码的最高位作为格雷码的最高位,而次高位格雷码为二进制码的高位与次高位相异或,而格雷码其余各位与次高位的求法相类似。实际操作时将只需将二进制码右移一位再与原值异或就行。只需一行代码:

assign graydata = (bindata >> 1) ^ bindata;保留格雷码的最高位作为自然二进制码的最高位,二进制码的次高位为格雷码的次高位与二进 制码的(次高位+1)进行异或,其余各位采用类似的方法。代码如下:

assign {bindata[7],bindata[6:0]}={graydata[7],bindata[7:1]^bindata[6:0]}

Verilog & SV

- 阻塞和非阻塞赋值的区别

- 非阻塞赋值在触发调节满足是,两条语句是同时进行的,一般时序逻辑用非阻塞赋值

- 阻塞赋值是顺序执行的,一般组合逻辑用阻塞赋值

- localparam , parameter , define的区别

| localparam | parameter | define | |

|---|---|---|---|

| 作用域 | 当前module | 当前module | 整个工程 |

| 参数传递 | 不可以 | 可 | 可 |

| 重定义 | 不可以 | defparameter | undef失效 |

注释:parameter如果在模块内部定义时视为localparam,无法进行参数传递,在模块名后写可以传递可以defparameter.

- task和function的区别

| task | founction | |

|---|---|---|

| 定义 | 任务不能出现always语句;可以包含延时控制语句(#),事件控制@等,但只能面向仿真,不能综合(可综合的任务只能实现组合逻辑) | 函数定义不能包含任何的时间控制语句,即#、@或者wait |

| 包含 | task可以包含其它的task和function。 | function不能包含task |

| 输入 | task可以没有或者有多个任意类型的变量 | function至少有一个输入变量 |

| 返回 | task则不返回值,也可以通过输出端口或双向端口返回一个或多个值 | function返回一个值,在函数的定义中,必须有一条赋值语句给函数中的一个内部变量赋以函数的结果值,该内部变量与函数具有相同的名字 |

| 调用 | 任务调用语句可以作为一条完整的语句出现 | 函数调用语句不能单独作为一条语句出现,只能作为赋值语句的右端操作数 |

-

连续赋值assign与always过程赋值

-

在连续赋值语句中,表达式右侧的计算结果可以立即更新表达式的左侧。在理解上,相当于一个组合逻辑之后直接连了一条线,这个逻辑对应于表达式的右侧,而这条线就对应于wire。

-

在过程赋值语句中,表达式右侧的计算结果在某种条件的触发下放到一个变量当中,而这个变量可以声明成reg类型。根据触发条件的不同,过程赋值语句可以建模不同的硬件结构:如果这个条件是时钟的上升沿或下降沿,那么这个硬件模型就是一个触发器;如果这个条件是某一信号的高电平或低电平,那么这个硬件模型就是一个锁存器;如果这个条件是赋值语句右侧任意操作数的变化,那么这个硬件模型就是一个组合逻辑。

-

-

wire和reg类型的区别

- 基本概念的差别

wire型数据常用来表示以assign关键字指定的组合逻辑信号,模块的输入输出端口类型都默认为wire型**,wire相当于物理连线,默认初始值是z**。

reg型表示的寄存器类型,用于always模块内被赋值的信号,必须定义为reg型,代表触发器,常用于时序逻辑电路,reg相当于存储单元,默认初始值是x。 - 在赋值语句中的差别

在连续赋值语句中,表达式右侧的计算结果可以立即更新表达式的左侧。在理解上,相当于一个逻辑之后直接连了一条线,这个逻辑对应于表达式的右侧,而这条线就对应于wire。

在过程赋值语句中,表达式右侧的计算结果在某种条件的触发下放到一个变量当中,而这个变量可以声明成reg类型。根据触发条件的不同,过程赋值语句可以建模不同的硬件结构:如果这个条件是时钟的上升沿或下降沿,那么这个硬件模型就是一个触发器;如果这个条件是某一信号的高电平或低电平,那么这个硬件模型就是一个锁存器;如果这个条件是赋值语句右侧任意操作数的变化,那么这个硬件模型就是一个组合逻辑。

总而言之,wire只能被assign连续赋值,reg只能在initial和always中赋值 - 端口信号和内部信号的差别

信号可以分为端口信号和内部信号。出现在端口列表中的信号是端口信号,其它的信号为内部信号。

对于端口信号,一旦定义位input或者output端口,默认就定义成了wire类型,输入端口只能是net类型(wire/tri)。输出端口可以是net类型,也可以是reg类型。若输出端口在过程块中赋值则为register类型;若在过程块外赋值(包括实例化语句),则为net类型。

内部信号类型与输出端口相同,可以是net或reg类型。判断方法也与输出端口相同。若在过程块中赋值,则为reg类型;若在过程块外如assign赋值,则为net类型。

若信号既需要在过程块中赋值,又需要在过程块外赋值。这种情况是有可能出现的,如决断信号。这时需要一个中间信号转换。

inout是一个双向端口, inout端口不能声明为reg类型,只能是wire类型。

- 基本概念的差别

-

系统函数

- clog2函数

$clog2返回2为底的向上取整的对数,用于计算位宽。 $signed和$unsigned。

首先明确这两个语句是可综合的。$signed(c)是一个function,将无符号数c转化为有符号数返回,不改变c的类型和内容。接上述代码历程:$unsigned同理。

- clog2函数

-

顺序块和并行块

- 顺序块(也称过程块)

关键字begin_end

顺序块中的语句一条条按顺序执行,只有前面语句执行完才执行后面的语句(除了带有内嵌延时控制的非阻塞赋值语句)。

如果语句包括延时或事件控制,那么延迟总是相对于前面那条语句执行完成的仿真时间的 - 并行块(不可综合)

关键字fork_join

并行块内的语句是并发执行的;

语句的执行的顺序是由各自语句内延迟或事件控制决定的

语句中的延迟或事件控制是相对于块语句开始执行的时刻而言的。 - 可以嵌套

- 顺序块(也称过程块)

跨时钟域信号处理类

跨时钟域处理方法总结–最终详尽版

-

同步电路和异步电路的区别:

- 同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。

- 异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

sky课件

- 同步时钟:能够明确定义多个时钟间时钟频率、时钟高/低电平持续时间、各个时钟得相位、时钟得输入Latency的时钟源。

- 不能明确定义多个时钟间以上关系的时钟源。

菜鸟教程 喜欢这个回答 - 同步时钟:一般认为,频率相同或频率比为整数倍、且相位相同或相位差固定的两个时钟为同步时钟。或者理解为,时钟同源且频率比为整数倍的两个时钟为同步时钟。其实,时钟同源,就保证了时钟相位差的固定性。

- 异步时钟:不能保证时钟源、频率、相位关系的时钟。

-

对于多位的异步信号如何进行同步?

- 对以一位的异步信号可以使用“一位同步器进行同步”(使用两级触发器)

- 而对于多位的异步信号,可以采用如下方法:

1:可以采用保持寄存器加握手信号的方法(多数据,控制,地址);

2:特殊的具体应用电路结构,根据应用的不同而不同;

3:异步FIFO。(最常用的缓存单元是DPRAM)

-

亚稳态的定义是什么;

时序逻辑在跳变时,由于异步信号、跨时钟域等原因,不满足setup或hold条件,输出在0和1之间产生振荡。 -

什么是亚稳态,产生的原因,怎么消除(触发器无法在某个规定时间段内达到一个确定的状态)

- 是什么

时序逻辑在跳变时,由于异步信号、跨时钟域等原因,不满足setup或hold条件,输出在0和1之间产生振荡。 - 原因

- 是什么

-

为什么两级触发器可以防止亚稳态传播? (打两拍)

使用两级触发器来使异步电路同步化的电路其实叫做“一位同步器”,他只能用来对一位异步信号进行同步。两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。同步器有效的条件:第一级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 < = 时钟周期。更确切地说,输入脉冲宽度必须大于同步时钟周期与第一级触发器所需的保持时间之和。最保险的脉冲宽度是两倍同步时钟周期。 所以,这样的同步电路对于从较慢的时钟域来的异步信号进入较快的时钟域比较有效,对于进入一个较慢的时钟域,则没有作用 。

-

MTBF(平均失效间隔时间)的概念;

触发器进入亚稳态的时间可以用参数 MTBF(mean time between failures)来描述, MTBF即触发器采样失败的时间间隔,其公式描述如下:

M T B F = e t r / τ / T 0 f a MTBF=e^{{tr}/{τ}} /T_0fa MTBF=etr/τ/T0fa

其中- t r = t_r= tr= 分辨时间(时钟沿开始)

- τ , T 0 = τ,T_0= τ,T0= 触发器参数

- f = f= f=采样时钟频率

- a = a= a= 异步事件触发频率

通常,MTBF越大说明系统采样失败的可能越小。可见,对于高速的设计,MTBF是更容易发生的。

-

同步电路与异步电路的比较;

-

两级DFF同步器的原理和代码,以及输入窄脉冲情况下的变化;

-

握手协议进行同步的原理和代码,并与方法4)在资源、速度、适用情况等方面进行比较;

-

异步FIFO里为什么要用格雷码?

参考链接 -

异步FIFO的原理和代码,包括为什么需要同步读写指针,为什么要用格雷码,满空状态如何判断,为什么会有假满假空现象以及会对系统产生什么影响,FIFO深度如何选择等等;

-

异步复位同步释放的原理和代码,以及比较异步复位和同步复位的优缺点;

参考链接 -

解决亚稳态

- 降低系统时钟

- 用更快的FF

- 引入同步机制,防止亚稳态传播

- 改善时钟质量

- 流水线

CRG 同步与异步复位

这里有一篇关于写复位的文章,建议读一下:

FPGA-xilinx系列芯片的复位,你真的明白吗?

-

同步复位的优点大概有3条:

a、有利于仿真器的仿真。

b、有利于时序分析,而且综合出来的fmax一般较高。

c、只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺。

缺点主要有以下几条:

a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时还要考虑,诸如:clk skew,组合逻辑路径延时,复位延时等因素。

b、FPGA内寄存器中支持异步复位专用的端口CLR,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。 -

对于异步复位来说,他的优点也有三条:

a、大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源。

b、设计相对简单。

c、异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。

缺点:

a、在复位信号释放(release)的时候容易出现问题。具体就是说:倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致亚稳态。

b、复位信号容易受到毛刺的影响。 -

异步复位同步释放电路

同步复位和异步复位都不可靠,将两者结合,取长补短,既解决了同步复位的资源消耗问题,也解决了异步复位的亚稳态问题。其根本思想,也是将异步信号同步化。

always @ (posedge clk) rst_n <= a_rst_n; //关键:异步复位信号用同步时钟打一拍(也可以多拍) always @ (posedge clk or negedge rst_n) if(!rst_n) b <= 1'b0; else b <= a; always @ (posedge clk or negedge rst_n) if(!rst_n) c <= 1'b0; else c <= b; /*另一种写法*/ //Synchronized Asynchronous Reset module sync_async_reset(clock,reset_n,data_a,data_b,out_a,out_b); input clock, reset_n; input data_a, data_b; output out_a, out_b; reg rst_nr, rst_n; reg out_a, out_b; always @(posedge clock or negedge reset_n) begin if(!reset_n) begin rst_nr <= 1'b0; rst_n <= 1'b0; //异步复位 end else begin rst_nr <= 1'b1; rst_n <= rst_nr; //同步释放 end end //信号rst_n作为新的总的复位信号,后续可以以“异步”做复位使用 always @(posedge clock or negedge rst_n) begin if(!rst_n) begin out_a <= 1'b0; out_b <= 1'b0; end else begin out_a <= data_a; out_b <= data_b; end end endmodule // sync_async_reset

综合与时序分析类

这个分类不是特别严谨,我的理由是用DC做综合或者用PT做时序分析都是在服务器的环境下,所以就放在一起了。一个数字IC设计工程师应该要能够借助这两个工具评估自己的设计。

- ASIC设计流程,从spec到GDSII的全过程,以及每一步的意义和工具;

- 综合的概念,以及主要操作步骤;

- 综合的常用脚本,包括创建原时钟、分频时钟,设置时钟参数等等;

- Setup time和Hold time的概念;

- 静态时序分析(STA)的概念和优缺点;

- 用PT做STA所需要的数据和脚本,以及弄懂PT时序分析报告上的信息;

- 时钟抖动(jitter)和时钟偏移(skew)的概念,以及他们对时序分析的影响(更严格还是更宽松了)?

参考答案- 抖动是时钟频率的变化,指的是时钟周期的变化。也即相对于理想时钟沿产生的不随时间积累的、时而超前、时而滞后的偏移。

- 偏移是时钟相位上的不确定,由于时钟源到达不同寄存器所经历路径的驱动和负载的不同,时钟边沿的位置有所差异。

- 对一个“输入-DFF-组合逻辑-DFF-输出”的一个典型系统进行时序分析,计算该系统的最大运行频率(最小周期);

- 如何修复Setup违例和Hold违例;

低功耗方法

- 集成电路中功耗的来源;

- 动态功耗与哪些参数有关,开关功耗的公式,以及静态功耗与哪些参数有关;

- ASIC中低功耗的方法

- SoC系统中常用的低功耗技术,从体系结构级到器件工艺级都要能列出一种,比如划分不同电压域、时钟域,使用不同阈值的器件等等;

- RTL级的低功耗设计方法,重点是门控时钟,包括基于与门和基于锁存器的门控时钟结构的代码和优缺点比较;

- 低功耗处理方法

- 处理好门控时钟,不用的时候给关了

- 数据通路上的Reg不复位

- 多个电源区域

- 关闭某些区域的电源

- 划分好时钟频率

- 什么是Clock Jitter和Clock Skew(布线长度和负载)

时钟抖动(Clock Jitter):指芯片的某一个给定点上时钟周期发生暂时性变化,使得时钟周期在不同的 周期上可能加长或缩短

时钟偏移(Clock Skew):是由于布线长度及负载不同引起的,导致同一个时钟信号到达相邻两个时序 单元的时间不一致。

区别:Jitter是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。Skew是由 不同布线长度导致的不同路径的时钟上升沿到来的延时不同。

STA(静态时序分析)

安利一波邸老师的课:数字集成电路静态时序分析基础

STA – Setup time & Hold time 详细解读

- 建立时间保持时间关系详解

- 从CMOS到建立时间和保持时间

- 建立时间保持时间经典题目

两篇总结的很好的时序约束的文章:

- 八小时超长视频教你掌握FPGA时序约束!

- 时序约束策略

- SDC synthesis design constraint

- setup time 和 hold time 和 recovery time 和 removal time (这两个是针对复位而言的)还有minimum pluse width。。。

- 时序设计的实质:

时序设计的实质就是满足每一个触发器的建立/保持时间的要求。 - 建立时间与保持时间的概念

建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。

保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。 - 为什么触发器要满足建立时间和保持时间?

因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。

(比较容易理解的方式)换个方式理解:需要建立时间是因为触发器的D端像一个锁存器在接受数据,为了稳定的设置前级门的状态需要一段稳定时间;需要保持时间是因为在时钟沿到来之后,触发器要通过反馈来锁存状态,从后级门传到前级门需要时间。(可以看sky网课ppt)

RTL设计(包含手撕代码)

笔试环节手撕代码的公司不少,状态机的设计方法一定要熟练

- 输入一个8bit的数,输出其中1的个数(使用全加器和加法器,至少使用7个全加器)

- 跨时钟域处理

- 单bit(由慢到快,由快到慢,脉冲间距够长,脉冲间距不够长),这里我说明一下,如果是握手的话,就不需要使用脉冲展宽了

- 多bit

- **串并转换(握手加移位逻辑)**牛客网上有

- 计数器

参考链接- 普通的计数器

- 环形计数器

- Jonhson计数器(扭环计数器)

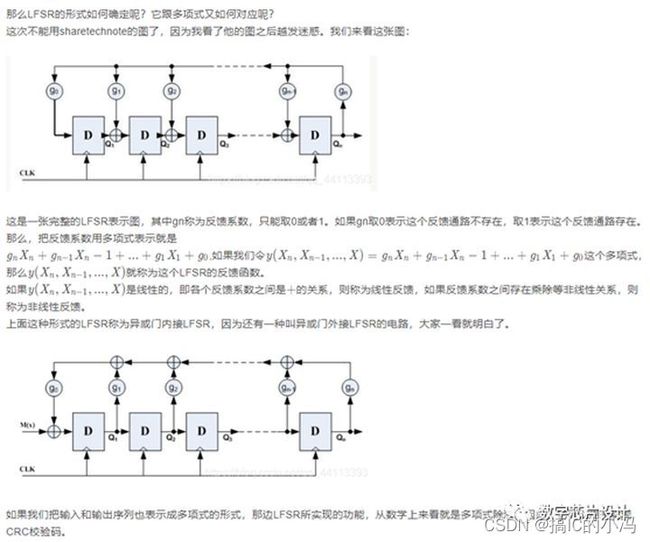

- LFSR

- 序列检测器(序列可以是单bit的,也可以是多bit的)FSM或者移位寄存器加比较的方式来实现

参考链接 - 序列发生器(可以用状态机,也可以用移位寄存器,还可以化简卡诺图用计数器加一些组合逻辑的方式来搞)参考链接

- 关于分频

偶数分频很简单,一个计数器,输出高电平占一半,低电平也占一半

而奇数分频由于除以2除不尽,因此,需要使用两个计数器,产生两个占空比为40%的信号,但一个采集上升沿,一个采集下降沿,最后利用相位差,产生一个奇分频的信号,而对于2的整数次幂的分频电路就有意思了,它可以直接使用串联的回路型D触发器,这就是得2分频用一个FF,4分频用2个D,8分频用3个D。N分频用log2(N)个D。- 偶数分频,奇数分频(分为占空比为0.5和非0.5两种情况),★小数分频

- 奇数分频电路的代码,包括两种情况:使用带负沿触发的DFF(要求占空比50%),不使用带负沿触发的DFF;

- 按键消抖,延迟时间计算为(F*t),但需要注意的是不光按键按下需要消抖,按键松开也需要消抖

- 同步FIFO和异步FIFO

- 有符号的数值比较器

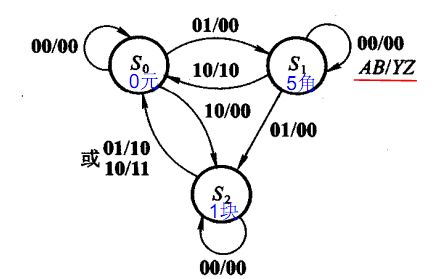

- 红绿灯的FSM

- 自动售货机的两种形式

-

设计一个自动饮料售卖机,饮料10分钱,硬币有5分和10分两种,并考虑找零

1.画出fsm(有限状态机)

2.用verilog编程,语法要符合FPGA设计的要求

3.设计工程中可使用的工具及设计大致过程?- 设计过程:

1、首先确定输入输出,A=1表示投入10分,B=1表示投入5分,Y=1表示弹出饮料,Z=1表示找零。

2、确定电路的状态,S0表示没有进行投币,S1表示已经有5分硬币。

3、画出状态转移图。

- 设计过程:

-

设计一个自动售饮料机的逻辑电路。它的投币口每次只能投入一枚五角或一元的硬币。投入一元五角硬币后给出饮料;投入两元硬币时给出饮料并找回五角。

input nickel、dimemodule sell(clk,rst,a,b,y,z); input clk,rst,a,b; output y,z; parameter s0=0,s1=1; reg state,next_state; always@(posedge clk) begin if(!rst) state<=s0; else state<=next_state; end always@(a or b or cstate) begin y=0;z=0; case(state) s0: if(a==1&&b==0) next_state=s1; else if(a==0&&b==1) begin next_state=s0; y=1; end else next_state=s0; s1: if(a==1&&b==0) begin next_state=s0; y=1; end else if(a==0&&b==1) begin next_state=s0; y=1; z=1; end else next_state=s0; default: next_state=s0; endcase end endmodule

output serve、change -

- round robine arbiter 这个考察比较多

可以看Matt Weber, "Arbiters: Design Ideas and Coding Styles"论文翻译与复现 - sort8以及从最大的几个数里选出来最大或最小的数

- 超前进位加法器

- 帧头检测 frame_head来脉冲的同时din会来数据,连续三次数据都是8’h23的话,就输出一个脉冲

- 数据包的抓取

- 被3整除的问题

参考链接 - 华莱士树(w和Booth两位一乘的乘法器

乘法器Booth算法

- 最大公约数的算法

- 毛刺时钟切换电路的代码

- 写一段verilog消除glitch

参考链接

正常情况下数据包由起始码(16bit)、数据段(n byte n<256)、结束码(16bit)3部分组成。起始码为0xFF00,结束码为0xFF01。在一个完整数据包中,数据段部分不会出现起始码和结束码。请设计一个电路在码流中检测完整且有效的数据包,并输出当前数据包的有效数据长度n。 输入数据接口input clk,rst_n,din[7:0],din_vld output data_cnt[7:0],data_cnt_vld

总线问题

本人项目和总线Arbiter有关,所以这方面应该多下点功夫才好。

AXI

- 五个通道的描述

- 握手的依赖关系

- burst传输的计算

- burst中len是传多少次,size是每次传多大

- 什么是outstanding

outstanding是一种超前传输机制,在没有使用outstanding的时候,读地址发出去了之后,一定要在数据回来了之后,才能进行下一步的操作。但使用outstanding机制了之后,可以通过读地址通道连续发起多个读事务,返回的数据也可以乱序返回,数据识别的标识就是各个通道的ID(WID在AXI4中被取消)

对于 ARID 一致的多个事务,从机必须按照接收事务的顺序,返回其读数据。

具有不同 ARID 的事务之间可以乱序(no ordering restrictions)

APB

AMBA总线(一)

AMBA总线(二)

- APB总线的基本结构

- APB总线执行的大致时序

- APB总线执行的状态机

- 关于APB基础知识

- pselx

- penable

- pwrite

- paddr

- pstrb 懂的都懂

- pwdata

- prdata

- pready

- pslverr //slave error 当从机出错的时候,这玩意儿会被拉高

- APB只有写的控制信号,使用的是pselx,这里的x代表的是第几个选通信号,也就是说,有多少个外设,就有多少个选通信号,而penable是一个总使能,其中pwrite信号为高时就是写,为低的时候就是读。因此AXILite数据和地址过来了之后,先放到FIFO中,然后对addr进行译码得到pselx拉高的地方

- 在转接的过程中需要跨时钟域传递两个信息,DATA,addr,write/read把三个合在一起,一共需要32+32+1 ,65位的数据宽度,至于它们的深度,由于写的速度差不多是读的速度的10倍(周期都差不太多),因此write fifo的深度为16,而read fifo由于是从慢速到高速,因此深度为1即可

- 为了满足各种速度的外设,APB还是支持握手的。

- 整个APB的传输过程有三个状态: IDLE 、SETUP、ACCESS(这个时候PENABLE才拉高)

- 只有当从机给了pready之后,ACCESS状态才能跳转回IDLE状态

AHB

- 基本的几条线路

- haddr

- hwrite(高电平时为write,低电平时为read)

- hrdata

- hready

- 扩展使用的

- htrans(用于表明当前传输的类型,说白了就是master用于控制当前的一种传输状态,IDLE、BUSY、NONSEQ、SEQ)

- hprot

- 用于burst的线路(不像axi,这里没有len,它的连续性由htrans这一组线来控制)

- hsize

- hburst

这个总线是可以进行流水化的

体系结构的问题

这部分的内容稍微有点偏向专用领域,但是平头哥和比特大陆等公司的笔试题里出现了不少相关内容。

- 流水线的好处,流水线带来的问题,几种相关性该怎么解决

- 相关性的类型和解决方案

- 控制相关

- 数据相关(RAW、WAR、WAW)

- 结构相关

- 怎样实现流水线的停顿

- ALU的结构

- 异常的实现(RISCV的异常处理流程)

- 五级流水线的基本描述

- Cache相关问题

- 基本的逻辑结构

- 能够完成地址划分和相关的计算

- FRV32中的Cache(load hit/miss、store hit/miss相关的行为)

- 性能评估

- 性能优化方法

- OoO

- Tomasolu算法+ROB(把龙芯二号的流水线给背下来,普通的保留站方案也背下来)

- 分支预测技术(BHT、BTB、RAS的基本原理)

- 虚实地址的转化过程(Linux中一条指令的执行流程)

- TLB的翻译过程和执行的思路

- VIPT需要规避的问题

- 计算机中使用补码的意义;

- 超前进位加法器的原理和代码

- 小数定点化的概念,包括对于一个确定的十进制小数,需要多少bit才能无损定点化;

- 基于IEEE-754标准的浮点数的表示;

- 计算机中的乘法和除法如何计算的(只需知道最简单的方法);

- 流水线设计的作用和优缺点;

- 处理器中结构冒险、数据冒险、控制冒险的概念和解决机制;

- cache的映射方法和写回策略有哪些;

- 谈谈对Retiming技术的理解

Retiming就是重新调整时序,例如电路中遇到复杂的组合逻辑,延迟过大,电路时序不满足,这个时候采用流水线技术,在组合逻辑中插入寄存器加流水线,进行操作,面积换速度思想。

RISCV的问题

- RISCV指令的总体结构

- 没有超过两个操作数的指令(读端口最多就是2个)

- 指令及其整齐,位置几乎是一样的(func7_rs2_rs1_func3_rd_op)

- RISCV的压缩指令特点(最低两位的问题)

- 异常处理流程

- PLIC和CLIC

- RISCV的虚实地址的转化过程

- 异常的分类