注:这篇是本人原创于2009年11月的一篇关于Modelsim仿真的文章,当时在使用新浪博客,后来发现博客园更加适合我就停止了原新浪博客的更新。今天使用Modelsim想起了这篇文章就移到此博客中,图片内的链接就不修改了……

软件版本:Modelsim SE PLUS 6.5http://www.cnblogs.com/Efronc

前言:

为了搞清Modelsim加载altera仿真库的问题我已经足足查了两天资料,这篇文章是我第一天写的,当时有些地方只是会做,可是为什么这样做就不是很了解了。经过昨天一天的努力,现在基本上明白了整个过程。对这篇文章进行整体的完善和补充(本人水平有限,如有错误请留言指正)。

http://www.cnblogs.com/Efronc

用Modelsim对Quartus II工程进行时序仿真(在此只讨论时序仿真)可分两种方式:一种是在Quartus II中设置run gate-level simulation automatically after compilation,在Quartus II布局布线后自动调用Modelsim,通过do文件自动完成仿真过程之间显示波形;另一种方式是自己启动Modelsim进行时序仿真。第一种方式Quartus II自动完成库的编译、添加和调用,第二种方式则需要自己添加altera仿真库(也可以把库文件跟仿真激励等一起编译,但是work库正大量资源库的模块用起来很不方便)。

下面我将以附录中简单的Verilog例子分三大部分由浅入深的介绍利用Modelsim进行时序仿真。

第一部分介绍Quartus II自动调用Modelsim进行时序仿真的操作过程;第二部分介绍altera仿真库(Verilog)的添加操作过程;第三部分简单的介绍一下Modelsim库的概念,分析一下Quartus II自动完成仿真的代码,最后能自己写一些简单的do文件利用我们添加的仿真库自动进行时序仿真。前两个部分是简单的操作,掌握其中一个部分即可进行时序仿真。最后一部分是代码的分析及利用,如有需要,请参考。

一.Quartus II自动调用Modelsim进行时序仿真

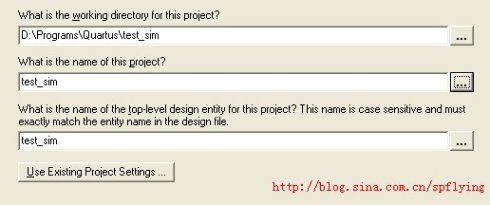

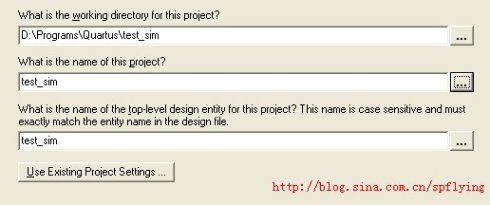

1.Quartus II 下建立新的工程test_sim;

2.编写Verilog代码

包括test_sim工程文件和sim仿真激励文件,保存在工程目录下的src文件夹中。

注意仿真激励文件不要添加进工程。代码如附录;

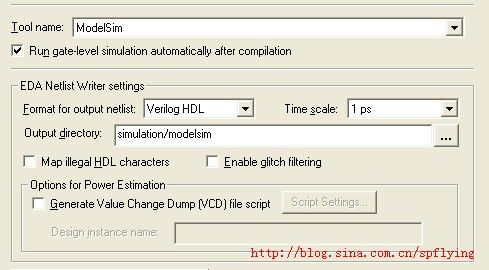

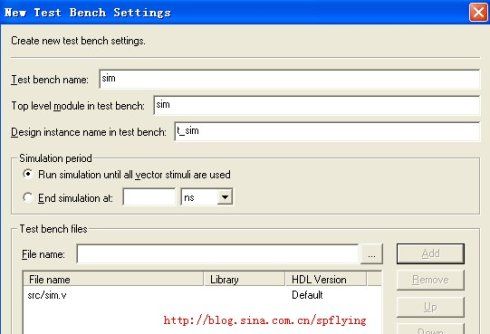

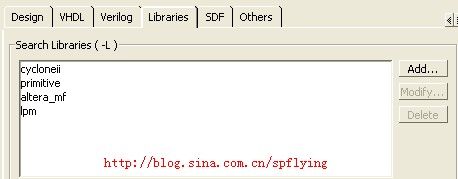

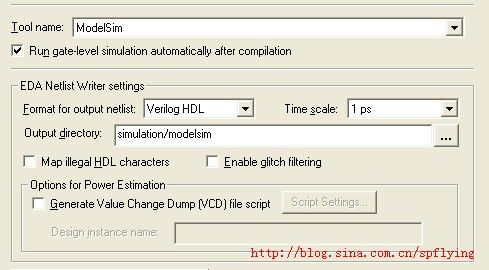

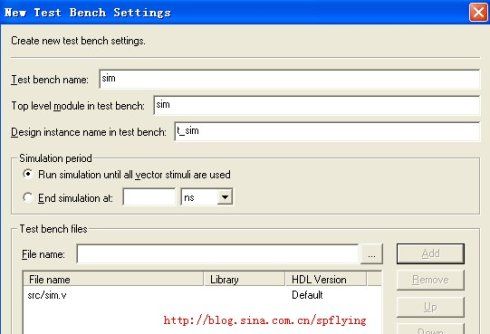

3.设置EDA tool settings>simulation

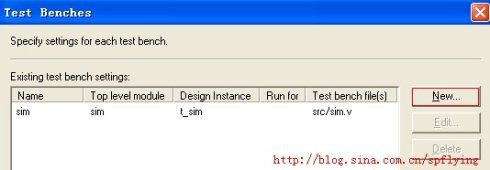

如图所示:

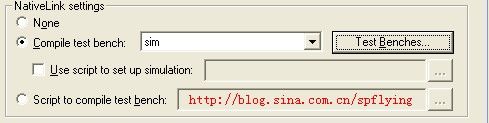

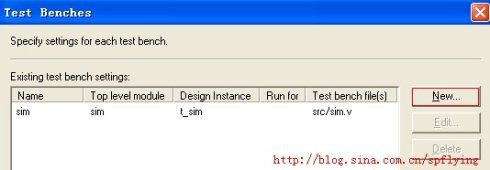

4.设置nativelink settings

如图所示:

5.点击Start compilation进行全编译,Quartus II自动完成仿真。

注:自动启动Modelsim需要在tool>options>EDA tool options下设置Modelsim安装路径。

二.Altera仿真库(Verilog)的添加

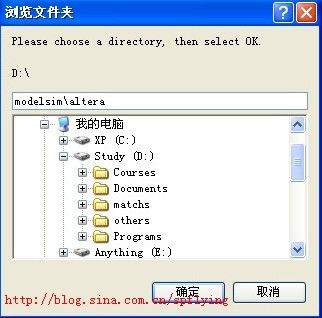

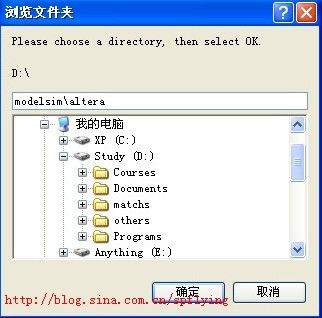

1.设置工作路径http://www.cnblogs.com/Efronc

打开modelsim安装目录(我的modelsim安装在d:/modelsim目录下),新建文件夹altera。后面的步骤将在该目录下的primitive、altera_mf、lpm、cycloneii文件夹下存放编译的库。

启动Modelsim SE仿真工具,在主窗口中选择【file】→【change directory】命令将路径转到altera文件夹。或者在命令行中执行cd D:/modelsim/altera命令。

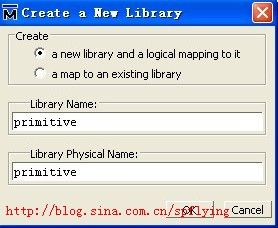

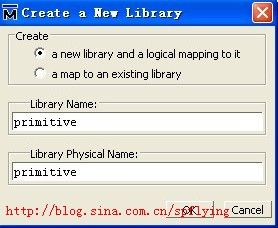

2.新建库http://www.cnblogs.com/Efronc

在主窗口中选择【file】→【new】→【library】命令,新建一个名为primitive的库。

3.查找编译资源库所需文件http://www.cnblogs.com/Efronc

在Quartus II安装目录下找到quartus\eda\sim_lib文件夹,用于编译资源库的文件有220model.v,220model.vhd,220pack.vhd,altera_mf.v,altera_mf.vhd,altera_mf_components.vhd,altera_primitives.v,altera_primitives.vhd,altera_primitives_components.vhd,cycloneii_atoms.v,cycloneii_atoms.vhd,cycloneii_components.vhd文件。方便起见把它们复制到altera下src文件夹下。

网上的很多教程都是把这些文件一起编译,这样适用于Verilog和VHDL混合仿真,但如果只用一种语言,如Verilog则完全没必要全部编译。这几个文件可分为Verilog组:220model.v、altera_mf.v、altera_primitives.v、cycloneii_atoms.v和VHDL组:220model.vhd、220pack.vhd、altera_mf.vhd、altera_mf_components.vhd,altera_primitives.vhd,altera_primitives_components.vhd,cycloneii_atoms.vhd,cycloneii_components.vhd。

编译时根据需要编译一组或全部编译。下面以Verilog组为例,首先编译primitive库。

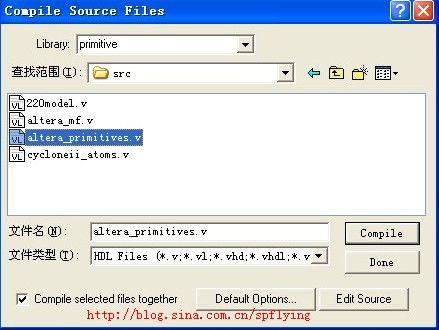

4. 编译库 http://www.cnblogs.com/Efronc

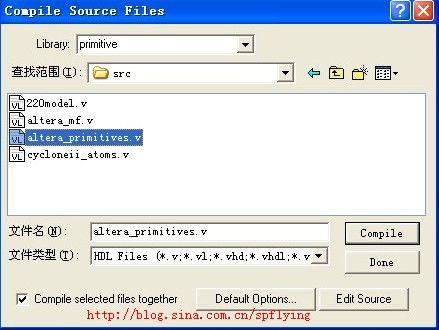

在主菜单中选【compile】→【compile】命令,对altera_primitives.v进行编译。

VHDL文件编译有所不同,LPM库的220model.vhd和220pack.vhd可以同时编译,MegaFunction库的先编译altera_mf_components.vhd文件,后编译altera_mf.vhd文件,Primitiv库先编译altera_primitive_components.vhd文件,后编译altera_primitive.vhd文件,元件库,如cyclone II库先编译cycloneii_atoms.vhd文件,后编译cycloneii_components.vhd文件,如果是其他系列的元件库则只要把对应的cycloneii改成其他系列的名称即可,如cyclone库则文件改为cyclone_atoms.vhd、cyclone_components.vhd或cyclone_atoms.v。

5.重复2.4过程添加剩下的库http://www.cnblogs.com/Efronc

重复2.4过程添加剩下的库。

还有一种方法是把这些库放到一个库中,即一起编译。根据需要自行选择。

6. 配制modelsim.ini文件http://www.cnblogs.com/Efronc

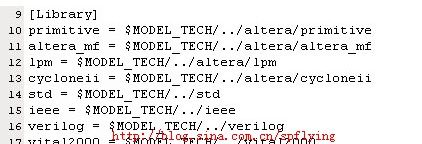

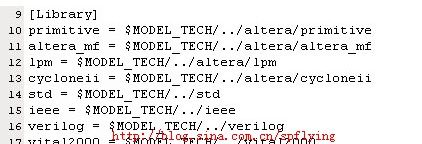

这一步是为了添加进系统库,以后不用再重复添加。

将modelsim 根目录下的配制文件modelsim.ini的属性只读改为可写,用记事本或者Ultraedit等其他文本编辑软件打开它。如下图所示添加此库(注:第一步的工程必须在modelsim的安装目录下才能使用此相对路径)。注意修改后关闭并改回只读属性。

primitive = $MODEL_TECH/../altera/primitive

altera_mf = $MODEL_TECH/../altera/altera_mf

lpm = $MODEL_TECH/../altera/lpm

cycloneii = $MODEL_TECH/../altera/cycloneii

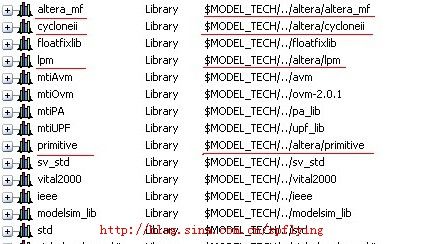

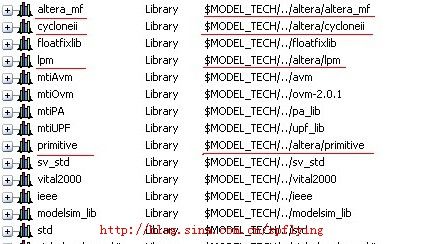

完成后如图:

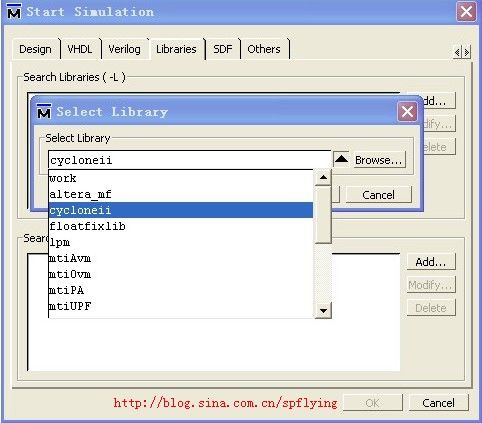

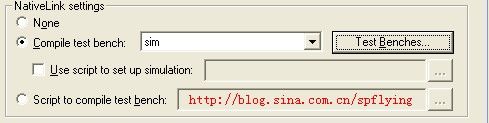

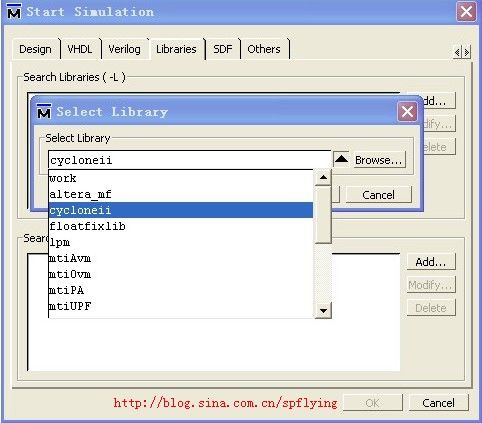

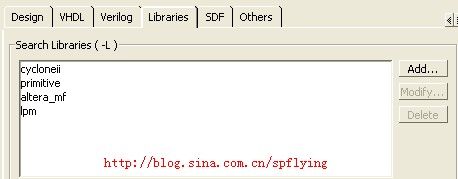

7.添加搜索库

可以根据自己需要添加某个库,可以不全加进来。如图所示:

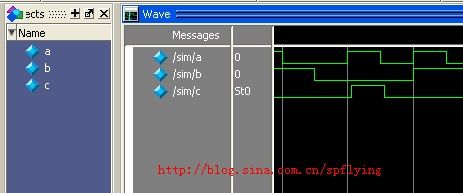

8.编译自己的vo文件和testbench文件到work库即可仿真。

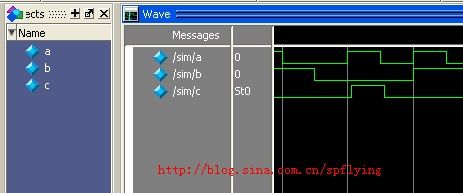

波形同上。

三.Modelsim库,Quartus II生成do文件代码分析及自行设计do文件

1.modelsim仿真库

以下是官方文档中的内容(更多内容请自行查看PDF文档)。

Design Library Overview

A design library is a directory or archive that serves as a repository for compiled design units.

The design units contained in a design library consist of VHDL entities, packages, architectures,and configurations; Verilog modules and UDPs (user-defined primitives); and SystemC modules. The design units are classified as follows:

• Primary design units — Consist of entities, package declarations, configuration

declarations, modulesUDPs, and SystemC modules. Primary design units within a given

library must have unique names.

• Secondary design units — Consist of architecture bodies, package bodies, and

optimized Verilog modules. Secondary design units are associated with a primary

design unit. Architectures by the same name can exist if they are associated with

different entities or modules.

Working Library Versus Resource Libraries

Design libraries can be used in two ways:

1. as a local working library that contains the compiled version of your design;

2. as a resource library.

The contents of your working library will change as you update your design and recompile. A resource library is typically static and serves as a parts source for your design. You can create your own resource libraries or they may be supplied by another design team or a third party(e.g., a silicon vendor).

Only one library can be the working library.

Any number of libraries can be resource libraries during a compilation. You specify which

resource libraries will be used when the design is compiled, and there are rules to specify in

which order they are searched (refer to Specifying Resource Libraries).

A common example of using both a working library and a resource library is one in which your gate-level design and testbench are compiled into the working library and the design references gate-level models in a separate resource library.

由上面的介绍可知,工作库只能有一个,而资源库则可以有许多。其中,在modelsim安装后有些库已经默认安装,例如IEEE库中包含预编译的synopsys的IEEE算法包,用于仿真加速等功能。这些库都有专用用途,初学者不宜更改。在仿真时,系统可以调用这些资源库来进行仿真,并且这些库是固定不变的。而工作库(默认的为work库,详见PDF文档)只有一个,它是用来把不同设计的编译文件等放进去,并且是不断更新变化的。

到处,我们初步了解了modelsim库的作用和概念。我们上面做的就是在modelsim中建立altera器件的仿真资源库,并且修改了ini文件使这些库是固定的(不必在不同设计中重复添加资源库,但是需要在每次打开Modelsim后添加搜索库,这两个是不同的概念)。

Modelsim仿真中会调用四种常用的仿真库:

(1)元件库,例如cycloneII元件库,在仿真中必用的特定型号的FPGA/CPLD的库。

(2)primitive,调用altera的原语(primitive)设计仿真时需要;

(3)altera_mf,调用MagaFunction的设计仿真时需要;

(4)lpm,调用lpm元件的设计仿真时需要;

第一种元件库是进行时序仿真时不可缺少的资源库。后三种库是调用了相应的Altera设计模块进行设计时才必须用到的库。值得一提的是,在modelsim-altera的AE版本中,后三种库是已经编译好的,在modelsim-altera安装目录下altera文件夹中可以找到。

2.Quartus II生成do文件代码分析

注:读者需在之前对Modelsim命令有初步的了解,可参阅help文档。

打开仿真目录.\test_sim\simulation找到其中的test_sim_run_msim_gate_verilog.do文件,用记事本或其他文本编辑软件打开。完整代码如下:

transcript on

if ![file isdirectory verilog_libs] {

file mkdir verilog_libs

}

vlib verilog_libs/cycloneii_ver

vmap cycloneii_ver ./verilog_libs/cycloneii_ver

vlog -vlog01compat -work cycloneii_ver {d:/altera/quartusii/quartus/eda/sim_lib/cycloneii_atoms.v}

if {[file exists gate_work]} {

vdel -lib gate_work -all

}

vlib gate_work

vmap work gate_work

vlog -vlog01compat -work work +incdir+. {test_sim.vo}

vlog -vlog01compat -work work +incdir+D:/Programs/Quartus/test_sim/src {D:/Programs/Quartus/test_sim/src/sim.v}

vsim -t 1ps +transport_int_delays +transport_path_delays -L cycloneii_ver -L gate_work -L work -voptargs="+acc" sim

add wave *

view structure

view signals

run -all

下面扼要的介绍一下它的控制流程。首先调用它的时候它会检测当前目录下有没有Verilog_libs这个文件夹,没有的话创建;然后在该文件夹下创建了一个物理库cyclone_ver并把逻辑库cyclone_ver映射到前面的物理库;由于前面的工程很简单,只用到了一些基本部件,所以只编译了cycloneii_atoms.v文件到cyclone_ver库;之后又创建了一个gate_work的物理库并把逻辑库work库映射到gate_work;编译了网表文件和仿真激励文件到work库;启动仿真(注意-L后面的库,这条指令的作用和第二部分最后一步的添加搜索库是一样的,感兴趣可以打开Start simulation看一下);加窗口波形信号等后运行。

3.自行设计do文件

通过上面库的介绍和Quartus II代码的分析,可以自己写一下简单的do文件自动运行了。

下面的代码是我写的do文件,注意路径的修改和代码最后的回车符。

点击tools>tcl>execute macro..打开刚刚保存的do文件运行即可。

cd D:/Programs/Quartus/test_sim/simulation/modelsim

vlib work

vmap work work

vlog -vlog01compat -work work +incdir+. {test_sim.vo}

vlog -vlog01compat -work work +incdir+D:/Programs/Quartus/test_sim/src {D:/Programs/Quartus/test_sim/src/sim.v}

vsim -t 1ps +transport_int_delays +transport_path_delays -L cycloneii -L primitive -L lpm -L altera_mf -L work -voptargs="+acc" sim

add wave *

view structure

view signals

run -all

附录:

测试程序:

module test_sim(

a,

b,

c

);

input a;

input b;

output c;

assign c = a & ( ~ b);

endmodule

仿真激励:

`timescale 1ns/1ps

`define period 10

module sim ();

reg a;

reg b;

wire c;

initial

begin

# (`period * 10) a = 1'b0;

# (`period * 10) b = 1'b0;

# (`period * 1000) $stop;

end

always #(`period * 10) a = {$random} % 2;

always #(`period * 15) b = {$random} % 2;

test_sim t_sim (

.a(a),

.b(b),

.c(c)

);

endmodule