数字IC后端设计实现流程之floorplan及powerplan规划

数字IC后端设计实现floorplan及powerplan规划

数字 IC 后端设计实现流程之 initial design

初始化 Initial 模块形状

估算完模块的面积后,block owner 会向 top 负责人报告子模块需要的大概面积,方便顶层 top 做 partition。模块的 boundary 一般都是负责 top level floorplan 的工程师基于全局考虑做 partition 后,为每个子模块分配的形状。比较有经验的 top 负责人往往在 partition 时会考虑模块实现难易程度来分配各个模块的 boundary。之所以芯片中有多边形的模块,主要有以下几方面的原因:

-

芯片 top level floorplan 中有些地方 top 不太好利用(节省面积)

-

模块的物理实现比较简单

-

负责模块的数字后端工程师能力比较强

初始化模块 floorplan 可以用如下命令实现:

Initialize_floorplan

在 ICC 中初始化模块形状时,需要注意的是方形和多边形的初始化命令是不一样的。方形的初始化命令应该用 create_floorplan 来实现。

初始化命令主要包含模块的 boundary, row, track, core to die 等信息,对应 gui 界面如下图所示。

摆放 io port

初始化模块 boundary 后,所有的 io port 均在原点。在 ICC 中是需要将这些 port,create 出对应的 terminal,摆放好它们的位置。面对成千上万的 port,很多 junior engineer 并不知道如何去摆放这些 port,这个是新手的通病。

那么多 port,显然我们不可能手工去 create terminal 和摆放对应的 port。吾爱 IC 社区的小编今天分享一个方法:

-

从 netlist 中利用脚本获得所有的 io port。这一步非常简单,因为 io port 在 net 不外乎以 input,output 或者 inout 的形式出现在 netlist 中 top module 的最上面的接口声明部分。你可以用 TCL 或者 perl 来自动获取这些 port,并写到一个文件中。

-

对获取到的 io port 文件,进行排序。如果某些模块对 io port 的 sequence 有特别要求,则需要严格按照 top 的要求重新调整 io port 顺序,否则只需要按照字母顺序即可(时钟信号建议单独处理,摆放在 port 中间位置)。

-

根据调整后的 io port sequence 文件,编写 pin constraint。这步主要指定对应 terminal 所用的层次以及 terminal 之间的间距。

-

最后执行 create_fp_pins,工具按照 pin constraint 来自动摆放 io port。

如果需要查看摆放 io port 的整套脚本,可以访问小编知识星球查看具体脚本。

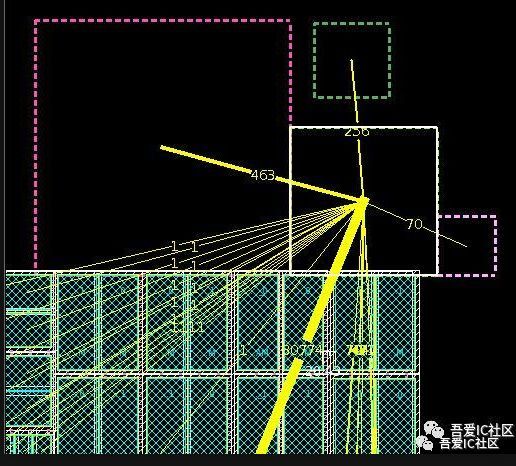

摆放 memory 和 ip

初始化模块形状后,所有的 macro,如 memory,ip 也都在原点处。如果你的模块中有两三百个 memory,你要如何快速完成 memory 的摆放呢?

具体做法:

由于 memory 特别多,建议先让工具摆放一遍。使用命令如下:

Set_fp_stragety -macros_on_edge on

这步主要指定摆放的方式为将 memory 摆放在 boundary 四周。默认情况下,工具会将 memory 摆放在中间区域。

Create_fp_placement

执行 create_fp_placement 后,此时 memory 和 standard cell 均已摆放好。但是我们只关心 memory 的位置,所以你可以将标准单元 standard cell remove 掉。需要特别注意的是工具摆放 memory 时不会考虑 poly orientation,所以需要特别留意这点。关于 poly orientation 的相关注意事项,可以参考之前推送的文章。

有了初始的 memory 位置后,我们可以利用 ICC 中 plan group 来进行 data flow 分析,从而精细化摆放 memory。

Powerplan 规划

摆放好 io port 和 memory 后,就需要进行 powerplan 规划。对于一个不做 power domain 的模块,它的 powerplan 就非常简单,就是构建一个交叉的 power mesh network 即可。本文主要讨论基于 power domain 的 powerplan 规划。在做 powerplan 规划之前,需要提前确定某个工艺的特定 Metal Stack,从而决定 block level 应该要用那些层来打 power。

- Power Switch Cell 供电 (MTCMOS)

对于需要做 power domain 的设计,需要加 MTCMOS。加 MTCMOS 需要注意以下几点:

MTCMOS 数量。关于设计中需要加多少数量的 MTCMOS,小编已经推送过,各位可以参见往期文章以及知识星球上的内容。MTCMOS 数量多少是基于 IR Drop(动态 IR Drop 和静态 IR Drop 结果),面积 Area,绕线资源等方面 tradeoff 来决定的。

【机密】从此没有难做的 floorplan(数字后端设计实现 floorplan 篇)

Create MTCMOS 后,需要为其做好 powerplan 规划,包含 global vdd 和 local vdd 的电源网络规划。由于 MTCMOS 上的 global power pin 是底层出 pin 的,而 global power strap 是高层供下来的,所以在 MTCMOS 上会有很多大孔。当设计中 MTCMOS 过多时,可能会导致 routing resource 不足,从而出现 short,diff net spacing 等 physical drc。

在规划 local vdd 电源网络时,需要考虑电源网络供电路径的电阻最小化。

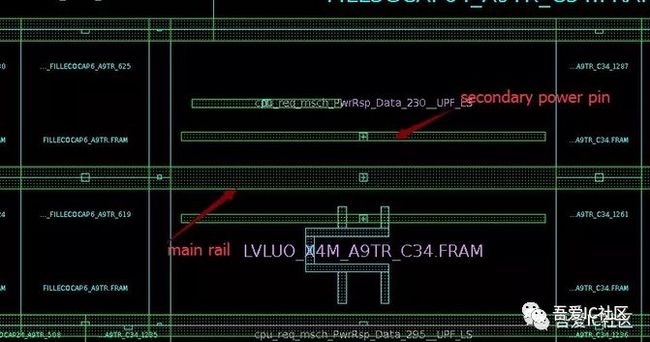

- Level shifter cell 供电

在数字后端实现中,我们会经常用到 Level shiftr。 Level shifter cell 的 power 连接是非常有讲究的。实践表明,很经常碰到 level shifter 区域存在特别大的 IR drop 问题。出现这种问题一般都是没人认真去研究 level shifter power 的连接方法。Level shifter 是两条 row 高度的 cell,其中含有 VDD,VSS 和 VDDL(VDDH)。VDDL 和 VDDH 是 secondary power pin。在画 power 时,需要将其画成一个额外的 power rail,确保每个 Level shift cell secondary power pin 的正常供电。

更多关于数字 IC 后端设计实现中 secondary power pin 的连接方法见往期推文。

推荐阅读:

低功耗设计实现中 secondary power pin 的连接方法汇总

- Memory 供电

Memory 上 power ground pin 一般是 Metal4 出 pin 的,所以可以用 Metal5 进行衔接,然后再将 Metal5 连接到更高层的金属上。

需要注意的是实际芯片出来,memory 上出问题的概率还是蛮大的。所以在数字后端设计实现时,需要确保 memory 供电足够充足。对于一个做 power domain 的设计,需要在 memory 周围加够 MTCMOS,打够 power strap。

- IP 供电

这里指的 IP 是指 SOC 设计中所用到的物理 phy。在给这类 IP 打 power 时,需要查阅 vendor 相关文档,整理出一个 check list 来。一般 vendor 会给出 IP 本身与四周其他 IP 的最小间距要求,与 core logic 区域之间的最小间距以及某电源网络路径最大电阻的要求等等。

即使你严格按照了 vendor 要求来做 floorplan 和 powerplan,你仍然需要将你的做法同 vendor 进行再次确认。做这一步目的是防止甩锅和背锅,老司机一定懂得。

如何 qualify floorplan 和 powerplan?

- verify_pg_nets 来检查

Verfy_pg_nets 的结果需要认真看,主要看设计中是否存在 floating pin,特别是 MTCMOS 是否存在 floating 的 global vdd。对于结果报告,需要我们能够分辨出哪些是真错,哪些是假错(或者说不用关心的错误),比如 floating shape 的错误就可以完全不用管。

- 跑一个初始版本的 DRC

这步主要用来检查 memory,ip 和标准单元 standard cell 的 poly orientation 方向是否一致以及 powerplan 是否存在 physical DRC 等。

- 人工 review floorplan 和 powerplan

这步是小编每个项目都会去做的,也强烈推荐各位也去做这个事情。因为有的时候你现有的 floorplan 和 powerplan 可能工具分析结果并没有大问题,但是从我们自身积累的工作经验出发,我们可能能够找出设计出的不足,比如某些 memory 的 channel 留得太大,channel 间 MTCMOS 不够,局部区域供电网络不够 robust 等。一个不是很完美的 floorplan 和 powerplan,如果你叫上两三个资深点的工程师去 review,肯定会被抓出不少毛病来的。

原文链接:https://mp.weixin.qq.com/s/SaPiSLp87WEcx8gWgoOiqQ