DDR3逻辑相关

1.DDR3为了保证CPU正常工作,必须一次传输完CPU 在一个传输周期内所需要的数据。而CPU在一个传输周期能接受的数据容量就是CPU数据总线的位宽,单位是bit(位)。一般是64bit,所以我们的板子加了4片DDR3=4X16bit=64bit.

2.根据Part Number 中的“-125”我们就可以找到图中的tCK = 1.25ns,就可以算出芯片支持的最大IO时钟频率:1/1.25ns = 800Mhz;此处的IO时钟频率也就是DDR3的频率

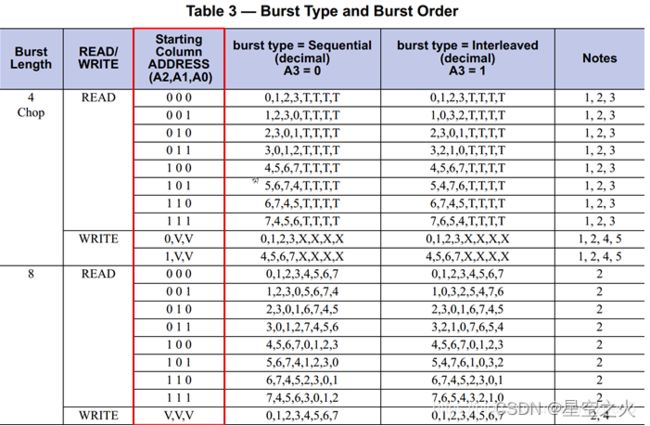

3.当一个FPGA上挂多个DDR,如4片ddr3,位宽则会相应增大;16*4 = 64bit,再乘以DDR3的突发长度BL=8;那么程序设计里DDR3的读写位宽就变成了16*4*8=512bit; (这里留个印象,再后文IP例化及程序设计部分还会讲到,到时候对应起来看更容易理解)——Read Burst Type and Length: 突发类型选择,突发类型有顺序突发和交叉突发两种,本次选择顺序突发(Sequential),其突发长度固定为 8。

4.由于是DDR方式传输数据(上升和下降沿都传输),所以芯片的一根数据线上的传输速率 = 2*800Mhz = 1600MT/s(1Kb=1000bit)。其实就是1600Mbit/s;带宽就是16根数据线同时传输的数据速率 = 1600Mbit/s x 16 = 25600Mbit/s = 3200Mbyte/s = 3.125GByte/s

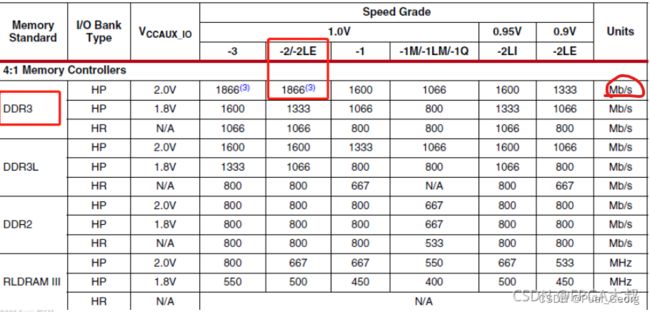

k7系列的FPGA所支持的DDR3传输速率高达1866MT/s,这里需要跟硬件工程师具体了解了解,实际使用最高还是1600MT/s,对应频率= 1600M/2= 800Mhz;

5.Clock Period:(上图已讲解如何查看器件所支持的最大频率)

6.术语部分

核心频率:核心频率就是DDR物理层(PHY)IO时钟频率,对应到MIG就是第一个配置的“CLOCK PERIOD”,上文我们选择的是800Mhz

工作频率:核心频率* 2 (上下沿)= 1600M核心频率* 2 = 1600M

传输速率:核心频率* 2 = 1600MT/s

带宽:传输速率*位宽 = 1600M * 16 = 25600Mbit/s = 3200Mbyte/s = 3.125GByte/s

7.选择DDR3的类型,Components指的是DDR3的型号是元件类,笔记本那种的插条类是SODIMMs。

8.是否使用XADC,会输出器件的温度,如果其他模块要用XADC,那么这里就不使能。

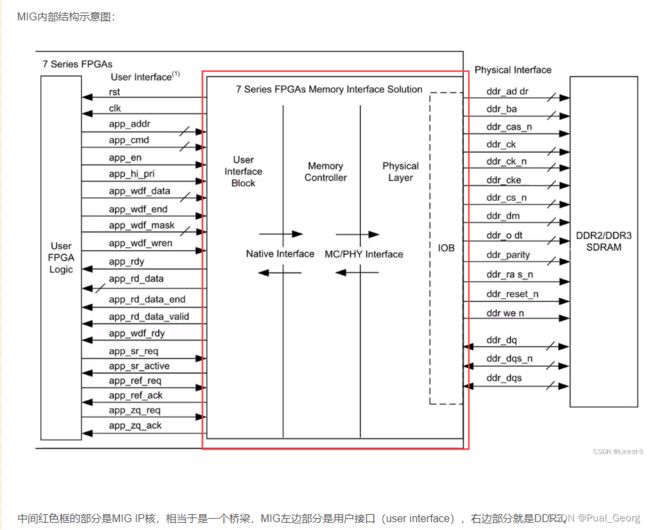

利用MIG核(上图红色部分)可以核DDR3芯片进行通信,我们只管USER FPGA logic部分就可以了。

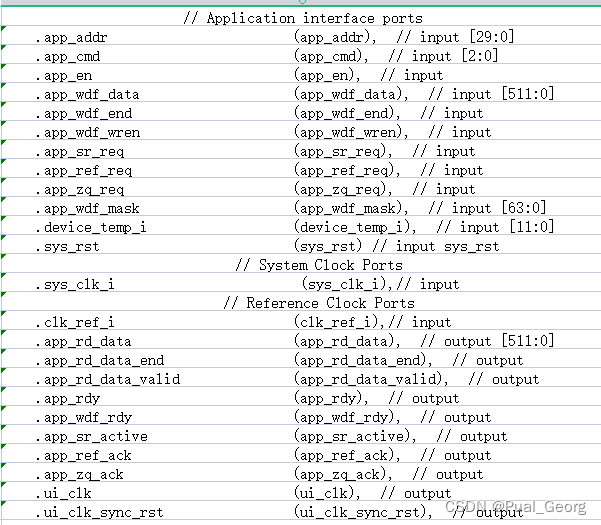

mig_7series_0 u_mig_7series_0 (

// Memory interface ports

.ddr3_addr (ddr3_addr), // output [15:0] 行列地址,其中行地址线和列地址线是分时复用的,即地址要分两次送出,先送出行地址,再送出列地址。

.ddr3_ba (ddr3_ba), // output [2:0] bank地址

.ddr3_cas_n (ddr3_cas_n), // output 列地址选通

.ddr3_ck_n (ddr3_ck_n), // output [0:0] 差分时钟p端

.ddr3_ck_p (ddr3_ck_p), // output [0:0] 差分时钟n端

.ddr3_cke (ddr3_cke), // output [0:0] 时钟有效信号,高电平有效

.ddr3_ras_n (ddr3_ras_n), // output 行地址选通信号,低电平有效

.ddr3_reset_n (ddr3_reset_n), // output 复位信号,低电平有效

.ddr3_we_n (ddr3_we_n), // output 0-写允许 1-读允许

.ddr3_dq (ddr3_dq), // inout [63:0] 数据

.ddr3_dqs_n (ddr3_dqs_n), // inout [7:0] 数据选取脉冲

.ddr3_dqs_p (ddr3_dqs_p), // inout [7:0] 数据选取脉冲

.init_calib_complete (init_calib_complete), // output 初始化完成信号 ,高电平有效

.ddr3_cs_n (ddr3_cs_n), // output [0:0] 片选信号,低表示命令有效,否则命令屏蔽

.ddr3_dm (ddr3_dm), // output [7:0] 数据掩码 一位控制一个字节

.ddr3_odt (ddr3_odt), // output [0:0] 片上终端使能,高电平有效

// Application interface ports

.app_addr (app_addr), // input [29:0] 访问的DDR3地址

.app_cmd (app_cmd), // input [2:0] 000 写命令 001 读命令

.app_en (app_en), // input 命令路径:的使能信号,该信号有效时,app_cmd、app_addr信号才有效,其余的时刻信号无效

.app_wdf_data (app_wdf_data), // input [511:0] 写数据路径数据信号

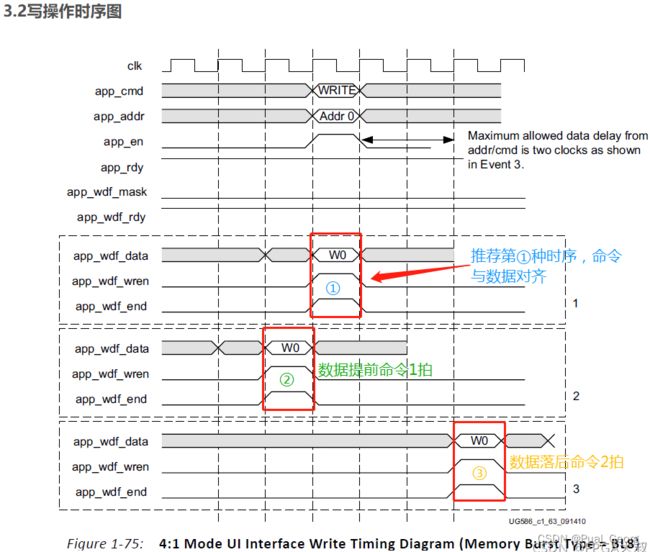

.app_wdf_end (app_wdf_end), // input 4:1模式下与app_wdf_wren相同,2:1模式下每两个app_wdf_wren,使能一次 app_wdf_en。这个可以理解可参考UG586数据手册P169 Figure 1-78/ Figure 1-79

.app_wdf_wren (app_wdf_wren), // input 写数据的有效信号

.app_rd_data (app_rd_data), // output [511:0] 读数据信号

.app_rd_data_end (app_rd_data_end), // output DDR3给用户读命令结束信号

.app_rd_data_valid (app_rd_data_valid), // output 读数据有效信号

.app_rdy (app_rdy), // output 命令路径准备好接受用户的命令信号,与app_en有效时命令有效

.app_wdf_rdy (app_wdf_rdy), // output MIG信号给用户的信号,在该信号与app_wdf_wren信号同时有效时,数据被写入DDR芯片

.app_sr_req (1'b0), // input 一般为0

.app_ref_req (1'b0), // input 一般为0

.app_zq_req (1'b0), // input 一般为0

.app_sr_active (), // output 上面请求的响应信号

.app_ref_ack (), // output 上面请求的响应信号

.app_zq_ack (), // output 上面请求的响应信号

.ui_clk (clk), // output MIG给用户使用的时钟,用户对MIG IP核的操作必须使用该时钟

.ui_clk_sync_rst (rst), // output MIG给用户使用的复位信号,用户对MIG IP核的操作必须使用该复位信号

.app_wdf_mask (64'd0), // input [63:0] 写数据的掩码 ,一般为0

// System Clock Ports

.sys_clk_p (sys_clk_p), // input MIG的系统时钟,在MIG的选项中选择

.sys_clk_n (sys_clk_n), // input

.sys_rst (sys_rst) // input sys_rst MIG IP核的复位信号,与系统时钟相关联

);

我们可以看一下这个DDR3的内部结构图,从这个图中我们可以看出10bit的Column Address的寻址能力只有128,只有7bits用于列地址译码!列地址0,1,2并没有用,而这列地址的低三位被用于确定Burst Length 与Burst Order了.见下图:(所以列地址的低三位并没有用于寻址,所以如果我们想要访问下一存储单元的话,地址需要加8而不是加1)