Arm发布全新服务器芯片及路线图,进一步叫板X86

![]()

来源:内容编译自「anandtech」,谢谢。

Arm对服务器市场拥有巨大的野心是一件众所周知的事实,但这是需要历经数年才得以实现的愿望。过去多年里,虽然Arm阵营经过许多怀疑和错误的尝试,但到2020年的今天,没有人可以否认,由该公司CPU IP驱动的服务器芯片的确具有竞争力,而且在多个指标上实际上处于领先地位。

亚马逊的 Graviton2—— 64核的Neoverse N1服务器芯片是这个另一库第一款被广泛应用的产品,它将推动Arm服务器生态系统向前发展,并积极进攻目前由x86厂商(如英特尔和AMD)主导的基础架构CPU市场份额。

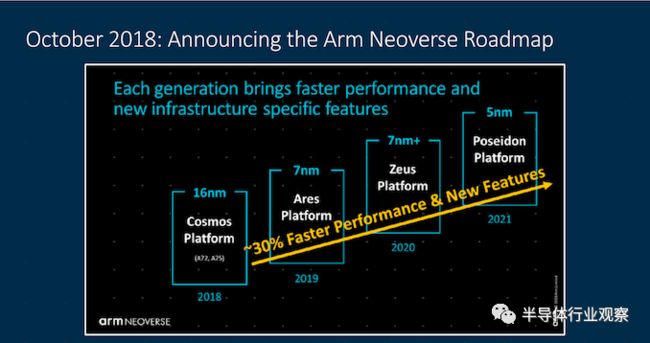

这段旅程虽然漫长,但其根源可以追溯到公司早在2018年制定的公开路线图上。快进到2020年,我们不仅看到带有第一代Neoverse N1基础架构CPU IP的产品以商业和公开可用的形式进入市场,而且我们已经看到该公司将其30%的目标实现的目标收益提高了2倍。

Neoverse V1:全新的最高性能层基础架构CPU

今天,我们已准备好迈向下一代Neoverse平台。Arm不仅展示了先前称为Zeus的CPU微体系结构,而且还展示了Neoverse N系列以外的全新产品类别:推出新的Neoverse V系列和Neoverse V1(宙斯),以及以Neoverse N2(Perseus)形式出现的新路线图。

新的Neoverse V1将新的V系列引入Arm的基础设施IP产品组合,从本质上讲,这代表着该公司为追求更高的绝对性能而不考虑成本的努力。

今年春季初,我们介绍了该公司新的移动Cortex-X1 CPU IP,它代表着Arm的重要商业模式变更:过去,Arm只提供一个单一的,适合所有人的CPU微体系结构,被许可人必须采用更广泛的设计和制造方案。但现在从性能方面,我们已经看到了微体系结构的差异,一种IP产品现在专注于纯粹的最高性能(Cortex-X1),无论面积或功耗成本如何;而另一种设计(Cortex-A78)专注于Arm的产品。更传统的最大化PPA(功率,性能,面积)设计理念。

Neoverse V1形式的Zeus微体系结构实质上是Arm在Hera Cortex-X1 CPU IP的移动IP产品中实现的基础设施对应物:专注于最大性能,而对功耗和面积的关注较少。

这意味着V1具有显着更大的缓存,内核结构,使用了更多的面积和功能来达到前所未有的性能水平。

与我们今天在芯片中看到的Neoverse N1相比,Arm的新架构实现了突破性的+50 IPC提升。这里的性能提升潜力是巨大的,因为这仅是同一进程的ISO频率升级,并且由于V1通过制程节点的改进而增加了频率,因此基于V1的实际产品也很有可能还会获得额外的性能提升。

如果以保守时钟的Graviton2及其2.5GHz N1内核为基准,则理论上的3GHz V1芯片将使每核单线程性能提高80%。就单核性能而言,这样的性能提升不仅会大大超过服务器领域当前的任何x86竞争者,而且足以与当今AMD和Intel当今最好的高性能台式机芯片相媲美(尽管我们必须记住它将与下一代Zen3 Milan和Willow Cove Sapphire Rapids产品竞争。

Neoverse N2是英仙座:继续PPA关注

除了Neoverse V1平台,我们还看到了以前没有的路线图插入。英仙座(Perseus)的设计将成为Neoverse N2,并将成为N1的有效产品定位继承者。与N1相比,这种新的CPU IP代表了40%的IPC提升,但是仍然保持着相同的设计理念,即在最低功耗和最小面积内实现性能最大化。

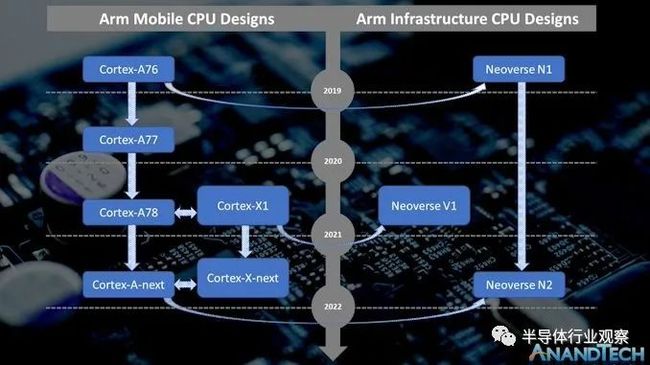

当我们在这里谈论的微体系结构世代时,可能会有些混乱,因此我制作了一张图表来说明我们可以称呼Arm的移动设备和服务器CPU IP之间的世代同级产品:

尽管这只是Arm产品的总体概况,但需要注意的是,在设计期间的同一时间串联开发的Cortex和Neoverse产品之间存在相似之处。Neoverse N1是与Cortex-A76一起开发的,因此这两个微体系结构可以视为兄弟设计,因为它们具有很多相似之处。

Neoverse V1可以看作是Cortex-X1的同级设计,可能共享许多为这两个旗舰CPU开发的超大型内核结构。

Neoverse N2较为特殊,因为它代表了下一代Cortex-A内核的兄弟姐妹设计,这是A78的后续产品。Arm表示,他们将在今年年底前获得该“ Perseus”设计的许可,并且客户已经在使用beta RTL ,我们很可能在明年的TechDay活动中听到更多有关这一代产品的信息。N2将比V1落后一年,随后将需要更多时间才能在产品中看到这一点。

需要注意的是,以上所有设计均基于Austin,并且可以视为与Cortex-A76相同的微体系结构家族。如果我没记错的话,下一代“波塞冬”设计将采用Arm的Sophia-Antipolis设计团队开始的全新的微体系结构,尽管Arm确实指出,如今不同团队之间存在更多的协作和模糊化。在这里,Arm已经注意到,这一代设计的IPC提升了30%,且有可能在2023年投放市场。

带有SVE的未公开架构:Armv9?

Neoverse V1和N2的一个非常显着的特征是它们现在支持SVE(可伸缩矢量扩展),其中V1具有两个原生256位流水线,而N2是2x128位设计。SVE与其他SIMD ISA相比的优势在于,其中写入的代码可以随着微体系结构的执行宽度的变化而扩展,而这对于当今的Neon或AVX SIMD指令来说是无法实现的。

迄今为止,富士通的A64FX芯片和定制核心微体系结构是唯一宣布的且可与SVE一起使用的CPU,这意味着V1和N2将是Arm实际实施SVE的第一个自己的设计。

今天有关V1和N2 CPU这部分内容的公告引起了更多的疑问,但没有答案,因为该公司不愿透露此支持是否涉及第一代SVE指令集,或者它们是否已经支持SVE2。

实际上,无论是Armv8设计还是后续迭代之一,该公司甚至都不会确认设计的基础架构。对于公司而言,这是非常不寻常的,因为它在IP的这些基本方面一向都是透明的。

我认为这里发生的是V1和 N2可能都是 Armv9设计,并且该公司将最迟在今天宣布到明年年中的某个时候公开披露新的ISA迭代,当然,这只是我自己的猜测,因为Arm拒绝对此话题发表评论。

更新:实际上,似乎Arm 早在6月就已经将上游的初始编译器条目公开提交给GCC for Zeus,从而确认至少Neoverse V1是Armv8.4 + SVE(1)设计。我仍然认为N2可能是v9 + SVE2设计。

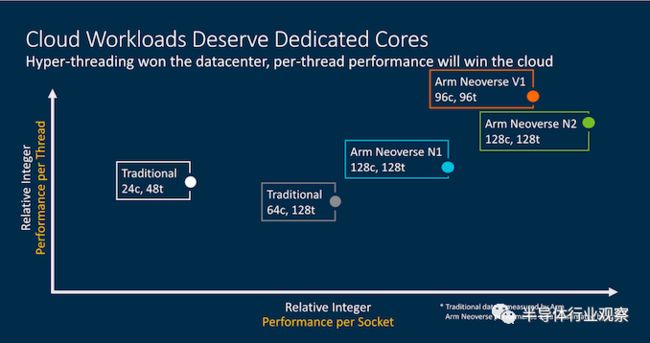

归根结底,我们得出的是两个极其引人注目的新微体系结构,它们极大地推动了Arm在基础设施市场中的地位。Neoverse N2是一个显而易见的设计,着重于Arm的PPA指标,该公司认为客户设计的产品主要侧重于需要大量CPU内核的“横向扩展”工作负载。在这里,我们可以看到多达128个内核的设计。

Neoverse V1将看到较少的内核数设计,因为CPU更大,功耗更高。Arm认为被许可人最有可能采用64到96范围的设计。这些顶级产品将与英特尔和AMD所能提供的最好的产品相抗衡,如果性能预测得以实现(如通常对Arm所做的那样),那么我们将与我们进行激烈的竞争我见过。

SiPearl的“ Rhea”芯片是第一个被确认采用新Neoverse V1内核的公共设计,该芯片希望在7nm TSMC工艺节点中具有72个内核。Ampere的“ Siryn”设计还将成为应用V1微体系结构的候选对象,该微体系结构的目标是2022年在台积电的5nm节点上发布。

![]()

1.用于MCU,基于FreeRTOS的micro(轻量级)ROS!

2.RT-Thread团队回应社区关切:鸿蒙OS带来的影响-合作远远大于竞争

3.从嵌入式编程中感悟「栈」为何方神圣?

4.bug粉碎机之volatile的那些坑

5.118亿晶体管!苹果A14首秀,这颗全球首发的5nm芯片有多香?

6.嵌入式C语言源代码优化方案(非编译器优化)

![]()

免责声明:本文系网络转载,版权归原作者所有。如涉及作品版权问题,请与我们联系,我们将根据您提供的版权证明材料确认版权并支付稿酬或者删除内容。