FPGA:Vivado流水灯设计详细流程(1)

基于Vivado的FPGA设计开发的流程主要包括以下步骤:

1)创建工程;

2)创建源设计文件,包括Verilog文本、IP核、模块文件、网表输入等方式;

3)行为仿真(Behavioral Simulation),Vivado自带仿真器,也可以选择第三方仿真软件ModelSim等工具进行仿真;

4)综合(Synthesis):根据设定的编译策略,对工程进行综合,生成网表文件;

5)引脚约束:通过I/O Planing或者直接编辑.XDC文件添加引脚约束信息;

6)实现(Implimentation):指针对某一具体的目标器件经布局布线(Plance&Route),或者适配器(Fitting),产生延时信息文件、报告文件(.rpt),以供时序分析、时序仿真使用;

7)生成Bitstream文件,产生.bit和.bin等编程文件;

8)将生成的Bitstream文件下载至FPGA芯片。

以Ver流水灯设计为例,介绍在Vivado环境下运行Verilog程序的流程,包括源程序的编写、编译、仿真及下载。本例基于Vivado18.3版本。

1.流水灯设计输入

(1)创建新工程

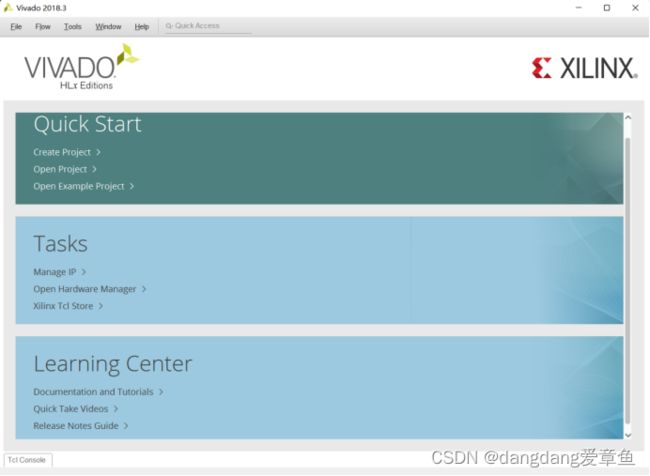

双击Vivado18.3,出现如图所示的界面,单击Quick Start栏中的Create Project,启动工程向导,创建一个新工程。

工程路径F:/FPGA/VIVADO/FPGA-Project/exam;

工程名称:flow_led

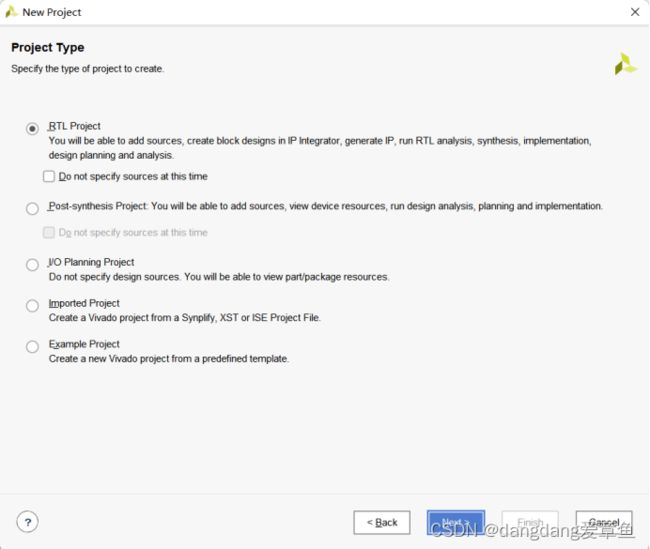

选择项目类型

选择RTL项目,RTL仿真就是程序仿真,RTL用硬件描述语言描述出功能,然后经过逻辑综合,得到门级单元。

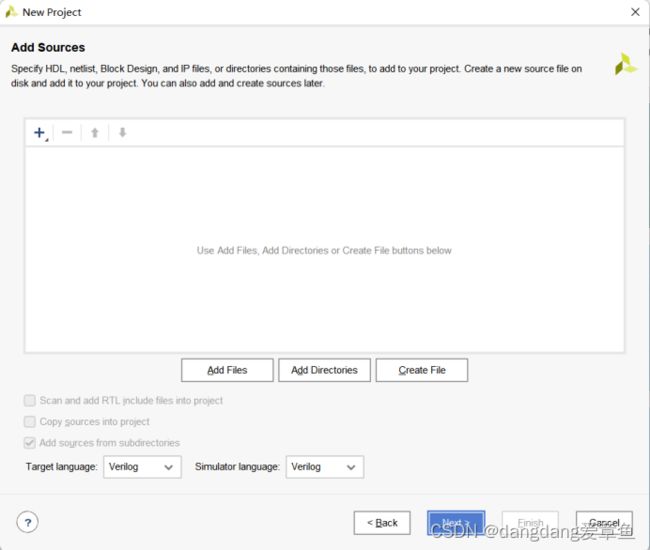

添加源文件与选择设计语言,target language与simulator language都选择Verilog语言,单击next。

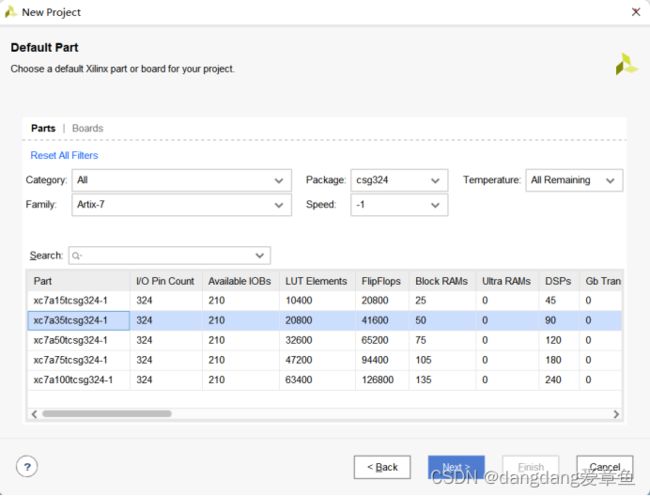

在器件选择页面中根据自己使用的FPGA开发板进行选择,我这里选择Xilinx的Artix-7开发板,封装形式package选择csg324,单击next;

工程创建成功页面如下所示,核对自己选择的信息,无误后点击finish。

(2)输入源文件设计

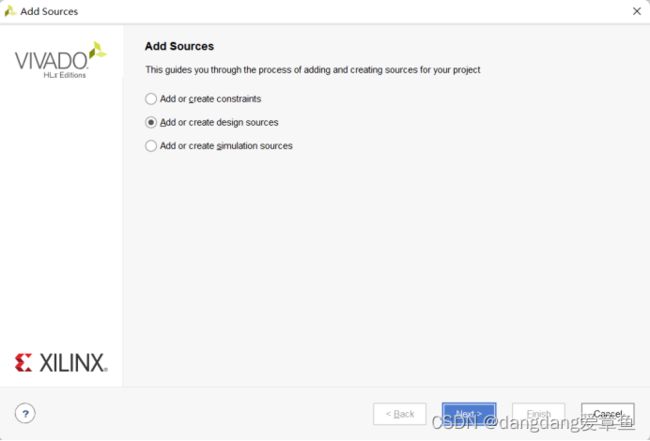

在Flow Navigator下的Project Manager中点击Add Sources,打开设计文件导入窗口;

在Add Sources窗口中选择Add or create design sources选项,表示创建源文件;

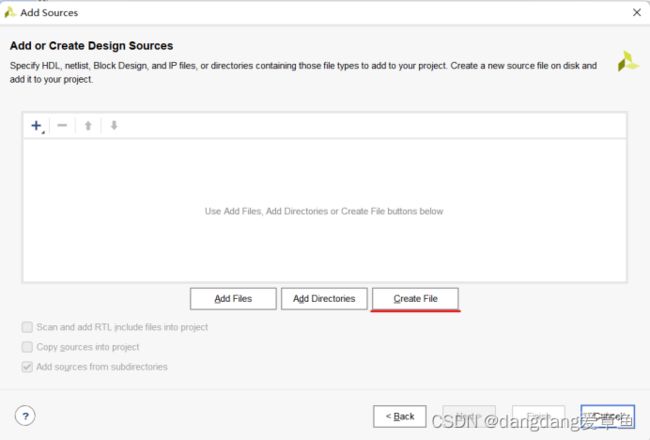

点击Create File新建文件;

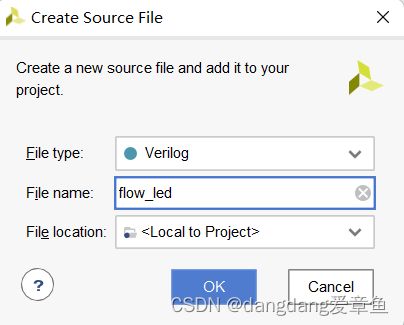

填写源文件名称为flow_led;

在Sources栏中点击新建的flow_led.v文件,开始进行流水灯源文件的编写;

流水灯设计源代码flow_led.v

module flow_led(clk,clr,led);

input clk;

input clr;

output reg [7:0] led;

reg [28:0] counter;

//时序逻辑

always @(posedge clk)

begin

if(!clr) begin counter <= 0; led <= 8'h01; end

else

if(counter < 50000000)//2Hz

counter <= counter + 1;

else

begin

counter <= 0;

led <= {led[6:0],led[7]};

end

end

endmodule

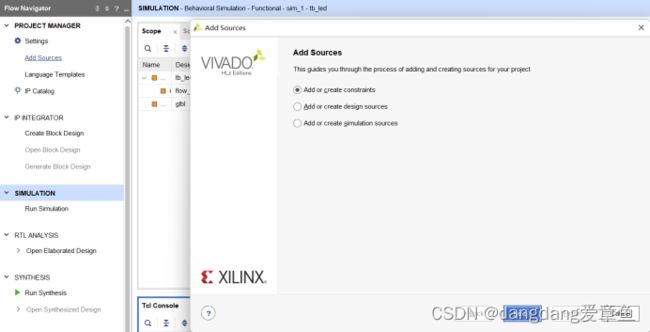

(3)行为仿真

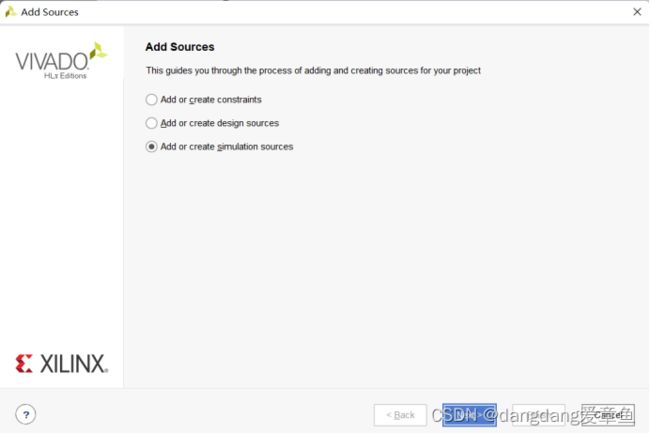

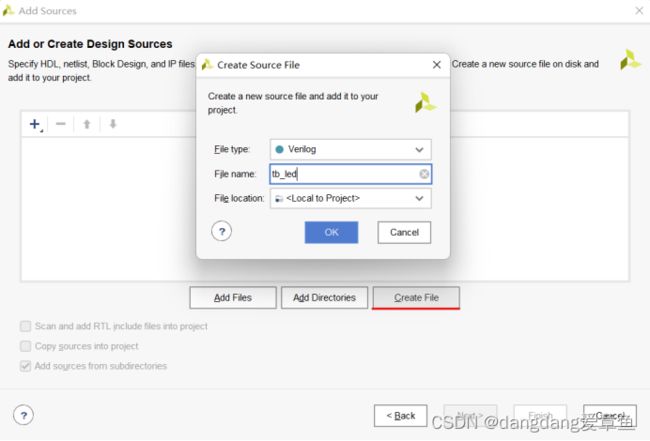

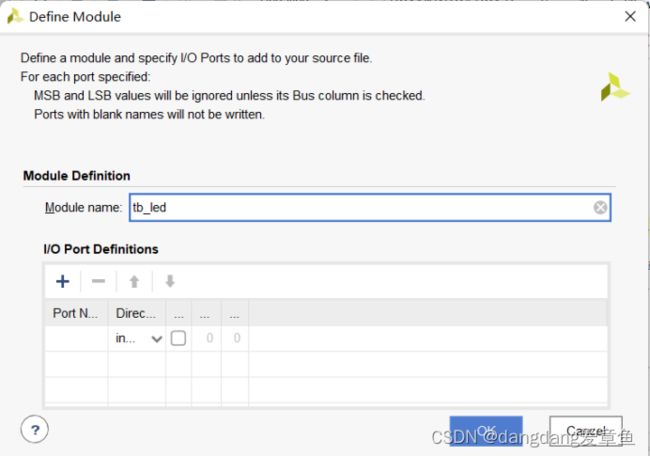

在Flow Navigator下的Project Manager中点击Add Sources, 在Add Sources窗口中选择Add or create simulation sources选项,表示创建仿真激励文件;

点击Create File新建文件; 填写激励文件名称为tb_led;

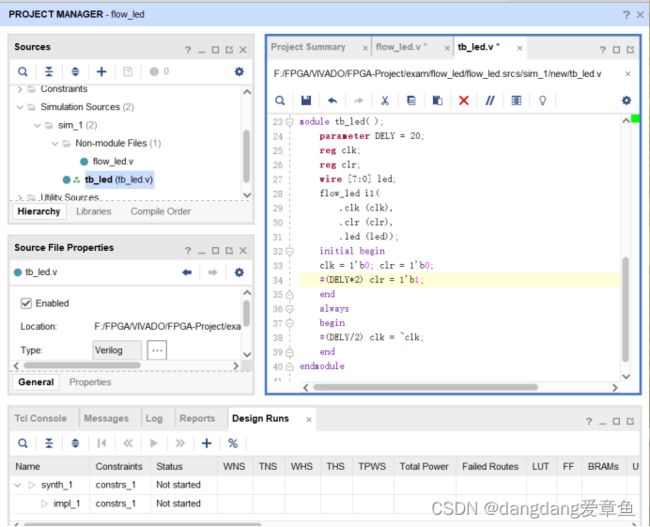

在Sources栏中点击新建的tb_led.v文件,开始进行流水灯源文件的编写;

流水灯测试代码激励文件tb_led

`timescale 1ns / 1ns //时间尺度/时间精度

module tb_led( );

parameter DELY = 20;

reg clk;

reg clr;

wire [7:0] led;

flow_led i1(

.clk (clk),

.clr (clr),

.led (led));

initial begin

clk = 1'b0; clr = 1'b0;

#(DELY*2) clr = 1'b1;

end

always

begin

#(DELY/2) clk = ~clk;

end

endmodule

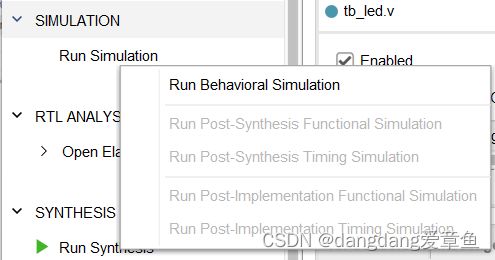

开始进行行为级仿真,在Flow Navigator下的Simulation中点击Run Simulation选择Run Behavioral Simulation;

100ms表示仿真的时间长度。得出如下的仿真图,观察此波形是否和预想的一致,验证原设计问价的正确性。

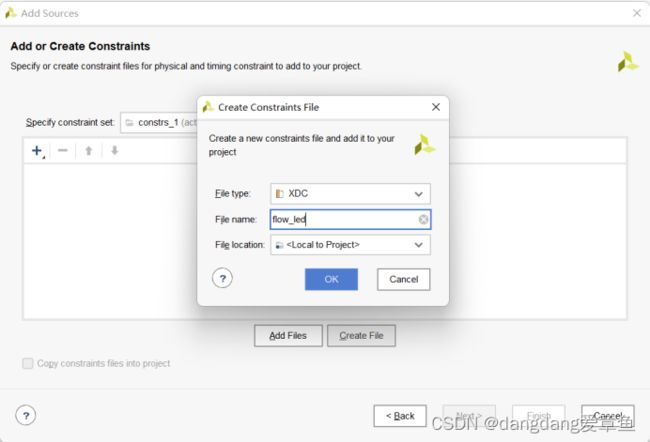

(4)创建引脚约束文件

在Flow Navigator下的Project Manager中点击Add Sources, 在Add Sources窗口中选择Add or create constraints选项,表示创建引脚约束文件;

输入文件名;

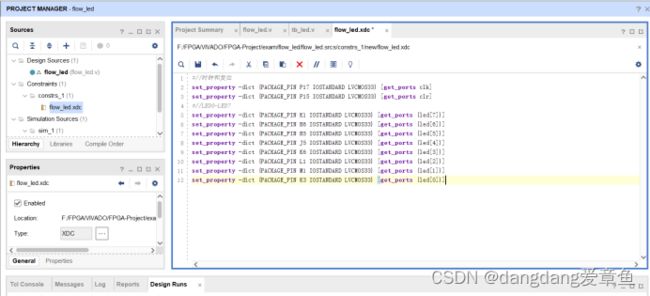

创建完成后,双击sources栏中的Constraints下的flow_led.xdc文件,输入引脚约束文件。

XDC 编写的语法:

约束引脚号:set_property PACKAGE_PIN " 引脚编号 " [ get_ports “端口名称”]

约束电压: set_property IOSTANDARD " 电平标准 " [ get_ports “端口名称” ]

重点:

通过原理图,查看LED与FPGA中实际引脚相连位置,然后看驱动该FPGA的Bank是多大的电压,如果是1.5V电压驱动,那就是LVCMOS15 ,如果是1.8V驱动,那就是LVCMOS18

解读:

set_property:设置属性

IOSTANDARD :IO标准

LVCMOS15 :1.5V

get_ports :获取端口

led_tri_o[3]:第3个led端口

PACKAGE_PIN :引脚

F5 :引脚约束到F5

通俗理解:

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[3]}]修改led_tri_o[3]的IO标准为1.5V

set_property PACKAGE_PIN G6 [get_ports {led_tri_o[3]}] 将led_tri_o[3]约束到G6引脚

流水灯引脚约束文件

#//时钟和复位

set_property -dict {PACKAGE_PIN P17 IOSTANDARD LVCMOS33} [get_ports clk]

set_property -dict {PACKAGE_PIN P15 IOSTANDARD LVCMOS33} [get_ports clr]

#//LED0-LED7

set_property -dict {PACKAGE_PIN K1 IOSTANDARD LVCMOS33} [get_ports {led[7]}]

set_property -dict {PACKAGE_PIN H6 IOSTANDARD LVCMOS33} [get_ports {led[6]}]

set_property -dict {PACKAGE_PIN H5 IOSTANDARD LVCMOS33} [get_ports {led[5]}]

set_property -dict {PACKAGE_PIN J5 IOSTANDARD LVCMOS33} [get_ports {led[4]}]

set_property -dict {PACKAGE_PIN K6 IOSTANDARD LVCMOS33} [get_ports {led[3]}]

set_property -dict {PACKAGE_PIN L1 IOSTANDARD LVCMOS33} [get_ports {led[2]}]

set_property -dict {PACKAGE_PIN M1 IOSTANDARD LVCMOS33} [get_ports {led[1]}]

set_property -dict {PACKAGE_PIN K3 IOSTANDARD LVCMOS33} [get_ports {led[0]}]

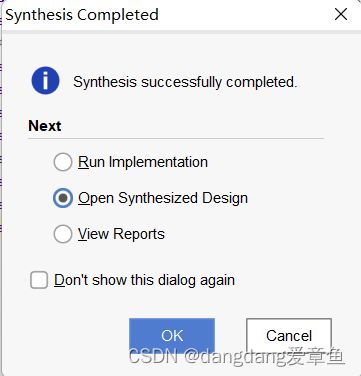

(6)综合编译生成电路图

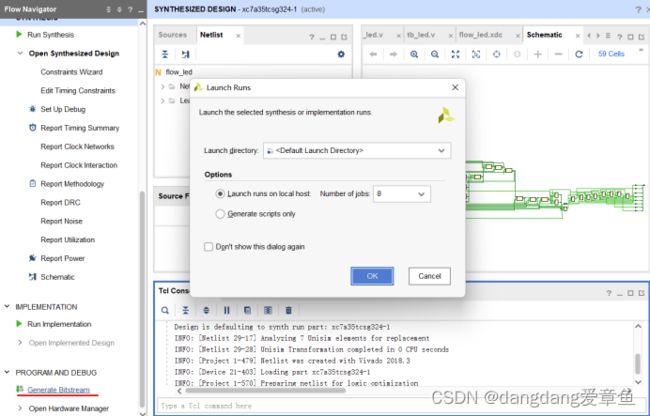

点击左侧导航栏中的Synthesis下的Run Synthesis进行综合编译,为缩短编译时间,此处选择8;

直接选择的打开综合设计文件;

编译成功后点击导航栏中的Open Synthesis Design下的Schematic,可以查看综合后的电路图。

(7)生成比特流文件并下载

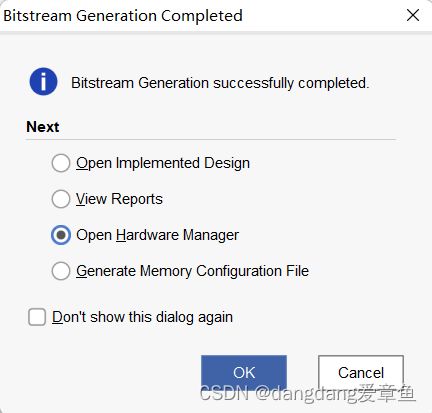

点击导航栏中的Program and Debug下的Generate Bitstream生成比特流文件;

选择打开硬件管理器;

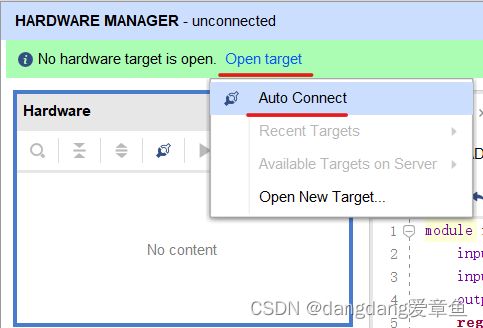

电脑外接开发板后点击Hradware manager栏中下方的Open target中的Auto Connect,进行开发板的连接。

搜索电脑外接的FPGA开发板,由于我还没有开发板,目前就演示到这里,后面再更新。