SAR ADC 系列9:采样上机实践

目录

作业问题:

上机实践1:传输门的导通阻抗

上机实践2:Booststrap功能验证

上机实践3:Booststrap线性度仿真

Bootstrap设计

仿真确定开关尺寸

仿真BootstrapDFT

确定抬升电容C的大小

确定CB的上拉下拉MOS管尺寸

确定CLK反相C点NMOS尺寸——不重要的管子

Diode连接(衬底连接)

下级板采样

Bootstrap开关中MOS管尺寸选取

作业问题:

- 电容会产生噪声吗?——(不会)

- 一阶RC滤波器的噪声表达式——(KT/C)

- 采样时钟的Jitter对SNR的影响仅仅取决于输入信号频率,与采样频率无关?——(是,fin与jitter)

- 电压电压较低的情况下(VDD<1V),传输门开关失效的原因是什么?——(阈值电压高,MOS管将近截止了)

- 上极板采样和下极板采样哪个精度更高?——(下级板精度高)

- 下极板采样电路中,哪个时钟沿最关键?——(下降沿提前到来的TOP极板时钟)

- 下极板采样电路中,哪个点是敏感点(Sensitive Point)?——(TOP极板)

上机实践1:传输门的导通阻抗

设计一个传输门开关:

■ 采用IO器件(VDD高),导通阻抗要求:~1KOhm@TT/2.5V/25

上机实践2:Booststrap功能验证

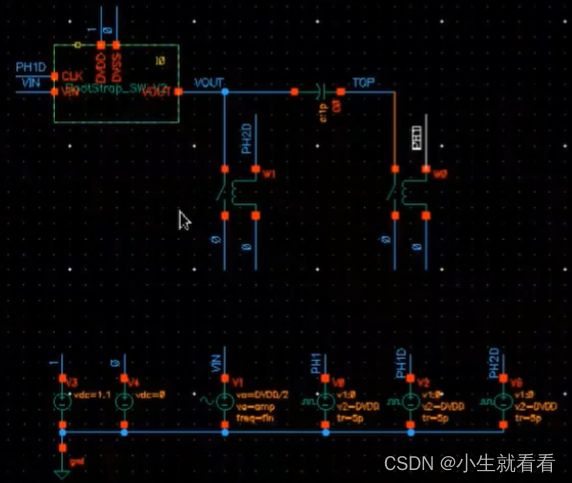

设计一个Bootstrap开关电路:

■ 1.1V Core器件,CLK=50MHz,Vin=0~1.1V的sin波,导通阻抗<1K

上机实践3:Booststrap线性度仿真

利用设计好的Bootstrap开关设计一个采样电路:

■ 上极板采样网络,采样电容=1pF,CLK=50MHz,Vin≤20MHz,最大幅度0~VDD

■ 下极板采样网络,其余参数相同,除了Bootstrap外,其余开关可用理想开关。

Bootstrap设计

仿真确定开关尺寸

Vin接在开关一端,自举开关Gate端在Vin基础上抬高VDD*K(系数K代表电压抬高系数)。

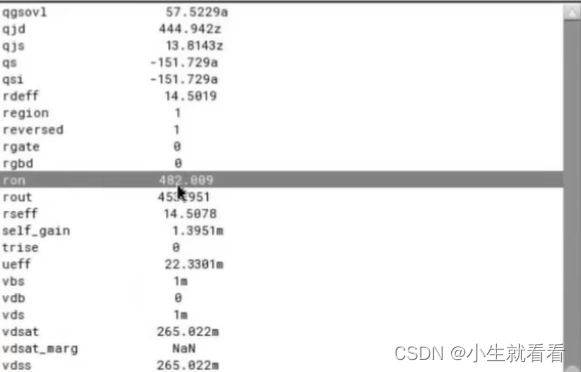

仿真导通阻抗的方法。如图,开关两端用一个vdc连接,标定开关等效电阻Req的电压为vdc(1mV),DC仿真,看通过开关的电流(也是通过vdc的电流 Req=vdc/idc。或者直接看MOS管OP参数,有个ron是电阻。

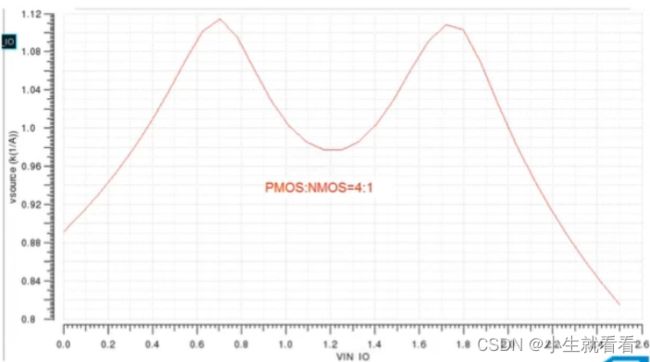

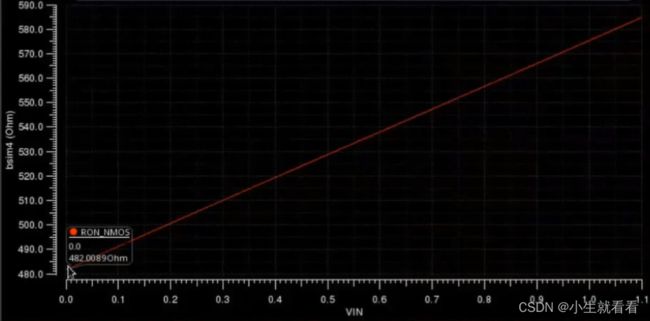

DC仿真Vin扫描0V:0.1V:1.1V(线性11步),plot开关等效电阻ron。当Vin=0时是没有衬偏效应的,随着Vin的增加,衬偏效应明显, ron随之增加。根据这个来设计开关管Req。

ron随Vin的变换,反映衬偏效应的影响

ron随Vin的变换,反映衬偏效应的影响

仿真MOS管寄生电容Cgg(重要,主要换算成单位面积栅电容,要熟练记住的)(对于工艺的各种参数要记住!)

最小尺寸仿真电容太小,要把管子尺寸设置大一点好看,单位面积电容=Cgg/area。不同的偏置情况下,电容值不一样。(记住大概数量级就好?)

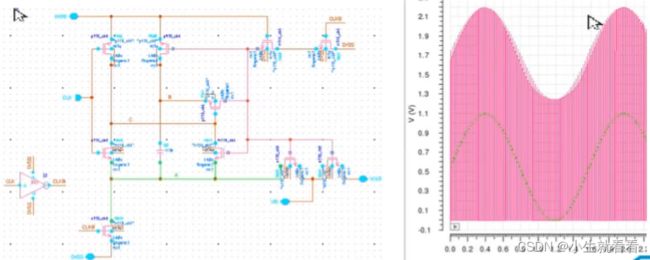

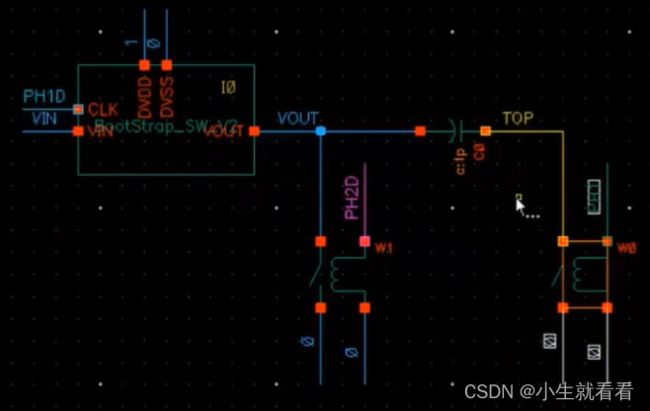

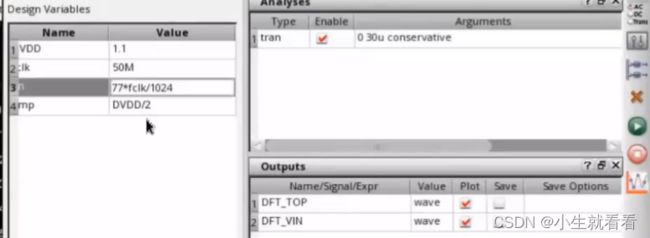

仿真BootstrapDFT

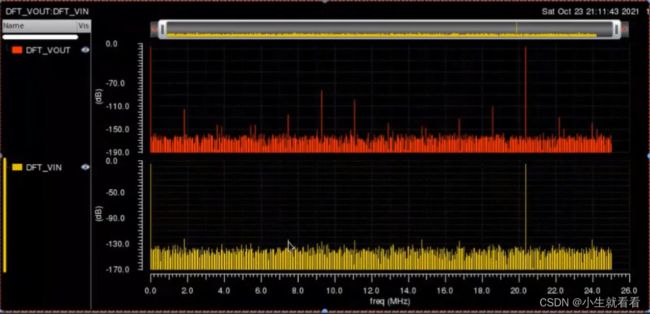

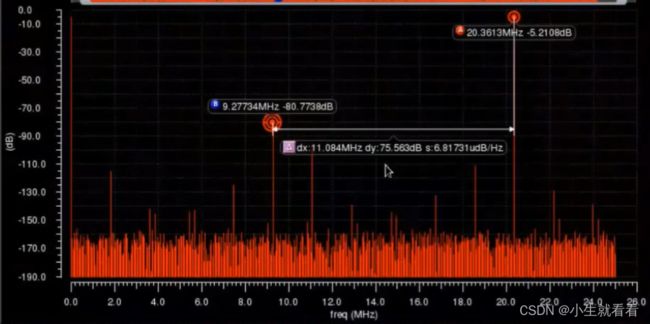

仿真BootstrapDFT,CLK=50MHz,fin=20MHz左右,确定fs,逼近fin。还要跑不同PVT下的性能。

电容非理想效应——沟道电荷和时钟馈通。Gate的电压变化是很大的(△Vg=Vin+VDD),当Gate电压拉倒0的时候,沟道电荷要泄放出去,会影响到Vout;同时变化频率为CLK,CLK频率高了也会耦合到输出。因为该效应还和Vin有关,会影响线性度。

信号和谐波差值达到了75dB,和噪底差值160dB,都高于十位的62dB,符合要求

信号和谐波差值达到了75dB,和噪底差值160dB,都高于十位的62dB,符合要求

确定抬升电容C的大小

电荷守恒的时候,抬升电容C会通过B点的PMOS管和DRV_Gate节点的寄生电容发生电荷共享。因此需要计算出DRV_Gate点的电容大小。其中Drain端的电容小,可以忽略。仿真DRV_Gate点连接到MOS栅极的各个MOS管的Cgg。升压电容比Cgg至少大两个数量级(一般1pF就够了)。

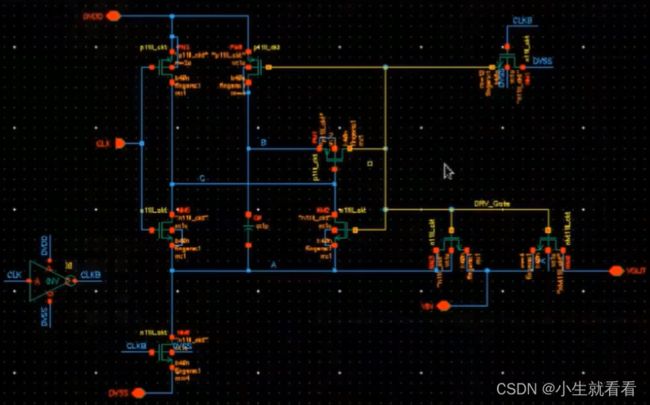

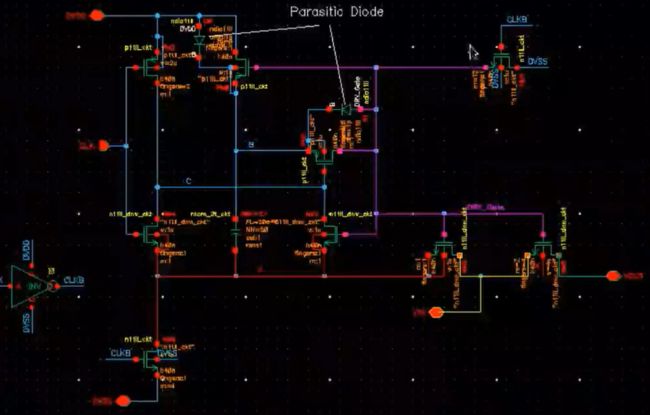

Bootstrap开关

Bootstrap开关

确定CB的上拉下拉MOS管尺寸

这两个MOS管作用是在CLK=0的时候,对电容C进行复位的(BOT=0,TOP=VDD),对于CLK=50Mhz,50%占空比而言,一半是10ns。要在10ns之内,将C复位到足够的精度。前面说了,N*tao,对应多少精度(10位,需要7*tao建立到10位精度)。这里给10个tao,即10ns=10*tao,tao=1ns。tao=Req*CB。两个管子串联Req=2*ron。CB=1pF。计算得到Req=1K,ron=500Ohm即可。前面仿真MOS管导通电阻的方法,确定N和P管子尺寸。

确定CLK反相C点NMOS尺寸——不重要的管子

CLK从0变为1(上升沿)瞬间,DRV_Gate还是0,开关断开的,Vin还没传到A点,A=0 。将C点放电(此时C和B都为VDD),当C点降到 Vbc>Vtp 时,PMOS导通发生电荷共享。DRV_Gate拉高,开关打开,Vin传到A点,拉高了A点电压。A点电压升高会导致CLK下拉C点的NMOS管截止(Vgs变小),但是此时DRV_Gate已经较高了,C点另一个NMOS会打开,把C拉成和A一样(把C点放电)。

总的来说:两个NMOS管作用是,在CLK=1的时候,将C点和A点拉到一样(给C点放电),两个管子分时工作的,一开始A点电压低(=0),C左NMOS开启,后来A点电压高(=Vin),C右NMOS开启。因此尺寸可以取的小一点,无所谓。

Diode连接(衬底连接)

PMOS的衬底连到三端的最高电位。(看前文的解释)

开关管接A点。

下级板采样

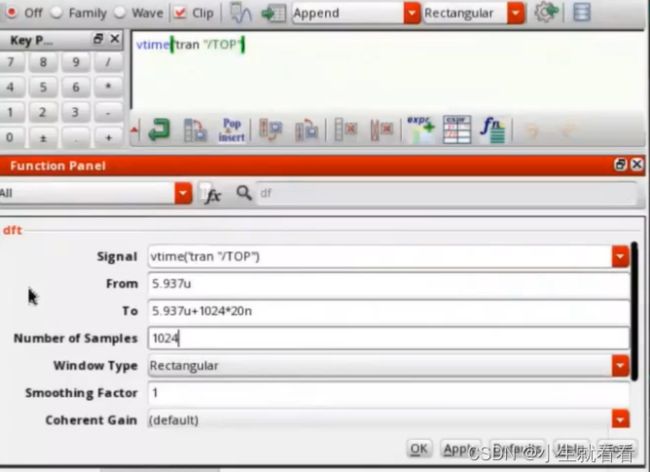

做DFT时,取的是,采样稳定后的值,怎么取:

选定初始时间,以Ts=1/fs为时间间隔采样,具体做法如下。

初始时刻是稳定的采样电压,采1024个点,间隔20n

初始时刻是稳定的采样电压,采1024个点,间隔20n  DFT固定fs,逼近fin,fin=M*fs/N,通过控制M来取fin,N确定精度

DFT固定fs,逼近fin,fin=M*fs/N,通过控制M来取fin,N确定精度

怎么计算SNR:

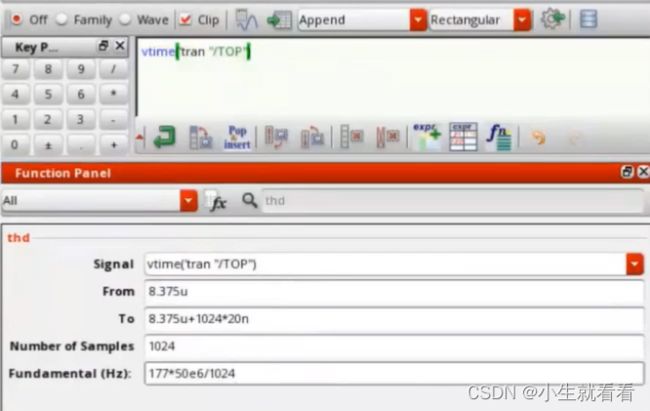

取采样wave,send to calculator,函数 thd ,再取dB

from to number fin和前面做DFT差不多

from to number fin和前面做DFT差不多

取的点数*2,噪底下降3dB

-------------更新----------------

有人疑惑耐压问题,开关管Gate最高电压达到了2*Vdd。

考虑的是能量的累计,不是瞬间的。电压要对时间积分,对于开关,有一半时间导通,一半时间关断,即使最大电压2*Vdd,平均下来也就一个Vdd。

-----------更新-----------------

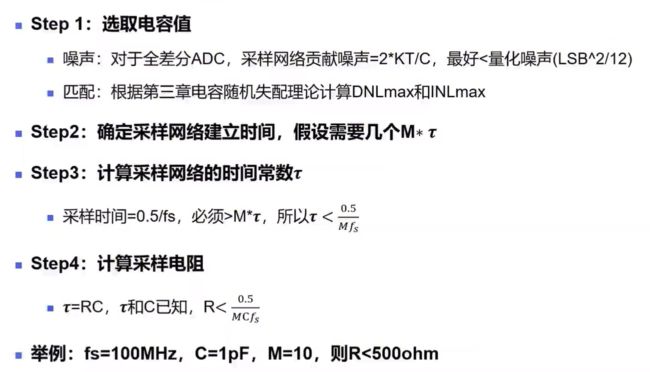

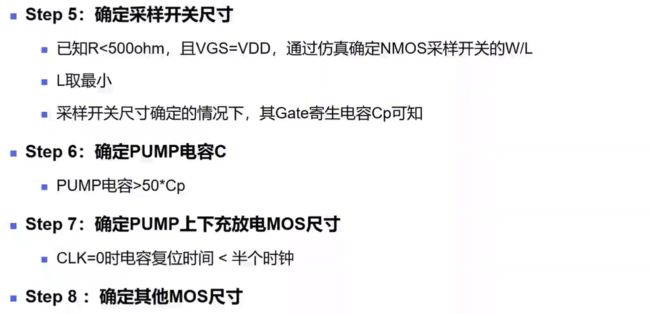

Bootstrap开关中MOS管尺寸选取

这里的2*KT/C指的是噪声功率,要是换算成电压的话,要开方sqrt。

计算得到R之后,通过仿真单个开关MOS管,确定尺寸,注意,各种corner都要考虑到,PVT。

采样开关确定,其寄生电容也确定,可以看看和C电荷共享的寄生电容Cp尺寸,C至少大一个数量级吧。然后还要确定上拉下拉MOS尺寸。上下拉MOS管和Pump电容C组成一个RC网络,R为两个MOS管电阻之和。和第一步一样,需要在0.5*Ts内复位到10*tao的精度,求出RC。同时为了保证驱动能力相同,可能PMOS尺寸会更大一些。Pump电容小了,节省面积,但是可能复位不到Vdd,大了复位更准。

自举开关

自举开关

然后确定那个右上角的泄放NMOS管,他负责将CLK下降沿拉倒0,其尺寸越大,CLK下降越快,可能寄生效应, 馈通效应越大。时钟馈通,沟道电荷可能都跟TOP点的放电速度有关系,而这个管子就是控制放电速度的。快放慢放都有。

关键管子就这几个,其余的随便取值,但是从版图的角度,如果面积要求不是非常非常严格,为了好画,管子尺寸不要差太大,1u,2u,3u,4u。。。这样,不要整个几十u的。