FPGA 串口中断_基于FPGA的轻量级RISCV SoC

项目来源:2019年第三届全国大学生FPGA创新设计竞赛一、设计概述 1.1设计目的随着以RISC-V(RISC,精简指令集计算机;V表示为第五代)为代表的新型开源ISA(instruction set architecture,指令集架构)的出现,使得国内在处理器研发上有了新的ISA可供选择。国内在处理器研发方面的人才需求也越来越多。但是由于目前国内计算机科学教学用具主要是8086微机和51单片机等陈旧的架构,这些处理器不仅缺乏相关的底层逻辑实现,而且指令架构过于陈旧不具备参考价值。综上所述,为了方便老师教学和学生由浅入深地了解处理器设计,需要一种开源的,简单的,同时使用了新型ISA的处理器,并且基于此集成一个SoC。1.2应用领域本设计可以运用在从数字逻辑基础教学到计算机组成及原理等多个场合。例如在进行数字逻辑基础教学的时候,可以让学生设计一款自定义外设,由于本SoC的内部总线时序非常简单,学生可以轻松设计出外设,这样既锻炼了学生的数字逻辑设计能力,又可以让学生理解数字逻辑和计算机系统之间的联系。同时,在计算机组成及原理的课程上,老师可以通过本处理器配套的汇编软件和仿真器联合进行汇编代码仿真,并且还可以使用配套的FPGA硬件进行无缝上板调试。1.3主要技术特点本作品着眼简单、易学,在硬件平台上不仅自研了一个简单的处理器内核-PRV332SV0,同时也基于这个内核配套搭建了一个SoC-PVS332,底层HDL代码具备完全自主知识产权。在软件方面,我们同时重构了一个简单易用的IDE,该IDE包含汇编和链接的功能,不仅可以联合仿真软件进行联合汇编代码仿真,而且可以直接生成机器码文件上板调试。学生在学习的时候可以根据自己的需求对任意一个模块进行时序仿真,从根本上解决了处理器-汇编指令-操作外设 这一道难以理解的槛。1.4关键性能指标本作品实现了一个RISCV处理器内核,该处理器是使用状态机实现的,完全兼容RISCV32I指令集和A拓展指令,并且具有MMU和RISCV定义的大部分CSR。另外为了简单没有加入缓存和流水线等机制。该处理器的板上工作频率为33MHz,平均CPI为7,实测运行MIPS值为6MIPS。基于该处理器集成了一个SoC,SoC里面集成了4KB的片上内存、4KB的程序储存器、八个SPI收发器、最多支持128个中断源的中断控制器、系统定时器、两对具备FIFO功能的UART收发器、22个GPIO、最大寻址范围16MB的外置拓展卡控制器。这些外设通过类AHB总线和一个总线交换机连接起来,内部总线吞吐量最大为133MB/s。为了尽可能适应教学和轻量化的需求,上述模块均为自主研发。配套研制的IDE重构了汇编器和链接器,集成了包含汇编器-链接器等多项功能,不仅可以和仿真器配合进行汇编代码仿真,还可以直接生成机器码文件实现上板调试。除了上述功能,该IDE还可以和自主研制的调试器进行无线连接,可以实现回传系统板上数据和烧录外部flash的功能。 二、系统组成及功能说明 2.1系统介绍本系统总体可以分为硬件端和PC机端,其中硬件部分又可分为FPGA核心模块、系统主板和调试器,系统框图如图1所示:

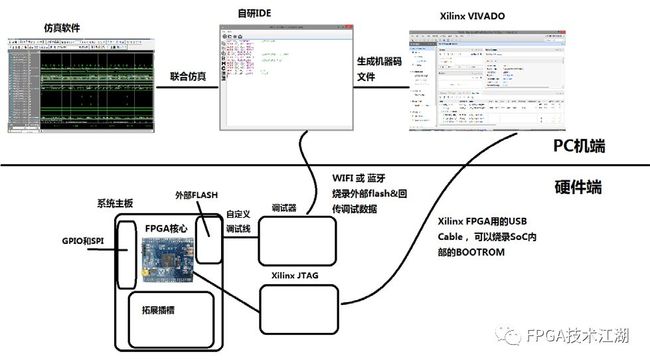

项目来源:2019年第三届全国大学生FPGA创新设计竞赛一、设计概述 1.1设计目的随着以RISC-V(RISC,精简指令集计算机;V表示为第五代)为代表的新型开源ISA(instruction set architecture,指令集架构)的出现,使得国内在处理器研发上有了新的ISA可供选择。国内在处理器研发方面的人才需求也越来越多。但是由于目前国内计算机科学教学用具主要是8086微机和51单片机等陈旧的架构,这些处理器不仅缺乏相关的底层逻辑实现,而且指令架构过于陈旧不具备参考价值。综上所述,为了方便老师教学和学生由浅入深地了解处理器设计,需要一种开源的,简单的,同时使用了新型ISA的处理器,并且基于此集成一个SoC。1.2应用领域本设计可以运用在从数字逻辑基础教学到计算机组成及原理等多个场合。例如在进行数字逻辑基础教学的时候,可以让学生设计一款自定义外设,由于本SoC的内部总线时序非常简单,学生可以轻松设计出外设,这样既锻炼了学生的数字逻辑设计能力,又可以让学生理解数字逻辑和计算机系统之间的联系。同时,在计算机组成及原理的课程上,老师可以通过本处理器配套的汇编软件和仿真器联合进行汇编代码仿真,并且还可以使用配套的FPGA硬件进行无缝上板调试。1.3主要技术特点本作品着眼简单、易学,在硬件平台上不仅自研了一个简单的处理器内核-PRV332SV0,同时也基于这个内核配套搭建了一个SoC-PVS332,底层HDL代码具备完全自主知识产权。在软件方面,我们同时重构了一个简单易用的IDE,该IDE包含汇编和链接的功能,不仅可以联合仿真软件进行联合汇编代码仿真,而且可以直接生成机器码文件上板调试。学生在学习的时候可以根据自己的需求对任意一个模块进行时序仿真,从根本上解决了处理器-汇编指令-操作外设 这一道难以理解的槛。1.4关键性能指标本作品实现了一个RISCV处理器内核,该处理器是使用状态机实现的,完全兼容RISCV32I指令集和A拓展指令,并且具有MMU和RISCV定义的大部分CSR。另外为了简单没有加入缓存和流水线等机制。该处理器的板上工作频率为33MHz,平均CPI为7,实测运行MIPS值为6MIPS。基于该处理器集成了一个SoC,SoC里面集成了4KB的片上内存、4KB的程序储存器、八个SPI收发器、最多支持128个中断源的中断控制器、系统定时器、两对具备FIFO功能的UART收发器、22个GPIO、最大寻址范围16MB的外置拓展卡控制器。这些外设通过类AHB总线和一个总线交换机连接起来,内部总线吞吐量最大为133MB/s。为了尽可能适应教学和轻量化的需求,上述模块均为自主研发。配套研制的IDE重构了汇编器和链接器,集成了包含汇编器-链接器等多项功能,不仅可以和仿真器配合进行汇编代码仿真,还可以直接生成机器码文件实现上板调试。除了上述功能,该IDE还可以和自主研制的调试器进行无线连接,可以实现回传系统板上数据和烧录外部flash的功能。 二、系统组成及功能说明 2.1系统介绍本系统总体可以分为硬件端和PC机端,其中硬件部分又可分为FPGA核心模块、系统主板和调试器,系统框图如图1所示:  图 1 系统框图硬件端的FPGA核心模块里面实现了了一个完全自主研发的SoC,内置一个33MHz的CPU核心和GPIO、SPI收发器、UART收发器、系统定时器、拓展卡控制器等多个外设。硬件端的系统主板上包含了可以插接FPGA核心板的插座、SPI和GPIO接口和板载的FLASH芯片,同时提供了一个自定义调试接口和自研的调试器相连接,系统可以通过这个自定义调试接口向调试器发送数据,然后调试器可以通过WIFI或蓝牙向PC端的IDE回传数据。调试器部分不仅可以回传主板送回来的数据,也可以根据电脑端的命令对系统复位和烧录系统主板上的外部flash,这样一来该系统具备两种启动方式:1、直接从内部的BOOTROM里面启动。2、 从内置的BOOTROM启动后运行预先设定好的BOOTLOADER程序,加在外部flash到内存里,然后执行加载进来的程序。PC端我们完全自主研制了一个IDE,完全重构了汇编器算法。同时我们添加了多项功能,不仅可以编辑RISCV汇编,还可以生成多种文件类型以供仿真和烧录。2.2 各模块介绍2.2.1 FPGA部分本次使用的FPGA核心板是XC7S15,FPGA芯片一共有8000可用LUT6,核心板一共有96个可用IO,核心板如图2所示:

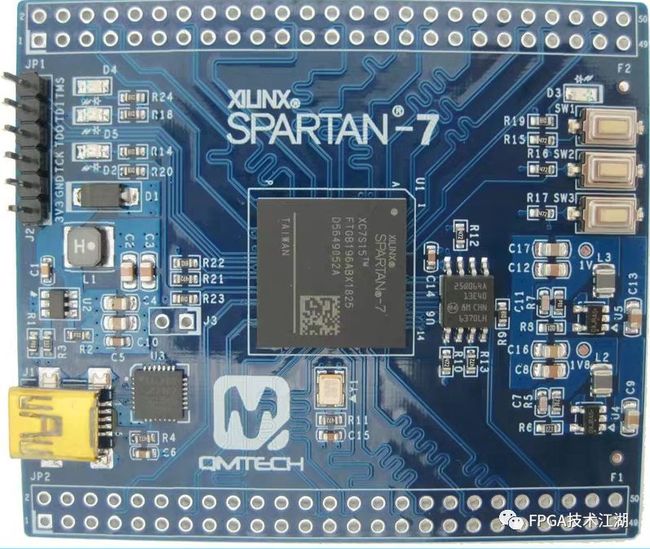

图 1 系统框图硬件端的FPGA核心模块里面实现了了一个完全自主研发的SoC,内置一个33MHz的CPU核心和GPIO、SPI收发器、UART收发器、系统定时器、拓展卡控制器等多个外设。硬件端的系统主板上包含了可以插接FPGA核心板的插座、SPI和GPIO接口和板载的FLASH芯片,同时提供了一个自定义调试接口和自研的调试器相连接,系统可以通过这个自定义调试接口向调试器发送数据,然后调试器可以通过WIFI或蓝牙向PC端的IDE回传数据。调试器部分不仅可以回传主板送回来的数据,也可以根据电脑端的命令对系统复位和烧录系统主板上的外部flash,这样一来该系统具备两种启动方式:1、直接从内部的BOOTROM里面启动。2、 从内置的BOOTROM启动后运行预先设定好的BOOTLOADER程序,加在外部flash到内存里,然后执行加载进来的程序。PC端我们完全自主研制了一个IDE,完全重构了汇编器算法。同时我们添加了多项功能,不仅可以编辑RISCV汇编,还可以生成多种文件类型以供仿真和烧录。2.2 各模块介绍2.2.1 FPGA部分本次使用的FPGA核心板是XC7S15,FPGA芯片一共有8000可用LUT6,核心板一共有96个可用IO,核心板如图2所示:  图 2 核心板FPGA中实现的SoC框图如图3所示:

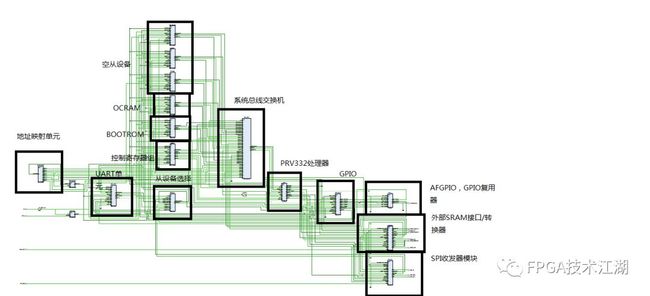

图 2 核心板FPGA中实现的SoC框图如图3所示:  图3 SoC原理框图在这个FPGA里面我们独立研发了一个RISCV处理器核心并基于这个核心自主搭建了一个SoC。该SoC集成了4KB的片上内存、4KB的程序储存器、八个SPI收发器、最多支持128个中断源的中断控制器、系统定时器、两对具备FIFO功能的UART收发器、22个GPIO、最大寻址范围16MB的外置拓展卡控制器。这些外设通过类AHB总线和一个总线交换机连接起来,内部总线吞吐量最大为133MB/s。为了尽可能适应教学和轻量化的需求,上述模块均为自主研发。图4为FPGA中实现SoC全貌的RTL视图:

图3 SoC原理框图在这个FPGA里面我们独立研发了一个RISCV处理器核心并基于这个核心自主搭建了一个SoC。该SoC集成了4KB的片上内存、4KB的程序储存器、八个SPI收发器、最多支持128个中断源的中断控制器、系统定时器、两对具备FIFO功能的UART收发器、22个GPIO、最大寻址范围16MB的外置拓展卡控制器。这些外设通过类AHB总线和一个总线交换机连接起来,内部总线吞吐量最大为133MB/s。为了尽可能适应教学和轻量化的需求,上述模块均为自主研发。图4为FPGA中实现SoC全貌的RTL视图:  图 4 SoC的RTL视图2.2.1.1 PRV332处理器内核

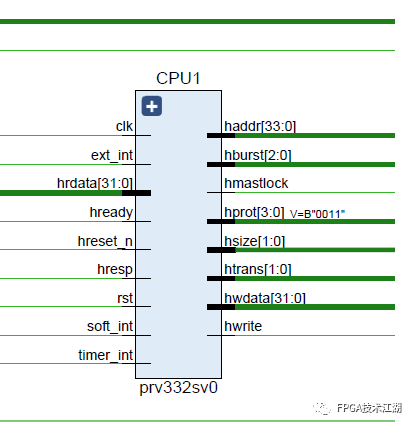

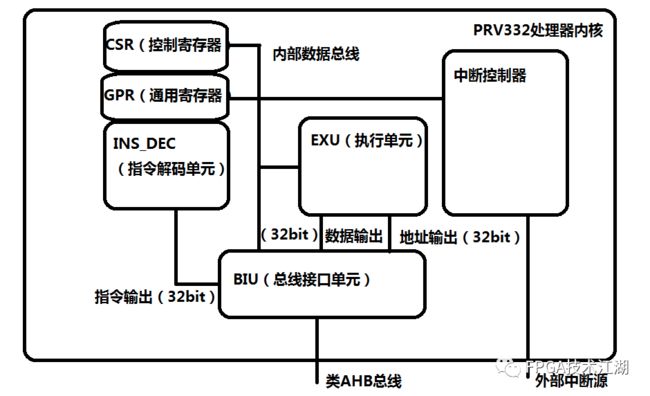

图 4 SoC的RTL视图2.2.1.1 PRV332处理器内核  图5 CPU内核整个SoC的PRV332处理器核心如图5所示,PRV332SV0处理器内核是一款支持RISCV-32 I和A拓展指令集,完全实现RISCV定 义的所有功能的处理器,不仅具备机器模式(M)模式下运行,还支持虚拟内存MMU 和系统(S)用户(U)模式,理论上完全具备运行类linux系统的能力。这款处理器内核主要由BIU(总线接口单元),EXU(执行单元),INS-CSR-GPR(指 令-CSR-通用寄存器单元),中断控制器组成,简单原理框图如图6所示。

图5 CPU内核整个SoC的PRV332处理器核心如图5所示,PRV332SV0处理器内核是一款支持RISCV-32 I和A拓展指令集,完全实现RISCV定 义的所有功能的处理器,不仅具备机器模式(M)模式下运行,还支持虚拟内存MMU 和系统(S)用户(U)模式,理论上完全具备运行类linux系统的能力。这款处理器内核主要由BIU(总线接口单元),EXU(执行单元),INS-CSR-GPR(指 令-CSR-通用寄存器单元),中断控制器组成,简单原理框图如图6所示。  图6 CPU原理框图整个CPU以状态机的方式运行,常规指令需要6T:T0:BIU准备开始下一条指令的地址。T1:BIU(总线接口单元)发出地址和总线控制信号。T2:BIU(总线接口单元)根据总线上的信号(访问失败信号、准备好信号)选择是否存入总线上的数据,若总线访问失败,则跳转到T10,若准备好信号为0,则保持T2状态,若准备好为高,则寄存总线上的数据并进入下一状态。T3:BIU发出准备好信号, 同时把指令通过BIU的指令输出总线输出给指令解码单元(INS_DEC)开始指令解码。T4:EXU开始动作,常规的加减法和逻辑运算将在这个周期内完成,如果是移位指令等则需要多个周期才能完成。T5:写回阶段,CPU内部的寄存器根据指令译码器译码结果进行寄存,同时PC(程序计数器)值在这个阶段被更改,指向下一条要被执行的指令的位置。如果在这个执行阶段中断控制器接受了某个外部中断,则跳到T10。当处理器遇到内存访问指令,需要增加额外的四个执行周期 T6-T9。T6:BIU准备开始下一条指令的地址。T7:BIU(总线接口单元)发出地址和总线控制信号。T8:BIU(总线接口单元)根据总线上的信号(访问失败信号、准备好信号)选择是否存入总线上的数据,若总线访问失败,则跳转到T10,若准备好信号为0,则保持T2状态,若准备好为高,则寄存总线上的数据并进入下一状态。T9:BIU发出准备好信号, 同时把数据放在内部数据总线上。当处理器遇到中断或者发生异常,需要增加一个执行周期T10,T10可以插入到以上执行周期的T2或T5或T8之后。在T10里处理器将根据错误类型将PC值自动拨到对应的中断向量上,同时储存当前发生异常的PC值和异常值到MEPC和MTVAL寄存器里。*关于RISCV的中断和异常处理可参考《The RISC-V Instruction Set Manual Volume II : Privileged Architecture》2.2.1.2 BOOTROM(程序只读储存器)

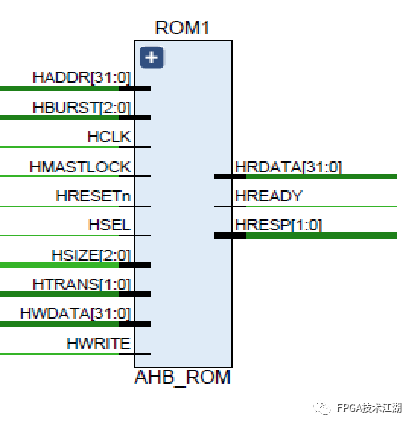

图6 CPU原理框图整个CPU以状态机的方式运行,常规指令需要6T:T0:BIU准备开始下一条指令的地址。T1:BIU(总线接口单元)发出地址和总线控制信号。T2:BIU(总线接口单元)根据总线上的信号(访问失败信号、准备好信号)选择是否存入总线上的数据,若总线访问失败,则跳转到T10,若准备好信号为0,则保持T2状态,若准备好为高,则寄存总线上的数据并进入下一状态。T3:BIU发出准备好信号, 同时把指令通过BIU的指令输出总线输出给指令解码单元(INS_DEC)开始指令解码。T4:EXU开始动作,常规的加减法和逻辑运算将在这个周期内完成,如果是移位指令等则需要多个周期才能完成。T5:写回阶段,CPU内部的寄存器根据指令译码器译码结果进行寄存,同时PC(程序计数器)值在这个阶段被更改,指向下一条要被执行的指令的位置。如果在这个执行阶段中断控制器接受了某个外部中断,则跳到T10。当处理器遇到内存访问指令,需要增加额外的四个执行周期 T6-T9。T6:BIU准备开始下一条指令的地址。T7:BIU(总线接口单元)发出地址和总线控制信号。T8:BIU(总线接口单元)根据总线上的信号(访问失败信号、准备好信号)选择是否存入总线上的数据,若总线访问失败,则跳转到T10,若准备好信号为0,则保持T2状态,若准备好为高,则寄存总线上的数据并进入下一状态。T9:BIU发出准备好信号, 同时把数据放在内部数据总线上。当处理器遇到中断或者发生异常,需要增加一个执行周期T10,T10可以插入到以上执行周期的T2或T5或T8之后。在T10里处理器将根据错误类型将PC值自动拨到对应的中断向量上,同时储存当前发生异常的PC值和异常值到MEPC和MTVAL寄存器里。*关于RISCV的中断和异常处理可参考《The RISC-V Instruction Set Manual Volume II : Privileged Architecture》2.2.1.2 BOOTROM(程序只读储存器)  图7 BOOT-ROMPVS332具有一个片上BOOT-ROM,如图7,在BOOT-ROM里面预置了开机启动代码,系统复位后处理器首先执行该ROM里面的程序,通过修改该BOOT-ROM里面程序的内容可以实现多种功能。2.2.1.3 OCRAM(片上内存)

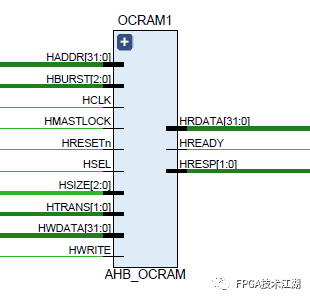

图7 BOOT-ROMPVS332具有一个片上BOOT-ROM,如图7,在BOOT-ROM里面预置了开机启动代码,系统复位后处理器首先执行该ROM里面的程序,通过修改该BOOT-ROM里面程序的内容可以实现多种功能。2.2.1.3 OCRAM(片上内存)  图8 OCRAMPVS332具备一个4K字节的片上RAM,如图8所示,该内存为同步SRAM,可以在2T周期内读写数据,工作频率和CPU同步。具备比较高的读写带宽。可以在系统没有拓展内存的情况下使用。2.2.1.4 SPI收发器

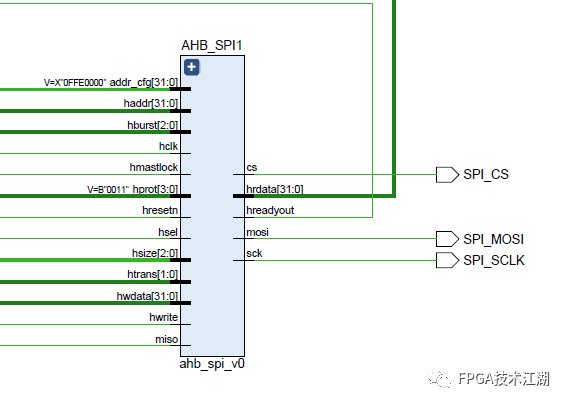

图8 OCRAMPVS332具备一个4K字节的片上RAM,如图8所示,该内存为同步SRAM,可以在2T周期内读写数据,工作频率和CPU同步。具备比较高的读写带宽。可以在系统没有拓展内存的情况下使用。2.2.1.4 SPI收发器  图9 SPI收发器PVS332具备一个硬件SPI收发器,如图9所示,可以使用额外的门电路可以同时管理八个从设备。以下截图来自于《PVS332处理器编程手册》,描述的是SPI收发器的地址和操作,分别如图10、图11所示。

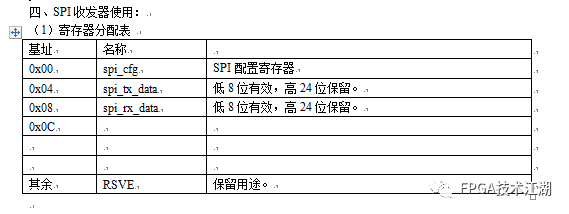

图9 SPI收发器PVS332具备一个硬件SPI收发器,如图9所示,可以使用额外的门电路可以同时管理八个从设备。以下截图来自于《PVS332处理器编程手册》,描述的是SPI收发器的地址和操作,分别如图10、图11所示。  图10 SPI收发器寄存器

图10 SPI收发器寄存器  图11 SPI寄存器定义2.2.1.5 EXT-SLOT(拓展插槽)

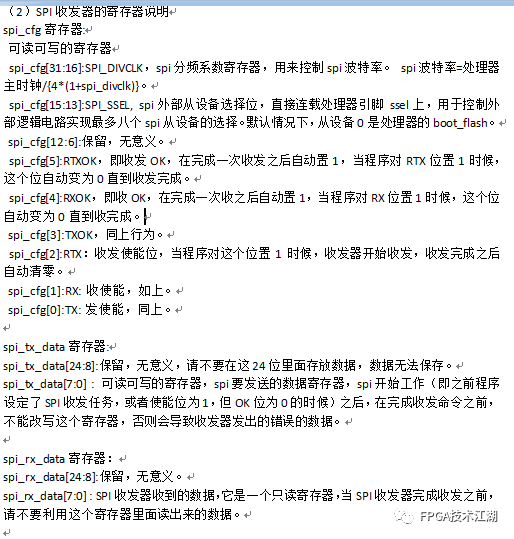

图11 SPI寄存器定义2.2.1.5 EXT-SLOT(拓展插槽)  图12 拓展插槽适配器PVS332通过该适配器,如图12所示,支持最多8个,每个2MB的多功能拓展插槽,这些插槽都支持等待状态,同时插槽的地址直接被映射在处理器外部地址里面,程序可以直接访问到这些插槽上面的设备。拓展槽使用32个双向IO作为数据总线(SRAM_Data),22条地址总线(SRAM_Add),4条字节选择线(SRAM_BSEL),外部设备准备好信号线(rdy),读写信号线(SRAM_OE,SRAM_WR)和外部片选信号线(SRAM_CS)。外部总线读写分四个周期。(a)读时序当PVS332处理器内置的PRV332SV0处理器访问的内存属于外部储存器时,PVS332自动将内存选择到外部,进入读周期。T1:SRAM_CS拉低,SRAM_OE拉低,SRAM_Add送出地址,SRAM_BSEL的某几个位拉低以指示是哪个字节被读写。在下一个时钟上升沿进入T2状态T2:保持T1状态,在下一个时钟上升沿进入T3状态。T3:保持T2状态,当rdy=1时候,在下一个时钟沿进入T4状态,否则等待在T3状态T4:保持T3状态,在T4周期结束的时候进行数据采样,同时回到等待状态TW。(b)写时序T1:SRAM_CS拉低,SRAM_Add送出地址 ,SRAM_Data送出数据,SRAM_BSEL某几个位拉低以指示要操作哪个字节,在下一个上升沿进入T2周期。T2:SRAM_WR拉低,其余参数保持和T1一致,在下一个时钟上升沿进入T3周期。T3:保持T2状态,等待rdy信号之后在下一个时钟上升沿进入T4周期T4: SRAM_WR拉高,其余参数保持和T1一致,在下一个时钟上升沿进入TW。2.2.1.6 GPIO

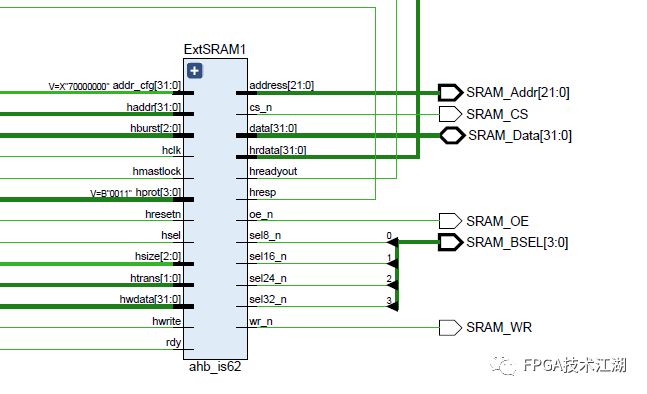

图12 拓展插槽适配器PVS332通过该适配器,如图12所示,支持最多8个,每个2MB的多功能拓展插槽,这些插槽都支持等待状态,同时插槽的地址直接被映射在处理器外部地址里面,程序可以直接访问到这些插槽上面的设备。拓展槽使用32个双向IO作为数据总线(SRAM_Data),22条地址总线(SRAM_Add),4条字节选择线(SRAM_BSEL),外部设备准备好信号线(rdy),读写信号线(SRAM_OE,SRAM_WR)和外部片选信号线(SRAM_CS)。外部总线读写分四个周期。(a)读时序当PVS332处理器内置的PRV332SV0处理器访问的内存属于外部储存器时,PVS332自动将内存选择到外部,进入读周期。T1:SRAM_CS拉低,SRAM_OE拉低,SRAM_Add送出地址,SRAM_BSEL的某几个位拉低以指示是哪个字节被读写。在下一个时钟上升沿进入T2状态T2:保持T1状态,在下一个时钟上升沿进入T3状态。T3:保持T2状态,当rdy=1时候,在下一个时钟沿进入T4状态,否则等待在T3状态T4:保持T3状态,在T4周期结束的时候进行数据采样,同时回到等待状态TW。(b)写时序T1:SRAM_CS拉低,SRAM_Add送出地址 ,SRAM_Data送出数据,SRAM_BSEL某几个位拉低以指示要操作哪个字节,在下一个上升沿进入T2周期。T2:SRAM_WR拉低,其余参数保持和T1一致,在下一个时钟上升沿进入T3周期。T3:保持T2状态,等待rdy信号之后在下一个时钟上升沿进入T4周期T4: SRAM_WR拉高,其余参数保持和T1一致,在下一个时钟上升沿进入TW。2.2.1.6 GPIO  图13 GPIOPVS332处理器支持128个GPIO, 所设计的模块如图13所示,在目前系统里面因为FPGA引脚较少,实际只使用了GPIOC的22个GPIO。GPIO有关的控制寄存器如下图14所示。

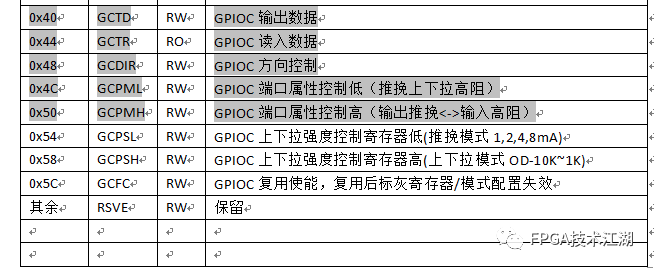

图13 GPIOPVS332处理器支持128个GPIO, 所设计的模块如图13所示,在目前系统里面因为FPGA引脚较少,实际只使用了GPIOC的22个GPIO。GPIO有关的控制寄存器如下图14所示。  图14 GPIO控制寄存器*以上设备的汇编测试程序可见SIM-TESTCODE文件夹。*以上设备的寄存器定义可以见附录中的PVS332编程手册。2.2.1.7 UART16550

图14 GPIO控制寄存器*以上设备的汇编测试程序可见SIM-TESTCODE文件夹。*以上设备的寄存器定义可以见附录中的PVS332编程手册。2.2.1.7 UART16550

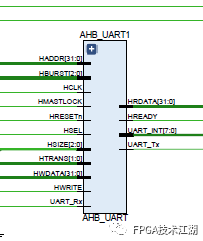

图 15 UART16550

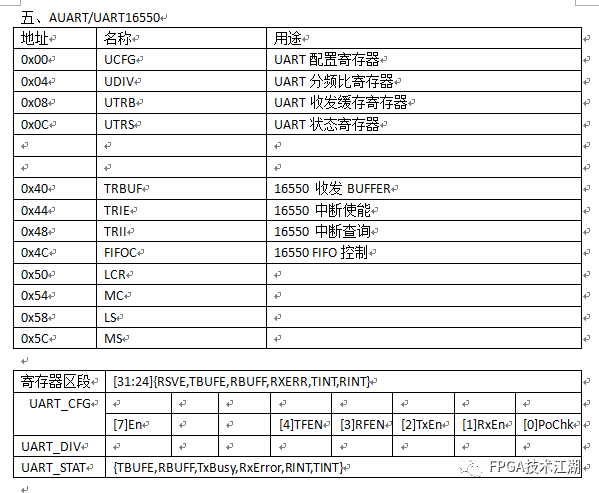

如图15,PVS332支持一个带FIFO的UART收发器,具备16字节深度的FIFO,最高支持波特 率为9600。UART16550的控制寄存器如图16所示: 图16 UART16550控制寄存器*详情可以参考附录中的PVS332编程手册2.2.1.8 控制寄存器组

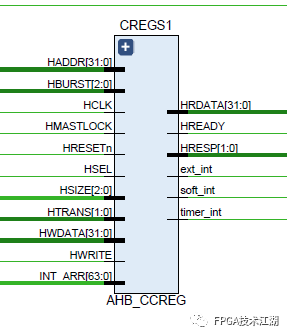

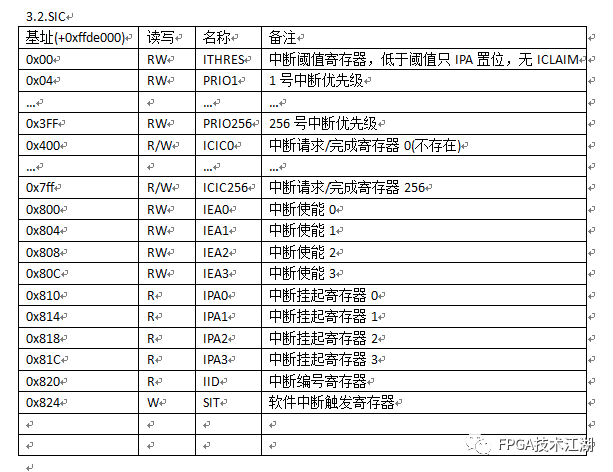

图16 UART16550控制寄存器*详情可以参考附录中的PVS332编程手册2.2.1.8 控制寄存器组  图17 控制寄存器组PVS332 SoC中有一个控制寄存器(图17 控制寄存器组)控制整个SoC的各项功能。控制寄存器组里面包含了:(1)系统定时器PVS332 SoC支持RISCV架构定义的系统的定时器(MTIME、MTIMECMP)这两个寄存器在0x0ffc0000-0x0ffc000f的空间里。该定时器在MTIME计时到MTIMECMP之后会产生定时器中断,只有当程序更新了MTIME或者MTIMECMP寄存器之后中断才会被清除。(2)软件中断控制器软件中断控制器可以让程序使用置1的方式产生同步的软件中断。(3)中断控制器(SIC)SIC可以支持最多256个外部中断的管理,并可以配置它们的优先级,由这个寄存器管理的中断源最后都连接在PRV332处理器的ext_int中断上,触发中断之后PRV332的xcause寄存器将会被更新为外部中断,软件可以查询SIC里面的中断挂起寄存器而找到是哪个外部设备发起了中断。图18是SIC的寄存器列表,详情可见附录中的《PVS332编程手册》

图17 控制寄存器组PVS332 SoC中有一个控制寄存器(图17 控制寄存器组)控制整个SoC的各项功能。控制寄存器组里面包含了:(1)系统定时器PVS332 SoC支持RISCV架构定义的系统的定时器(MTIME、MTIMECMP)这两个寄存器在0x0ffc0000-0x0ffc000f的空间里。该定时器在MTIME计时到MTIMECMP之后会产生定时器中断,只有当程序更新了MTIME或者MTIMECMP寄存器之后中断才会被清除。(2)软件中断控制器软件中断控制器可以让程序使用置1的方式产生同步的软件中断。(3)中断控制器(SIC)SIC可以支持最多256个外部中断的管理,并可以配置它们的优先级,由这个寄存器管理的中断源最后都连接在PRV332处理器的ext_int中断上,触发中断之后PRV332的xcause寄存器将会被更新为外部中断,软件可以查询SIC里面的中断挂起寄存器而找到是哪个外部设备发起了中断。图18是SIC的寄存器列表,详情可见附录中的《PVS332编程手册》  图18 SIC控制寄存器*详情可见附录中的《PVS332编程手册》。2.2.2 系统主板系统主板分为3大部分,分别为FPGA插座部分、拓展插槽部分、SPI和GPIO和flash部分。2.2.2.1 FPGA插座部分

图18 SIC控制寄存器*详情可见附录中的《PVS332编程手册》。2.2.2 系统主板系统主板分为3大部分,分别为FPGA插座部分、拓展插槽部分、SPI和GPIO和flash部分。2.2.2.1 FPGA插座部分

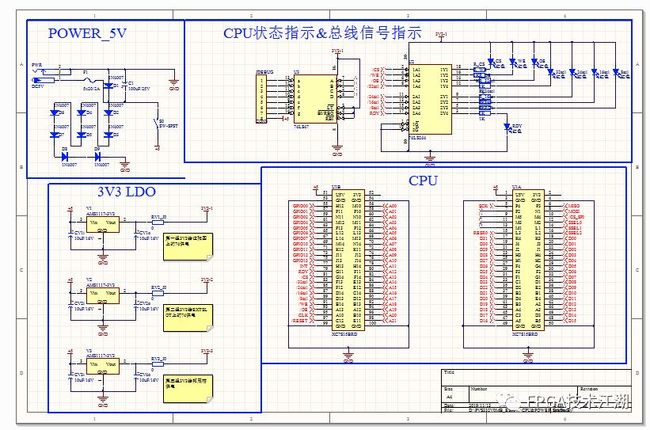

图19 FPGA核心板插座部分

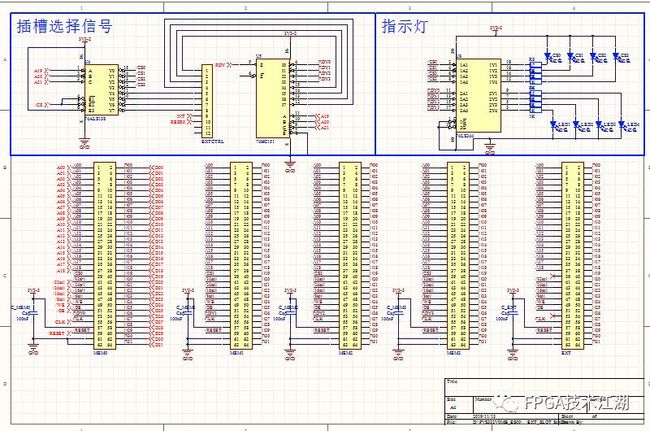

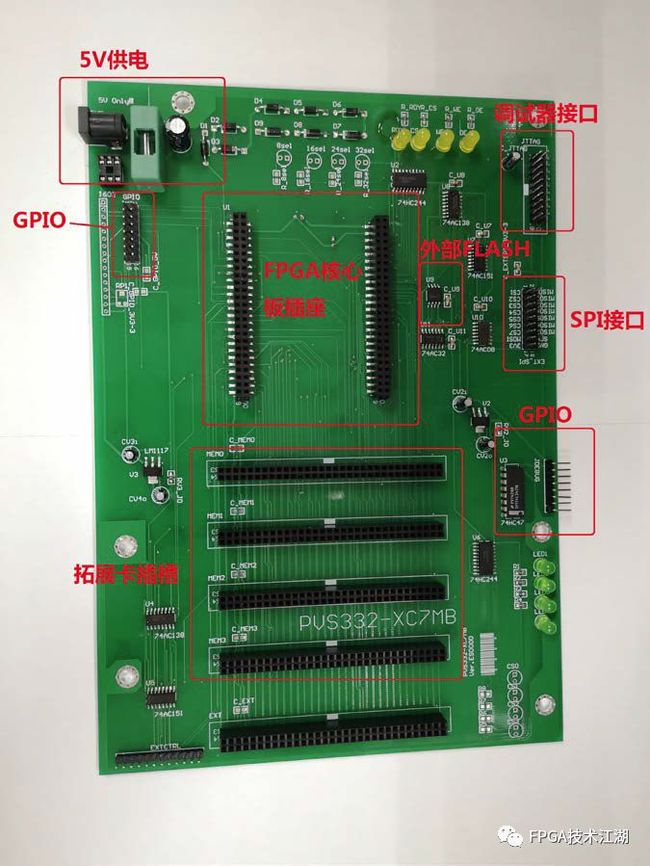

如图19,在这个部分里的CPU位置,可以插入上述FPGA核心板作为系统主板的CPU,该核心板一共有96个可用IO,我们将IO分配为:拓展卡IO、通用输入输出(GPIO)、SPI收发器 三个部分。在旁边的稳压器部分,主要为板上的逻辑芯片供电。同时我们板载了多个指示灯用于指示系统的运行状态。2.2.2.2 拓展插槽部分 图20 拓展插槽部分在拓展插槽上图20所示,我们使用32个IO作为双向数据总线,22个IO作为地址总线,4个IO作为字节选择线, 2个IO作为读写使能线,1个IO作为准备好信号输入线。总线工作频率为8MHz(FPGA工作频率33MHz时)。最大传输速度为32MB/s。为了实现多个外部设备,我们将A19-A21作为一个3-8译码器的输入信号,使用该3-8译码器获得8个译码器信号,这样外部就可以获得8个插槽的片选信号。其余的A0-A18作为地址线,配合四个字节选择线可以寻址8 * 512K * 4Byte的空间。2.2.2.3 SPI、GPIO和flash部分

图20 拓展插槽部分在拓展插槽上图20所示,我们使用32个IO作为双向数据总线,22个IO作为地址总线,4个IO作为字节选择线, 2个IO作为读写使能线,1个IO作为准备好信号输入线。总线工作频率为8MHz(FPGA工作频率33MHz时)。最大传输速度为32MB/s。为了实现多个外部设备,我们将A19-A21作为一个3-8译码器的输入信号,使用该3-8译码器获得8个译码器信号,这样外部就可以获得8个插槽的片选信号。其余的A0-A18作为地址线,配合四个字节选择线可以寻址8 * 512K * 4Byte的空间。2.2.2.3 SPI、GPIO和flash部分

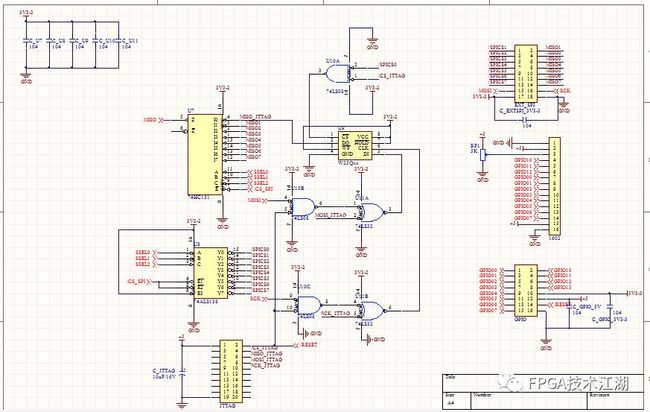

图21 SPI、IO和外部FLASH

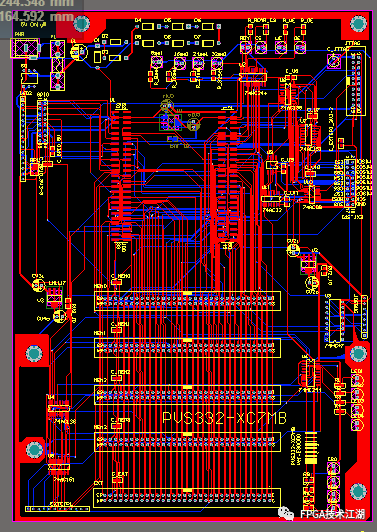

SPI部分同样使用3-8译码器作为从设备选择信号,而后使用一片8-1数据选择器作为八个SPI从设备的MISO选择。FLASH部分使用额外的74系列逻辑芯片搭建了复用器,在调试器对系统进行复位时(/RESET为低),此时复用器将FLASH的引脚切换给调试器的MOSI、MISO、SCK、CS使用。当调试器烧录FLASH完成之后,/RESET被拉高,此时该复用器将FLASH切换给主系统的SPI收发器使用。2.2.2.4 主板PCB图 图 22 主板PCB图2.2.2.5 主板实物PVS332可以搭配配套的PVS332-XC7MB主板,板上引出了七个SPI,16个GPIO和 烧录器用的插针。同时引出了四个可以直接使用的拓展槽接口和一个需要外接其它拓展电路的接口。主板实物如图23所示:

图 22 主板PCB图2.2.2.5 主板实物PVS332可以搭配配套的PVS332-XC7MB主板,板上引出了七个SPI,16个GPIO和 烧录器用的插针。同时引出了四个可以直接使用的拓展槽接口和一个需要外接其它拓展电路的接口。主板实物如图23所示:

图23 主板实物图

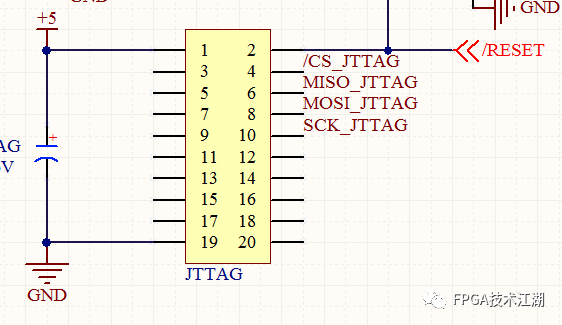

2.2.3 调试器调试器使用ESP32作为主控,使用ESP32通过蓝牙/WIFI等多种方式连接系统主板和电脑端软件。该调试器可以和电脑端配套软件联合使用,执行包括对系统主板进行复位、烧录外部FLASH、监视系统主板串口并回传数据等一系列任务。调试器通过自定义排线接口与系统主板相连接,自定义接口的引脚定义如图24所示:

图24 调试器电路

调试器通过上图中MISO,MOSI,SCK,/CS来完成对系统主板的复位和调试工作。在/RESET为0时(即系统复位), 调试器作为SPI从机,MOSI,MISO,SCK,CS引脚控制系统主板上的外部FLASH;在/RESET为高(即系统正常工作)时,MOSI,MISO,SCK为SoC的SPI收发器0引脚,此时调试器作为SPI 从机,可以监视串口数据。调试器实物如图25所示: 图25 调试实物图2.2.4内存拓展卡外置内存拓展卡是两片IS62WV51216构成的,一共2兆字节。可以插在主板上的拓展插槽内,可以让系统获得额外的2MB内存。拓展卡如图26所示:

图25 调试实物图2.2.4内存拓展卡外置内存拓展卡是两片IS62WV51216构成的,一共2兆字节。可以插在主板上的拓展插槽内,可以让系统获得额外的2MB内存。拓展卡如图26所示:  图26 内存拓展卡2.2.5 PC端IDE软件部分我们完全自主研发了一个IDE-PRV332IDE,具备编辑RISCV汇编,生成多种机器码文件的能力,可以极大的方便程序验证和调试工作。IDE界面如图27所示:

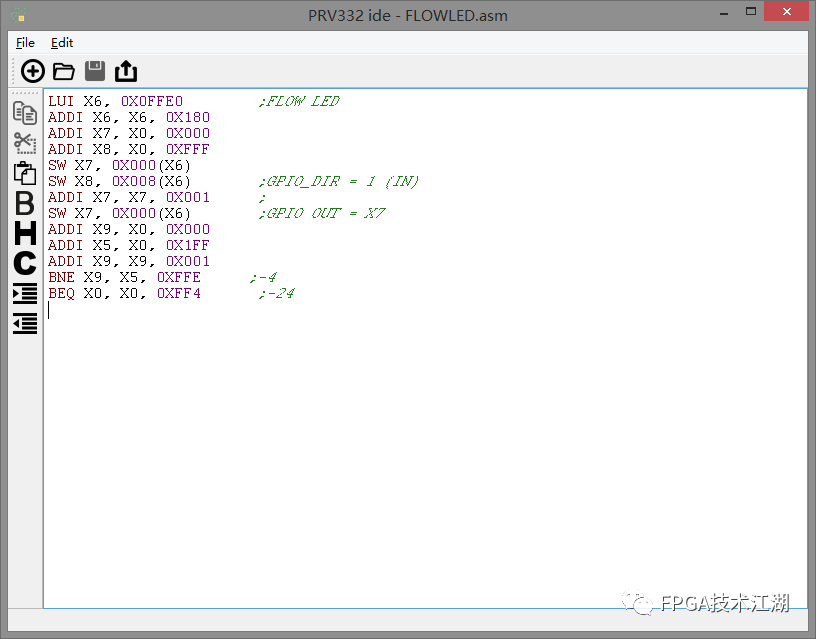

图26 内存拓展卡2.2.5 PC端IDE软件部分我们完全自主研发了一个IDE-PRV332IDE,具备编辑RISCV汇编,生成多种机器码文件的能力,可以极大的方便程序验证和调试工作。IDE界面如图27所示:

图27 IDE界面

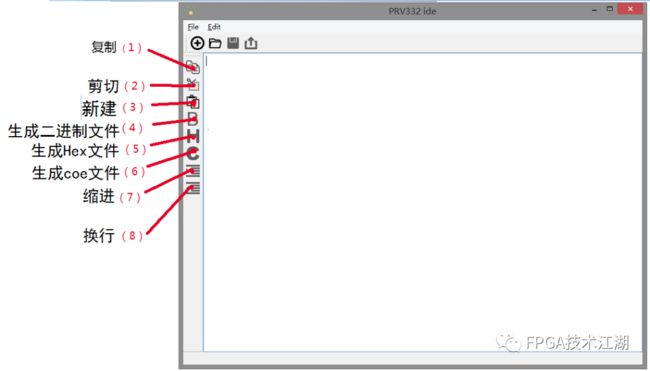

2.2.5.1 IDE各项功能介绍 图28 IDE功能如图28所示,IDE功能从上到下依次为:复制文件、剪切文件、新建文件、生成二进制文件、生成Hex文件、生成coe文件、缩进、换行。其中生成二进制文件可以让汇编代码直接被仿真器仿真;生成的Hex文件可以直接烧录到flash里面,配合SoC内部的BOOTLOADER程序使用;生成的coe文件可以作为xilinx FPGA的ROM里面的内容。2.2.5.2 IDE实现技术特点Prv332ide使用pyqt编写图形界面同时重构了原有的riscv汇编工具链,是一个总代码约2000行的轻量级prv332定制的可以直接烧录的ide.汇编工具链上抛弃传统的两遍扫描算法使用高效的一遍扫描算法,同时利用散列算法进行加速使得汇编翻译和地址分配速度非常快。不仅在速度上进行了优化,同时利用python面向对象的优点预留多个接口,配合图形界面可以直接生成用于仿真的二进制文件(直接用于modelsim仿真),coe文件(用于直接烧录xilinx的BROM),hex文件(用于直接烧录到soc的片外flash)。大大方便了验证和调试工作。图形界面使用pyqt开发,除了汇编工具链生成的之外还可以利用socket直连jttag接收soc传来的数据以及烧录工作。三、完成情况及性能参数 3.1综合完成FPGA逻辑资源占用

图28 IDE功能如图28所示,IDE功能从上到下依次为:复制文件、剪切文件、新建文件、生成二进制文件、生成Hex文件、生成coe文件、缩进、换行。其中生成二进制文件可以让汇编代码直接被仿真器仿真;生成的Hex文件可以直接烧录到flash里面,配合SoC内部的BOOTLOADER程序使用;生成的coe文件可以作为xilinx FPGA的ROM里面的内容。2.2.5.2 IDE实现技术特点Prv332ide使用pyqt编写图形界面同时重构了原有的riscv汇编工具链,是一个总代码约2000行的轻量级prv332定制的可以直接烧录的ide.汇编工具链上抛弃传统的两遍扫描算法使用高效的一遍扫描算法,同时利用散列算法进行加速使得汇编翻译和地址分配速度非常快。不仅在速度上进行了优化,同时利用python面向对象的优点预留多个接口,配合图形界面可以直接生成用于仿真的二进制文件(直接用于modelsim仿真),coe文件(用于直接烧录xilinx的BROM),hex文件(用于直接烧录到soc的片外flash)。大大方便了验证和调试工作。图形界面使用pyqt开发,除了汇编工具链生成的之外还可以利用socket直连jttag接收soc传来的数据以及烧录工作。三、完成情况及性能参数 3.1综合完成FPGA逻辑资源占用  图29 FPGA布线占用

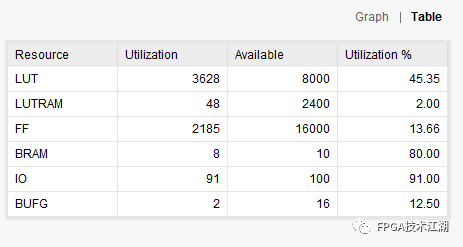

图29 FPGA布线占用  图30 FPGA资源占用图29和图30可看到,综合布线完成后共占用逻辑单元3628个,一共使用总逻辑单元数量的45.35%。片内RAM共使用8KB,占用总片内RAM资源的80%。在总的资源占用上较为良好的达到了对轻量的需求。3.2 在MODELSIM里面进行汇编代码仿真(以SPI收发器为例)首先我们在配套的汇编软件中写SPI收发器的汇编代码,图31所示:

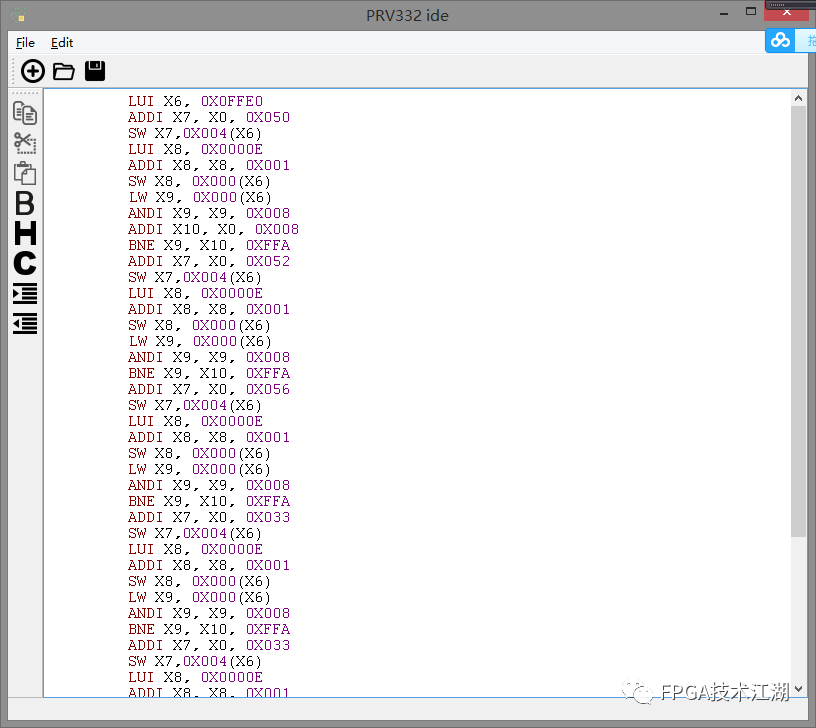

图30 FPGA资源占用图29和图30可看到,综合布线完成后共占用逻辑单元3628个,一共使用总逻辑单元数量的45.35%。片内RAM共使用8KB,占用总片内RAM资源的80%。在总的资源占用上较为良好的达到了对轻量的需求。3.2 在MODELSIM里面进行汇编代码仿真(以SPI收发器为例)首先我们在配套的汇编软件中写SPI收发器的汇编代码,图31所示:  图31 SPI收发器驱动此程序写了一个使用SPI收发器完成发送一系列字符串的程序的程序。程序流程如下:设置SPI收发器的基地址、设置要发送的数据、使能SPI收发器、检查SPI收发器的TXOK位,若为1则继续发送下一个字节的数据。其次我们使用PRV332IDE生成给modelsim仿真使用的二进制文件,如图32所示:

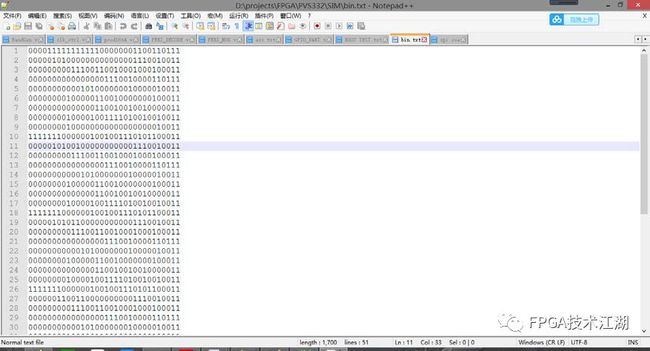

图31 SPI收发器驱动此程序写了一个使用SPI收发器完成发送一系列字符串的程序的程序。程序流程如下:设置SPI收发器的基地址、设置要发送的数据、使能SPI收发器、检查SPI收发器的TXOK位,若为1则继续发送下一个字节的数据。其次我们使用PRV332IDE生成给modelsim仿真使用的二进制文件,如图32所示:  图32 生成的二进制文件然后我们打开modelsim,直接开始仿真,可以看到SoC的SPI有关引脚上出现了我们希望看到的数据,如图33所示。

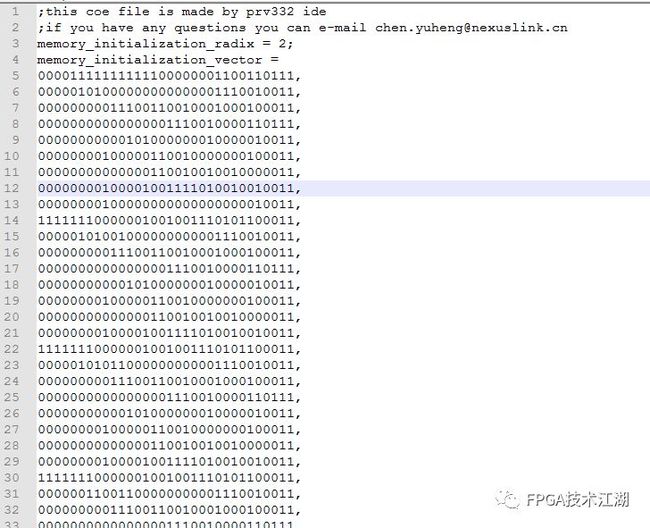

图32 生成的二进制文件然后我们打开modelsim,直接开始仿真,可以看到SoC的SPI有关引脚上出现了我们希望看到的数据,如图33所示。  图34 COE文件

图34 COE文件  图35测试电路系统启动之后可以看到从BOOTROM启动的SPI程序发出的信息,如图36所示:

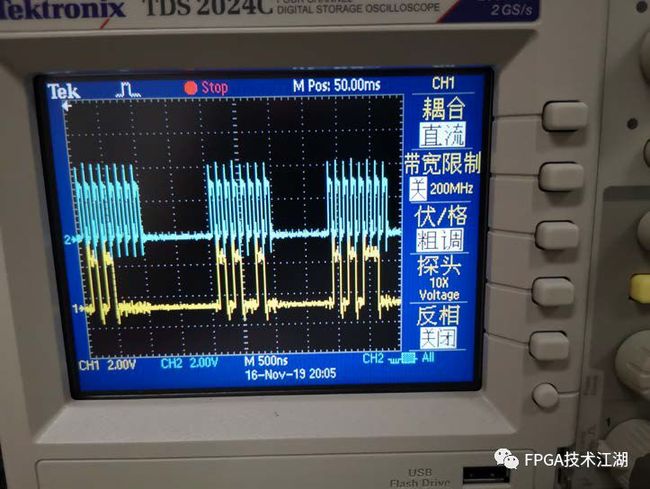

图35测试电路系统启动之后可以看到从BOOTROM启动的SPI程序发出的信息,如图36所示:  图36 启动信息同时在示波器上也可以看到SPI收发器正常工作,图37所示:

图36 启动信息同时在示波器上也可以看到SPI收发器正常工作,图37所示:  图37 示波器观察到的波形 四、总结4.1主要创新点(1)本系统完全自主研发了一个简单的SoC,主CPU同样为自主研发,抛弃了MCS51,X86等落后的指令集,采用了新型的RISCV指令集,(2)本系统同时完全自主研发了一个汇编语言IDE,在保证简单易用的前提下,实现了生成多种文件的功能,极大的方便了调试。(3)本系统的SoC不仅可以在仿真软件上运行,我们还制作了相应的系统主板,突破了目前国内同类教学用RISCV系统只有仿真文件的问题。4.2可扩展之处(1)目前只支持少量的通信设备(八个SPI一个UART),以及非常少的拓展卡设备可以用(只有一个2MB拓展内存卡,最多只能拓展16MB的外部储存空间)。(2)目前的汇编器只支持汇编语言开发,以后可以移植GCC编译器让该系统可以用于C语言编程下的微机教学。(3)目前本系统暂时不支持JTAG等调试机制,以后有望移植JTAG让调试更加简单。五、参考文献 [1]水头一寿,CPU自制入门[M].北京:人民邮电出版社,2014[2]胡振波,手把手教你设计CPU-RISC-V处理器[M].武汉:人民邮电出版社,2018[3]胡振波,RISC-V架构与嵌入式开发快速入门[M].武汉:人民邮电出版社,2018[4]夏宇闻,Verilog数字系统设计教程(第四版)[M].北京:北京航空航天大学出版社,2017[5]Andrew Waterman, Krste Asanovic, SiFive Inc.The RISC-V Instruction Set Manual Volume II :Privileged Architecture[Z].Califorina:University of California, Berkeley,July 27,2019.[6]Andrew Waterman, Krste Asanovic, SiFive Inc.The RISC-V Instruction Set Manual Volume I :Unprivileged Architecture[Z].Califorina:University of California, Berkeley,July 27,2019.END后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

图37 示波器观察到的波形 四、总结4.1主要创新点(1)本系统完全自主研发了一个简单的SoC,主CPU同样为自主研发,抛弃了MCS51,X86等落后的指令集,采用了新型的RISCV指令集,(2)本系统同时完全自主研发了一个汇编语言IDE,在保证简单易用的前提下,实现了生成多种文件的功能,极大的方便了调试。(3)本系统的SoC不仅可以在仿真软件上运行,我们还制作了相应的系统主板,突破了目前国内同类教学用RISCV系统只有仿真文件的问题。4.2可扩展之处(1)目前只支持少量的通信设备(八个SPI一个UART),以及非常少的拓展卡设备可以用(只有一个2MB拓展内存卡,最多只能拓展16MB的外部储存空间)。(2)目前的汇编器只支持汇编语言开发,以后可以移植GCC编译器让该系统可以用于C语言编程下的微机教学。(3)目前本系统暂时不支持JTAG等调试机制,以后有望移植JTAG让调试更加简单。五、参考文献 [1]水头一寿,CPU自制入门[M].北京:人民邮电出版社,2014[2]胡振波,手把手教你设计CPU-RISC-V处理器[M].武汉:人民邮电出版社,2018[3]胡振波,RISC-V架构与嵌入式开发快速入门[M].武汉:人民邮电出版社,2018[4]夏宇闻,Verilog数字系统设计教程(第四版)[M].北京:北京航空航天大学出版社,2017[5]Andrew Waterman, Krste Asanovic, SiFive Inc.The RISC-V Instruction Set Manual Volume II :Privileged Architecture[Z].Califorina:University of California, Berkeley,July 27,2019.[6]Andrew Waterman, Krste Asanovic, SiFive Inc.The RISC-V Instruction Set Manual Volume I :Unprivileged Architecture[Z].Califorina:University of California, Berkeley,July 27,2019.END后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注职业+方向+名字进群

FPGA技术江湖QQ交流群

备注地区+职业+方向+名字进群