allwinner boot0启动

目录

路径:u-boot-2018/arch/arm/cpu/armv7/sunxi/u-boot-spl.lds

路径:u-boot-2018/arch/arm/cpu/armv7/start.S

路径:u-boot-2018/arch/arm/lib/crt0.S

路径:u-boot-2014.07\common\board_f.c

路径:u-boot-2014.07\common\board_r.c

U_BOOT_CMD(烧写函数)

Uboot用户自定义程序(未找到被调用的位置)

SUNXI_USB

结构体申明

结构体定义

dram_data_recv_finish

Uboot中添加环境变量

路径:u-boot-2018/arch/arm/cpu/armv7/sunxi/u-boot-spl.lds

/* SPDX-License-Identifier: GPL-2.0+ */

/*

* (C) Copyright 2012

* Allwinner Technology Co., Ltd.

* Tom Cubie

*

* Based on omap-common/u-boot-spl.lds:

*

* (C) Copyright 2002

* Gary Jennejohn, DENX Software Engineering,

*

* (C) Copyright 2010

* Texas Instruments,

* Aneesh V

*/

MEMORY { .sram : ORIGIN = CONFIG_SPL_TEXT_BASE,\

LENGTH = CONFIG_SPL_MAX_SIZE }

MEMORY { .sdram : ORIGIN = CONFIG_SPL_BSS_START_ADDR, \

LENGTH = CONFIG_SPL_BSS_MAX_SIZE }

OUTPUT_FORMAT("elf32-littlearm", "elf32-littlearm", "elf32-littlearm")

OUTPUT_ARCH(arm)

ENTRY(_start)

SECTIONS

{

.text :

{

__start = .;

*(.vectors)

arch/arm/cpu/armv7/start.o (.text)

*(.text*)

} > .sram

. = ALIGN(4);

.rodata : { *(SORT_BY_ALIGNMENT(.rodata*)) } >.sram

. = ALIGN(4);

.data : { *(SORT_BY_ALIGNMENT(.data*)) } >.sram

. = ALIGN(4);

.u_boot_list : {

KEEP(*(SORT(.u_boot_list*)));

} > .sram

. = ALIGN(4);

__image_copy_end = .;

_end = .;

.bss :

{

. = ALIGN(4);

__bss_start = .;

*(.bss*)

. = ALIGN(4);

__bss_end = .;

} > .sdram

}

ENTRY(_start)表示入口函数,即uboot上电启动的位置。

arch/arm/cpu/armv7/start.o (.text):表示文本段被调用的文件

路径:u-boot-2018/arch/arm/cpu/armv7/start.S

/* SPDX-License-Identifier: GPL-2.0+ */

/*

* armboot - Startup Code for OMAP3530/ARM Cortex CPU-core

*

* Copyright (c) 2004 Texas Instruments

*

* Copyright (c) 2001 Marius Gr枚ger

* Copyright (c) 2002 Alex Z眉pke

* Copyright (c) 2002 Gary Jennejohn

* Copyright (c) 2003 Richard Woodruff

* Copyright (c) 2003 Kshitij

* Copyright (c) 2006-2008 Syed Mohammed Khasim

*/

#include

#include

#include

#include

#include

/*************************************************************************

*

* Startup Code (reset vector)

*

* Do important init only if we don't start from memory!

* Setup memory and board specific bits prior to relocation.

* Relocate armboot to ram. Setup stack.

*

*************************************************************************/

.globl reset

.globl save_boot_params_ret

.type save_boot_params_ret,%function

#ifdef CONFIG_ARMV7_LPAE

.global switch_to_hypervisor_ret

#endif

reset:

/* Allow the board to save important registers */

b save_boot_params

save_boot_params_ret:

#ifdef CONFIG_ARMV7_LPAE

/*

* check for Hypervisor support

*/

mrc p15, 0, r0, c0, c1, 1 @ read ID_PFR1

and r0, r0, #CPUID_ARM_VIRT_MASK @ mask virtualization bits

cmp r0, #(1 << CPUID_ARM_VIRT_SHIFT)

beq switch_to_hypervisor

switch_to_hypervisor_ret:

#endif

/*

* disable interrupts (FIQ and IRQ), also set the cpu to SVC32 mode,

* except if in HYP mode already

*/

mrs r0, cpsr

and r1, r0, #0x1f @ mask mode bits

teq r1, #0x1a @ test for HYP mode

bicne r0, r0, #0x1f @ clear all mode bits

orrne r0, r0, #0x13 @ set SVC mode

orr r0, r0, #0xc0 @ disable FIQ and IRQ

msr cpsr,r0

/*

* Setup vector:

* (OMAP4 spl TEXT_BASE is not 32 byte aligned.

* Continue to use ROM code vector only in OMAP4 spl)

*/

#if !(defined(CONFIG_OMAP44XX) && defined(CONFIG_SPL_BUILD))

/* Set V=0 in CP15 SCTLR register - for VBAR to point to vector */

mrc p15, 0, r0, c1, c0, 0 @ Read CP15 SCTLR Register

bic r0, #CR_V @ V = 0

mcr p15, 0, r0, c1, c0, 0 @ Write CP15 SCTLR Register

#ifdef CONFIG_HAS_VBAR

/* Set vector address in CP15 VBAR register */

ldr r0, =_start

mcr p15, 0, r0, c12, c0, 0 @Set VBAR

#endif

#endif

/* the mask ROM code should have PLL and others stable */

#ifndef CONFIG_SKIP_LOWLEVEL_INIT

#ifdef CONFIG_CPU_V7A

bl cpu_init_cp15

#endif

#ifndef CONFIG_SKIP_LOWLEVEL_INIT_ONLY

bl cpu_init_crit

#endif

#endif

bl _main

/*------------------------------------------------------------------------------*/

ENTRY(c_runtime_cpu_setup)

/*

* If I-cache is enabled invalidate it

*/

#if !CONFIG_IS_ENABLED(SYS_ICACHE_OFF)

mcr p15, 0, r0, c7, c5, 0 @ invalidate icache

mcr p15, 0, r0, c7, c10, 4 @ DSB

mcr p15, 0, r0, c7, c5, 4 @ ISB

#endif

bx lr

ENDPROC(c_runtime_cpu_setup)

/*************************************************************************

*

* void save_boot_params(u32 r0, u32 r1, u32 r2, u32 r3)

* __attribute__((weak));

*

* Stack pointer is not yet initialized at this moment

* Don't save anything to stack even if compiled with -O0

*

*************************************************************************/

ENTRY(save_boot_params)

b save_boot_params_ret @ back to my caller

ENDPROC(save_boot_params)

.weak save_boot_params

#ifdef CONFIG_ARMV7_LPAE

ENTRY(switch_to_hypervisor)

b switch_to_hypervisor_ret

ENDPROC(switch_to_hypervisor)

.weak switch_to_hypervisor

#endif

/*************************************************************************

*

* cpu_init_cp15

*

* Setup CP15 registers (cache, MMU, TLBs). The I-cache is turned on unless

* CONFIG_SYS_ICACHE_OFF is defined.

*

*************************************************************************/

ENTRY(cpu_init_cp15)

/*

* Invalidate L1 I/D

*/

mov r0, #0 @ set up for MCR

mcr p15, 0, r0, c8, c7, 0 @ invalidate TLBs

mcr p15, 0, r0, c7, c5, 0 @ invalidate icache

mcr p15, 0, r0, c7, c5, 6 @ invalidate BP array

mcr p15, 0, r0, c7, c10, 4 @ DSB

mcr p15, 0, r0, c7, c5, 4 @ ISB

/*

* disable MMU stuff and caches

*/

mrc p15, 0, r0, c1, c0, 0

bic r0, r0, #0x00002000 @ clear bits 13 (--V-)

bic r0, r0, #0x00000007 @ clear bits 2:0 (-CAM)

orr r0, r0, #0x00000002 @ set bit 1 (--A-) Align

orr r0, r0, #0x00000800 @ set bit 11 (Z---) BTB

#if CONFIG_IS_ENABLED(SYS_ICACHE_OFF)

bic r0, r0, #0x00001000 @ clear bit 12 (I) I-cache

#else

orr r0, r0, #0x00001000 @ set bit 12 (I) I-cache

#endif

mcr p15, 0, r0, c1, c0, 0

#ifdef SUNXI_ARM_A53

/*

*clear AFE,TRE bit in sctrl

*non-secure: reset value is unknow

*secure : default value is 0

*notice : we must set the TRE bit to enable the memory

* arttribute configuration from the section table.

*/

MRC p15, 0, r0, c1, c0, 0 @Read SCTLR

BIC r0, r0, #(1<<28) @clr TRE bit

BIC r0, r0, #(1<<29) @clr AEF bit

MCR p15, 0, r0, c1, c0, 0 @Write SCTLR

#endif

#ifdef CONFIG_ARM_ERRATA_716044

mrc p15, 0, r0, c1, c0, 0 @ read system control register

orr r0, r0, #1 << 11 @ set bit #11

mcr p15, 0, r0, c1, c0, 0 @ write system control register

#endif

#if (defined(CONFIG_ARM_ERRATA_742230) || defined(CONFIG_ARM_ERRATA_794072))

mrc p15, 0, r0, c15, c0, 1 @ read diagnostic register

orr r0, r0, #1 << 4 @ set bit #4

mcr p15, 0, r0, c15, c0, 1 @ write diagnostic register

#endif

#ifdef CONFIG_ARM_ERRATA_743622

mrc p15, 0, r0, c15, c0, 1 @ read diagnostic register

orr r0, r0, #1 << 6 @ set bit #6

mcr p15, 0, r0, c15, c0, 1 @ write diagnostic register

#endif

#ifdef CONFIG_ARM_ERRATA_751472

mrc p15, 0, r0, c15, c0, 1 @ read diagnostic register

orr r0, r0, #1 << 11 @ set bit #11

mcr p15, 0, r0, c15, c0, 1 @ write diagnostic register

#endif

#ifdef CONFIG_ARM_ERRATA_761320

mrc p15, 0, r0, c15, c0, 1 @ read diagnostic register

orr r0, r0, #1 << 21 @ set bit #21

mcr p15, 0, r0, c15, c0, 1 @ write diagnostic register

#endif

#ifdef CONFIG_ARM_ERRATA_845369

mrc p15, 0, r0, c15, c0, 1 @ read diagnostic register

orr r0, r0, #1 << 22 @ set bit #22

mcr p15, 0, r0, c15, c0, 1 @ write diagnostic register

#endif

mov r5, lr @ Store my Caller

mrc p15, 0, r1, c0, c0, 0 @ r1 has Read Main ID Register (MIDR)

mov r3, r1, lsr #20 @ get variant field

and r3, r3, #0xf @ r3 has CPU variant

and r4, r1, #0xf @ r4 has CPU revision

mov r2, r3, lsl #4 @ shift variant field for combined value

orr r2, r4, r2 @ r2 has combined CPU variant + revision

#ifdef CONFIG_ARM_ERRATA_798870

cmp r2, #0x30 @ Applies to lower than R3p0

bge skip_errata_798870 @ skip if not affected rev

cmp r2, #0x20 @ Applies to including and above R2p0

blt skip_errata_798870 @ skip if not affected rev

mrc p15, 1, r0, c15, c0, 0 @ read l2 aux ctrl reg

orr r0, r0, #1 << 7 @ Enable hazard-detect timeout

push {r1-r5} @ Save the cpu info registers

bl v7_arch_cp15_set_l2aux_ctrl

isb @ Recommended ISB after l2actlr update

pop {r1-r5} @ Restore the cpu info - fall through

skip_errata_798870:

#endif

#ifdef CONFIG_ARM_ERRATA_801819

cmp r2, #0x24 @ Applies to lt including R2p4

bgt skip_errata_801819 @ skip if not affected rev

cmp r2, #0x20 @ Applies to including and above R2p0

blt skip_errata_801819 @ skip if not affected rev

mrc p15, 0, r0, c0, c0, 6 @ pick up REVIDR reg

and r0, r0, #1 << 3 @ check REVIDR[3]

cmp r0, #1 << 3

beq skip_errata_801819 @ skip erratum if REVIDR[3] is set

mrc p15, 0, r0, c1, c0, 1 @ read auxilary control register

orr r0, r0, #3 << 27 @ Disables streaming. All write-allocate

@ lines allocate in the L1 or L2 cache.

orr r0, r0, #3 << 25 @ Disables streaming. All write-allocate

@ lines allocate in the L1 cache.

push {r1-r5} @ Save the cpu info registers

bl v7_arch_cp15_set_acr

pop {r1-r5} @ Restore the cpu info - fall through

skip_errata_801819:

#endif

#ifdef CONFIG_ARM_CORTEX_A15_CVE_2017_5715

mrc p15, 0, r0, c1, c0, 1 @ read auxilary control register

orr r0, r0, #1 << 0 @ Enable invalidates of BTB

push {r1-r5} @ Save the cpu info registers

bl v7_arch_cp15_set_acr

pop {r1-r5} @ Restore the cpu info - fall through

#endif

#ifdef CONFIG_ARM_ERRATA_454179

mrc p15, 0, r0, c1, c0, 1 @ Read ACR

cmp r2, #0x21 @ Only on < r2p1

orrlt r0, r0, #(0x3 << 6) @ Set DBSM(BIT7) and IBE(BIT6) bits

push {r1-r5} @ Save the cpu info registers

bl v7_arch_cp15_set_acr

pop {r1-r5} @ Restore the cpu info - fall through

#endif

#if defined(CONFIG_ARM_ERRATA_430973) || defined (CONFIG_ARM_CORTEX_A8_CVE_2017_5715)

mrc p15, 0, r0, c1, c0, 1 @ Read ACR

#ifdef CONFIG_ARM_CORTEX_A8_CVE_2017_5715

orr r0, r0, #(0x1 << 6) @ Set IBE bit always to enable OS WA

#else

cmp r2, #0x21 @ Only on < r2p1

orrlt r0, r0, #(0x1 << 6) @ Set IBE bit

#endif

push {r1-r5} @ Save the cpu info registers

bl v7_arch_cp15_set_acr

pop {r1-r5} @ Restore the cpu info - fall through

#endif

#ifdef CONFIG_ARM_ERRATA_621766

mrc p15, 0, r0, c1, c0, 1 @ Read ACR

cmp r2, #0x21 @ Only on < r2p1

orrlt r0, r0, #(0x1 << 5) @ Set L1NEON bit

push {r1-r5} @ Save the cpu info registers

bl v7_arch_cp15_set_acr

pop {r1-r5} @ Restore the cpu info - fall through

#endif

#ifdef CONFIG_ARM_ERRATA_725233

mrc p15, 1, r0, c9, c0, 2 @ Read L2ACR

cmp r2, #0x21 @ Only on < r2p1 (Cortex A8)

orrlt r0, r0, #(0x1 << 27) @ L2 PLD data forwarding disable

push {r1-r5} @ Save the cpu info registers

bl v7_arch_cp15_set_l2aux_ctrl

pop {r1-r5} @ Restore the cpu info - fall through

#endif

#ifdef CONFIG_ARM_ERRATA_852421

mrc p15, 0, r0, c15, c0, 1 @ read diagnostic register

orr r0, r0, #1 << 24 @ set bit #24

mcr p15, 0, r0, c15, c0, 1 @ write diagnostic register

#endif

#ifdef CONFIG_ARM_ERRATA_852423

mrc p15, 0, r0, c15, c0, 1 @ read diagnostic register

orr r0, r0, #1 << 12 @ set bit #12

mcr p15, 0, r0, c15, c0, 1 @ write diagnostic register

#endif

mov pc, r5 @ back to my caller

ENDPROC(cpu_init_cp15)

#if !defined(CONFIG_SKIP_LOWLEVEL_INIT) && \

!defined(CONFIG_SKIP_LOWLEVEL_INIT_ONLY)

/*************************************************************************

*

* CPU_init_critical registers

*

* setup important registers

* setup memory timing

*

*************************************************************************/

ENTRY(cpu_init_crit)

/*

* Jump to board specific initialization...

* The Mask ROM will have already initialized

* basic memory. Go here to bump up clock rate and handle

* wake up conditions.

*/

b lowlevel_init @ go setup pll,mux,memory

ENDPROC(cpu_init_crit)

#endif

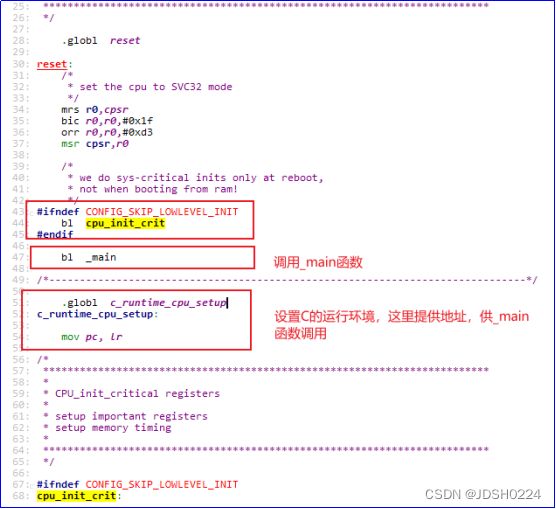

reset:是第一个被执行的汇编位置。

bl _main:跳转到main函数,文件位置:u-boot-2018/arch/arm/lib/crt0.S

路径:u-boot-2018/arch/arm/lib/crt0.S

/* SPDX-License-Identifier: GPL-2.0+ */

/*

* crt0 - C-runtime startup Code for ARM U-Boot

*

* Copyright (c) 2012 Albert ARIBAUD

*/

#include

#include

#include

#ifdef CONFIG_CPU_V7M

#include

#endif

/*

* This file handles the target-independent stages of the U-Boot

* start-up where a C runtime environment is needed. Its entry point

* is _main and is branched into from the target's start.S file.

*

* _main execution sequence is:

*

* 1. Set up initial environment for calling board_init_f().

* This environment only provides a stack and a place to store

* the GD ('global data') structure, both located in some readily

* available RAM (SRAM, locked cache...). In this context, VARIABLE

* global data, initialized or not (BSS), are UNAVAILABLE; only

* CONSTANT initialized data are available. GD should be zeroed

* before board_init_f() is called.

*

* 2. Call board_init_f(). This function prepares the hardware for

* execution from system RAM (DRAM, DDR...) As system RAM may not

* be available yet, , board_init_f() must use the current GD to

* store any data which must be passed on to later stages. These

* data include the relocation destination, the future stack, and

* the future GD location.

*

* 3. Set up intermediate environment where the stack and GD are the

* ones allocated by board_init_f() in system RAM, but BSS and

* initialized non-const data are still not available.

*

* 4a.For U-Boot proper (not SPL), call relocate_code(). This function

* relocates U-Boot from its current location into the relocation

* destination computed by board_init_f().

*

* 4b.For SPL, board_init_f() just returns (to crt0). There is no

* code relocation in SPL.

*

* 5. Set up final environment for calling board_init_r(). This

* environment has BSS (initialized to 0), initialized non-const

* data (initialized to their intended value), and stack in system

* RAM (for SPL moving the stack and GD into RAM is optional - see

* CONFIG_SPL_STACK_R). GD has retained values set by board_init_f().

*

* 6. For U-Boot proper (not SPL), some CPUs have some work left to do

* at this point regarding memory, so call c_runtime_cpu_setup.

*

* 7. Branch to board_init_r().

*

* For more information see 'Board Initialisation Flow in README.

*/

/*

* entry point of crt0 sequence

*/

ENTRY(_main)

/*

* Set up initial C runtime environment and call board_init_f(0).

*/

#if defined(CONFIG_SPL_BUILD) && defined(CONFIG_SPL_STACK)

ldr r0, =(CONFIG_SPL_STACK)

#else

ldr r0, =(CONFIG_SYS_INIT_SP_ADDR)

#endif

bic r0, r0, #7 /* 8-byte alignment for ABI compliance */

mov sp, r0

bl board_init_f_alloc_reserve

mov sp, r0

/* set up gd here, outside any C code */

mov r9, r0

bl board_init_f_init_reserve

mov r0, #0

bl board_init_f

#if ! defined(CONFIG_SPL_BUILD)

/*

* Set up intermediate environment (new sp and gd) and call

* relocate_code(addr_moni). Trick here is that we'll return

* 'here' but relocated.

*/

ldr r0, [r9, #GD_START_ADDR_SP] /* sp = gd->start_addr_sp */

bic r0, r0, #7 /* 8-byte alignment for ABI compliance */

mov sp, r0

ldr r9, [r9, #GD_BD] /* r9 = gd->bd */

sub r9, r9, #GD_SIZE /* new GD is below bd */

adr lr, here

ldr r0, [r9, #GD_RELOC_OFF] /* r0 = gd->reloc_off */

add lr, lr, r0

#if defined(CONFIG_CPU_V7M)

orr lr, #1 /* As required by Thumb-only */

#endif

ldr r0, [r9, #GD_RELOCADDR] /* r0 = gd->relocaddr */

b relocate_code

here:

/*

* now relocate vectors

*/

bl relocate_vectors

/* Set up final (full) environment */

bl c_runtime_cpu_setup /* we still call old routine here */

#endif

#if !defined(CONFIG_SPL_BUILD) || defined(CONFIG_SPL_FRAMEWORK)

# ifdef CONFIG_SPL_BUILD

/* Use a DRAM stack for the rest of SPL, if requested */

bl spl_relocate_stack_gd

cmp r0, #0

movne sp, r0

movne r9, r0

# endif

ldr r0, =__bss_start /* this is auto-relocated! */

#ifdef CONFIG_USE_ARCH_MEMSET

ldr r3, =__bss_end /* this is auto-relocated! */

mov r1, #0x00000000 /* prepare zero to clear BSS */

subs r2, r3, r0 /* r2 = memset len */

bl memset

#else

ldr r1, =__bss_end /* this is auto-relocated! */

mov r2, #0x00000000 /* prepare zero to clear BSS */

clbss_l:cmp r0, r1 /* while not at end of BSS */

#if defined(CONFIG_CPU_V7M)

itt lo

#endif

strlo r2, [r0] /* clear 32-bit BSS word */

addlo r0, r0, #4 /* move to next */

blo clbss_l

#endif

#if ! defined(CONFIG_SPL_BUILD)

bl coloured_LED_init

bl red_led_on

#endif

/* call board_init_r(gd_t *id, ulong dest_addr) */

mov r0, r9 /* gd_t */

ldr r1, [r9, #GD_RELOCADDR] /* dest_addr */

/* call board_init_r */

#if CONFIG_IS_ENABLED(SYS_THUMB_BUILD)

ldr lr, =board_init_r /* this is auto-relocated! */

bx lr

#else

ldr pc, =board_init_r /* this is auto-relocated! */

#endif

/* we should not return here. */

#endif

ENDPROC(_main)

ENTRY(_main):入口函数

board_init_f:与平台相关的函数,路径:u-boot-2014.07\common\board_f.c

board_init_r:

路径:u-boot-2014.07\common\board_f.c

workmode = 16,storage type = 0 //u-boot-2014.07\drivers\sunxi_flash\sunxi_flash.c sunxi_flash_handle_init 函数

[ 12.759]NAND_UbootProbe start

[ 12.762]NB1 : enter phy init

[ 12.765]nand_physic_init

[ 12.773]Reset NDFC start 0 0

[ 12.773]Reset NDFC end 0 0路径:u-boot-2014.07\common\board_r.c

U_BOOT_CMD(烧写函数)

位置:include/configs/sun8iw10p1.h:283:

函数:SUNXI_SPRITE_ENV环境变量

CONFIG_SUNXI_SPRITE_ENV_SETTINGS="bootdelay=0\0bootcmd=run sunxi_sprite_test\0console=ttyS0,115200\0sunxi_sprite_test=sprite_test read\0"

U_BOOT_CMD(

sprite_test, 2, 0, do_sprite_test,

"do a sprite test",

"NULL"

);以上的sprite_test函数被调用流程

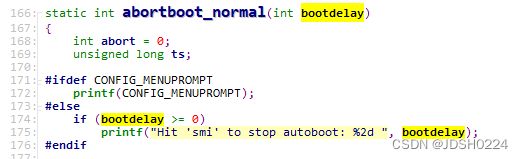

步骤1:boot启动延时函数

位置:u-boot-2014.07\common\autoboot.c

函数:bootdelay_process(void)

s = getenv("bootcmd"); //其中的bootcmd是上面CONFIG_SUNXI_SPRITE_ENV_SETTINGS配置

步骤2:自动启动传递的命令参数

位置:u-boot-2014.07\common\main.c

函数:autoboot_command(s); //上面的参数s传给当前函数

步骤2:运行命令

位置:u-boot-2014.07\common\autoboot.c

函数:run_command_list(s, -1, 0); //上面的参数s传给当前函数,即sprite_test

特别注意,上面的“bootdelay=0”,所以以下函数不会执行内核验签,即在烧写镜像环境不会执行的

Uboot用户自定义程序(未找到被调用的位置)

U_BOOT_CMD(

go, CONFIG_SYS_MAXARGS, 1, do_go,

"start application at address 'addr'",

"addr [arg ...]\n - start application at address 'addr'\n"

" passing 'arg' as arguments"

);SUNXI_USB

结构体申明

typedef struct sunxi_usb_setup_req_s

{

int (* state_init )(void);

int (* state_exit )(void);

void (* state_reset )(void);

int (* standard_req_op )(uint cmd, struct usb_device_request *req, uchar *buffer);

int (* nonstandard_req_op)(uint cmd, struct usb_device_request *req, uchar *buffer, uint data_status);

int (* state_loop )(void *sunxi_udc);

void (* dma_rx_isr )(void *p_arg);

void (* dma_tx_isr )(void *p_arg);

}

sunxi_usb_setup_req_t;结构体定义

路径:u-boot-2014.07\usb_sunxi\usb_efex.c

定义一个usb模块,初始化相关的函数指针

sunxi_usb_module_init(SUNXI_USB_DEVICE_EFEX, \

sunxi_efex_init, \

sunxi_efex_exit, \

sunxi_efex_reset, \

sunxi_efex_standard_req_op, \

sunxi_efex_nonstandard_req_op, \

sunxi_efex_state_loop, \

sunxi_efex_usb_rx_dma_isr, \

sunxi_efex_usb_tx_dma_isr \

);sunxi_usb_module_init

#define sunxi_usb_module_init(name, state_init, state_exit, state_reset, standard_req_op, nonstandard_req_op, state_loop, dma_rx_isr, dma_tx_isr) \

__sunxi_usb_module_init(name, state_init, state_exit, state_reset, standard_req_op, nonstandard_req_op, state_loop, dma_rx_isr, dma_tx_isr)

__sunxi_usb_module_init

#define __sunxi_usb_module_init(name, state_init, state_exit, state_reset, standard_req_op, nonstandard_req_op, state_loop, dma_rx_isr, dma_tx_isr) \

sunxi_usb_setup_req_t setup_req_##name = {state_init, state_exit, state_reset, standard_req_op, nonstandard_req_op, state_loop, dma_rx_isr, dma_tx_isr };

说明:setup_req_##name:即为定义的结构体名称

__sunxi_usb_module_reg

#define __sunxi_usb_module_reg(name) \

sunxi_udev_active = &setup_req_##name

说明:

1.模块注册,即绑定__sunxi_usb_module_init内初始化的结构体

2.sunxi_udev_active即为全局的USB操作结构体对象

sunxi_usb_module_reg(name)

#define sunxi_usb_module_reg(name) \

__sunxi_usb_module_reg(name)

dram_data_recv_finish

要剖析这个函数以及unxi_usb_module_init(SUNXI_USB_DEVICE_EFEX的结构体中函数的使用,在烧写的时候抓USB包分析。

Uboot中添加环境变量

setenv("partitions", partition_sets);