DDR 内存与 PCB 设计挑战

手机、笔记本电脑、云计算等对电子性能要求越来越高。除了处理器速度/性能外,内存在整体系统性能中也起着非常关键的作用。双倍数据速率(DDR)内存已成为主要选择,它具有低时延,大存储容量和低功耗。

内存简介

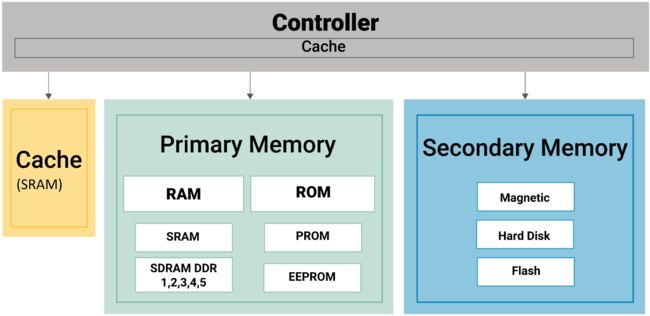

存储器是电子产品中的数据存储设备,主要用来存储数据处理过程中的数据。

主存储器进一步分为随机存取存储器 (RAM) 和只读存储器 (ROM)。RAM 是易失性存储器,断电后数据会丢失,而ROM 存储器即使在断电后仍保留数据。随着超大规模集成电路技术的进步,存储器结构、存储器芯片密度、尺寸、速度和通信接口都得到了很大程度的改进。

SRAM和SDRAM的区别

RAM进一步分为SRAM和SDRAM。SRAM 是静态 RAM,SDRAM 是同步动态 RAM。两者之间的架构差异在于DRAM 每个内存位使用 1 个晶体管和 1 个电容器,而 SRAM 使用 1 个触发器(每个触发器约 6 个晶体管)来形成一位。与 SRAM 相比,访问时间更长、速度稍慢。由于电容/晶体管的尺寸比触发器更小,与 SRAM 相比,SDRAM 的存储密度更高。SDRAM 是动态存储,因为电容器会随着时间的推移而放电,需要定期刷新,否则 SDRAM 存储的数据会丢失。

SRAM 一直是高速缓存的主要选择,因为它们速度极快且访问时间极短。它们内置在处理器内部,cache充当外部RAM和处理器之间的缓存。简而言之,cache大大缩减了处理器访问memory数据的平均时间。

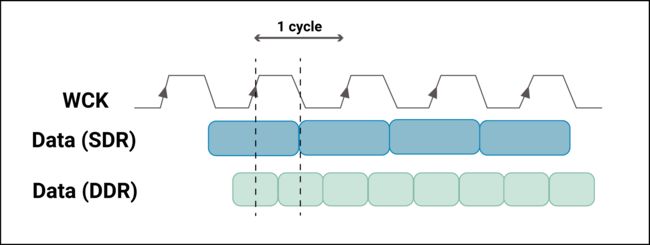

SDRAM 代表同步动态 RAM, I/O、内部时钟和总线时钟是同步的,例如PC133 I/O、内部时钟和总线时钟都是133MHz。Single Data Rate 表示 SDR SDRAM 每个时钟周期可以读/写一次。SDR SDRAM 需要等待上一个命令完成才能进行下一个读/写操作。

DDR RAM 有哪些不同类型?

随着对高数据速率和更大数据密度的需求提升,SDR 逐渐演变为 DDR 概念。在 DDR SDRAM 中,数据在上升沿、下降沿均有效,可将数据传输速率加倍。通过这种方式,DDR 比 SDR SDRAM 实现了更大的带宽,在不增加时钟频率的情况下将传输速率加倍。

在过去的几十年里,DDR 已经发生了许多改进。DDR 在市场上非常流行,广泛用于笔记本电脑、台式电脑、服务器和嵌入式计算系统,大大提高了操作速度、存储密度、降低了功耗,并增加了错误检测(例如 CRC)、通过位反转降低 SSN 噪声。下面,我们将介绍 DDR 存储器的演变及其优势。

第一代 – DDR SDRAM

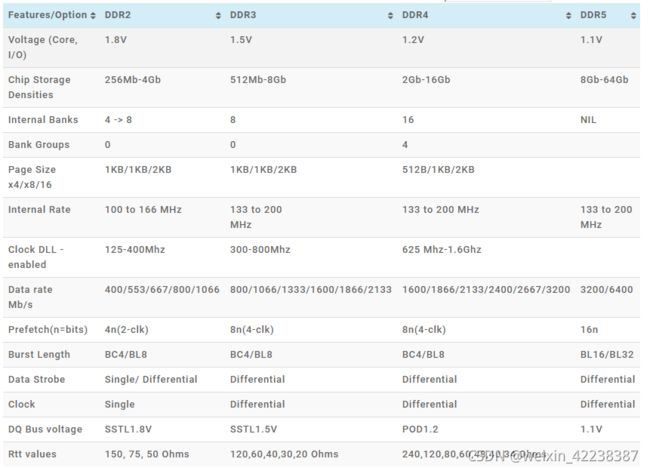

第一代DDR内存有一个2位的预取缓冲区,是SDR SDRAM的两倍。133 ~ 200MHz 的内部时钟速度使 DDR1 的传输速率为 266 到 400 MT/s(Million Transfer Per Second)。DDR1 IC于1998年投放市场。

第二代 – DDR2 SDRAM

DDR2 运行的速度是 DDR1 SDRAM 的两倍,通过改进的总线信号实现。DDR2 的预取为 4 位,是 DDR SDRAM 的两倍,与 DDR 内存具有相同的内部时钟速度(133 ~ 200 MHz),但DDR2 内存提高了传输速率(533 ~ 800 MT/s)和 I/O 总线信号。DDR2-533 和 DDR2-800 内存于 2003 年投放市场。

第三代 – DDR3 SDRAM

DDR3 的运行速度是 DDR2 的两倍,通过进一步改进总线信号来实现。DDR3 的预取为 8 位,是 DDR2 的两倍,传输速率为 800 ~ 1600 MT/s,与 DDR2 VDD 1.8V 相比,DDR3 VDD1.5V 的低电压,可以降低 40% 的功耗。DDR3 还有两个附加功能ASR(自动自刷新)和 SRT(自刷新温度)。DDR3 IC于2007年上市。

第四代 – DDR4 SDRAM

DDR4 的运行速度是 DDR3 的两倍,工作电压为1.2V,传输速率为2133~3200MT/s。DDR4 增加了4个bank组技术,每个bank组都可以单独操作。DDR4 在一个时钟周期内可以处理 4 个数据,因此 DDR4 的效率优于 DDR3。DDR4 还有一些附加功能,例如 DBI(数据总线反转)、数据总线上的 CRC(循环冗余校验)和命令/地址奇偶校验,这些功能可以增强DDR4内存的信号完整性,提高数据传输/访问的稳定性。DDR4 IC于2014年上市。

第五代 – DDR5 SDRAM

DDR5 的运行速度是 DDR4 的两倍。DDR5 的传输速率为 3200 ~ 6400 MT/s。DDR5 规范于 2018 年 11 月发布,IC 预计到 2022 年上市。

DDR5 VS DDR4

我们现在将讨论 DDR5 与 DDR4 之间最显着的变化

速度改进:

- 改进的时钟速度(1.6GHz 至 3.2GHz)

- 提高数据速度(3.2Gbps 至 6.4 Gbps)

- 新功能,例如决策反馈均衡 (DFE)

低电压等级:

工作电压VDD从1.2V变为1.1V,降低了功耗,另一方面,较低的 VDD 意味着较小的抗噪余量。

DDR5电源架构介绍:

电源管理从主板转移到 DIMM 本身,DDR5 DIMM 具有 12V 电源管理 IC,可实现更好的IC电源管理,并有助于解决信号完整性和噪声问题。

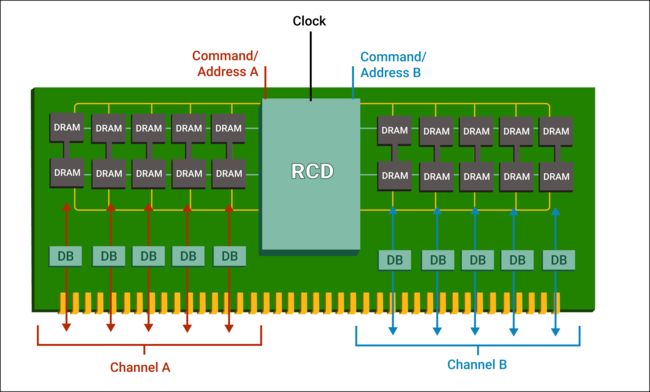

DDR5 通道架构的改进:

DDR4 DIMM 具有 72 位总线,包括 64 个数据位和 8 个 ECC 位(纠错码)。在 DDR5 中,每个 DIMM 有两个 40 位通道(32 个数据位和 8 个 ECC 位)。虽然数据宽度相同(总共 64 位),但具有两个较小的独立通道可提高内存访问效率,这样做的好处是更高的 MT/s 。

在 DDR4 中,RCD寄存时钟驱动器 ( RCD) 每侧提供两个输出时钟。DDR5 中的 RCD 每侧提供 4 个输出时钟,为每个通道提供一个独立的时钟,这提高了信号完整性并帮助我们解决由于降低 VDD 而出现的较低噪声容限问题。

突发长度增加至 16:

DDR4 突发长度为 8,而对于 DDR5,突发长度已扩展至 16。16 (BL16) 的突发长度使单个突发能够访问 64 字节的数据。双通道可以显著提升并发及内存效率。

更高DRAM容量:

DDR5 缓冲芯片 DIMM 使系统设计能够在单芯片封装中使用密度高达 64 Gb 的 DRAM,DDR4 在单芯片封装中提供 16 Gb DRAM。

在下表中,我们比较了几代 DDR RAM 的一些关键特性,以便更好地理解。

内存数据传输速度

内存数据传输的速度决定了程序的执行速度,当同时运行多个软件应用程序或图像应用程序时,传输速率的重要性就显而易见了,内存传输速率主要由三个因素决定,例如内存时钟速率、IO BUS时钟和预取位数。

| Names | Memory clock | I/O bus clock | Pre-fetch n = data bits |

Data Transfer rate = 2 * I/O clock | Theoretical bandwidth = data Trnsfr * 8 Byte |

|---|---|---|---|---|---|

| DDR1-200, PC-1600 | 100 MHz | 100 MHz | 2n | 200 MT/s | 1.6 GB/s |

| DDR1-400, PC-3200 | 200 MHz | 200 MHz | 2n | 400 MT/s | 3.2 GB/s |

| DDR2-800, PC2-6400 | 200 MHz | 400 MHz | 4n | 800 MT/s | 6.4 GB/s |

| DDR3-1600, PC3-12800 | 200 MHz | 800 MHz | 8n | 1600 MT/s | 12.8 GB/s |

| DDR4-2400, PC4-19200 | 300 MHz | 1200 MHz | 8n | 2400 MT/s | 19.2 GB/s |

| DDR4-3200, PC4-25600 | 400 MHz | 1600 MHz | 8n | 3200 MT/s | 25.6 GB/s |

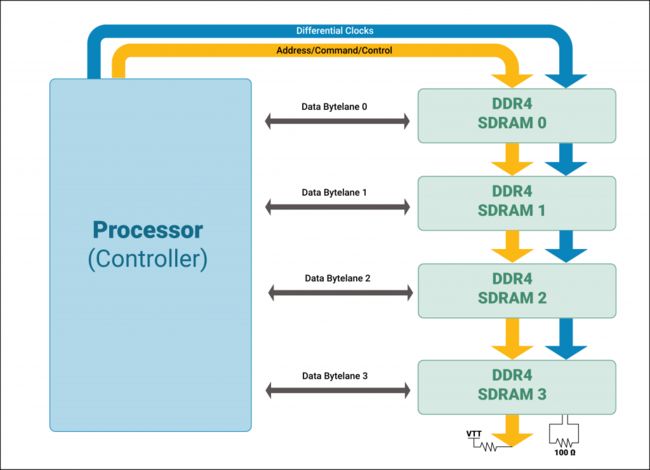

DDR4工作方式

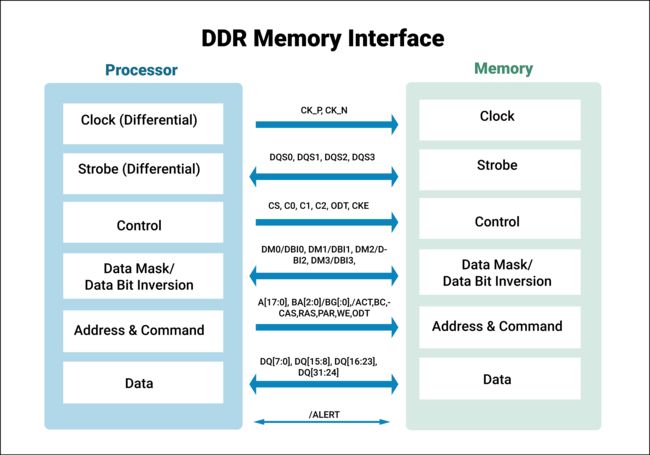

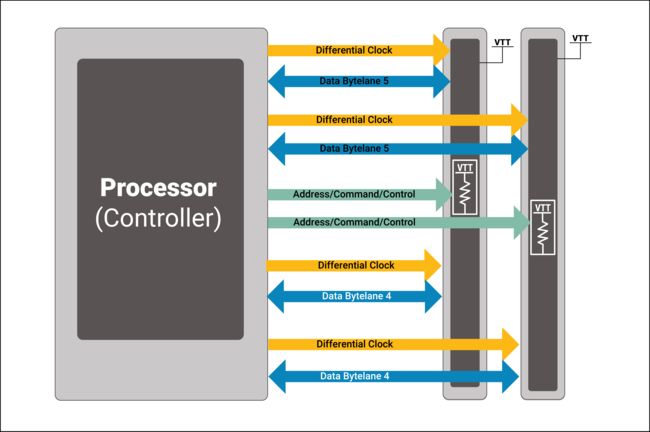

DDR4标准的内存和处理器接口如下图所示,该接口由各种信号组成,包括数据、地址、时钟和控制信号。

接口信号

下表列出了处理器和 SDRAM 存储器之间数据传输中使用的一些基本和重要信号。

| Symbol | Type | Function |

|---|---|---|

| CS_n (Differential) |

Input | Chip select is active low signal, this signal enables the memory IC for read/write operation |

| CKE | Input | Clock Enable. HIGH enables the internal clock signals device input buffers and output drivers. |

| CK_t/CK_c | Input | Clock is a differential signal. All address and control signals are sampled at the crossing of posedge and negedge of clock. |

| DQ(single)/ DQS_t/DQS_c (Differential) | In/out | Data Bus is single-ended signal whereas Data Strobe is differential signals. Data is read or written in memory with respect to strobe signal. It acts as data valid flag. |

| RAS_n/A16; CAS_n/A15; WE_n/A14 |

Input |

These are dual function inputs. When ACT_n and CS_n signals are LOW, these are interpreted as Row Address Bits. When ACT_n is HIGH, these are interpreted as command pins to indicate READ, WRITE or other commands. |

| ACT_n | Input | Activate command input, when this signal is low data on RAS/CAS/WE acts as a command |

| BG0-1 BA0-1 |

Input | Bank Group, Bank Address |

| DBI[0-n] | In/out | Data bit inversion |

| A0-16 | Input | Address inputs |

数据总线

DDR 存储器具有数据总线宽度,例如 DQ [0:3]、DQ [0:7] 和 DQ [8:15]。DIMM最大数据总线宽度为 32 位或 64 位,具体取决于处理器。在 DDR4 中,额外分配了 8 位用于错误控制(ECC),因此总线宽度变为 40 位/72 位。

数据总线反转 (DBI) 功能:

DDR4 使用数据总线反转以减轻噪声,因此可以观察到电源噪声改善和 IO 功率间歇性降低。DBI# 是一个低电平有效的双向信号,在写操作期间,如果 DBI# 采样为低电平,则 DRAM 会反转在 DQ 输入上接收到的写数据,如果 DBI# 为高电平,则 DRAM 将在 DQ 输入上接收到的数据保持非反相,在读取操作期间,其 DQ 输出上的读取数据由 DRAM 反转。当给定字节“0”数据位的数量大于 4 时,DBI# 引脚被驱动为低电平,否则读取的数据不会被 DRAM 反转并将 DBI# 引脚驱动为高电平。

Write leveling

在 DDR4 中,存储器以Fly-by拓扑而非拓扑进行布线,这样做是为了减少高速数据传输过程中引起的反射。Fly-By 路径是时钟(和地址)信号从控制器开始,并建立到所有 DRAM 的通道。然而,这会在 DRAM 的时钟到 DQS 方面产生问题,最靠近控制器的 DRAM 将在最后一个 DRAM 之前接收时钟和地址信号。

内存中地址/时钟路径的长度和信号不匹配会在读取周期中产生问题,因此在 DDR4 中实施了“写入均衡”解决方案,这些解决方案使控制器能够自动检测不同 DRAM 的时钟信号之间的时间差异,适当延迟数据通道,以便它们在时钟/地址信号到达 DRAM 时到达 DRAM。这种检测所需延迟的过程称为“训练”,还可以根据其选通延迟通道内的每个 DQ 位,以将选通完美地集中在 DQ 信号周围。

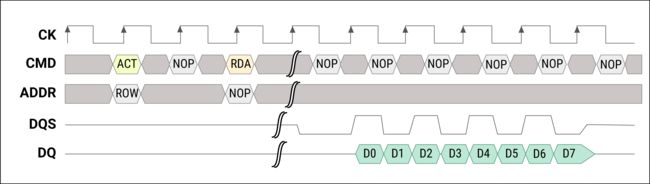

突发长度为 8 (BL8) 的 READ 操作

- 处理器发送ACT命令,此时地址总线上的值表示行地址。ACT 命令在时钟的第一个位置与行地址一起计时,命令行与地址总线复用。

- 处理器发送 RDA(自动预充电读取),此时地址总线上的值表示列地址,在第三个时钟沿,它被锁存到存储器中。

- 接下来,DQS 信号时钟是存储器的输出,在读取操作期间,两个边缘都与数据对齐。

- 最后,处理器发送 RDA 命令,该命令由 DRAM 解析,以在读取完成后自动对存储体进行预充电。

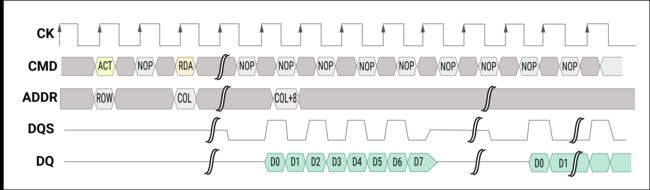

突发长度为 8 (BL8) 的写操作

- 处理器发送ACT命令,此时地址总线上的值表示行地址,ACT 命令在时钟的第一个位置与行地址一起计时。

- 处理器发送 2 个 WRITE 命令,第一个表示 COL 地址,第二个表示 COL+8,在第三个时钟沿,它被锁存到存储器中。

- 第二次写操作不需要ACT命令,这是因为我们打算写入的行已经在 Sense Amp 中处于激活状态。

- 接下来,选通 DQS 信号时钟是写操作期间处理器的输出以及选通信号两个边沿的数据。

- 第一个命令是一个普通的 WR,因此这会使该行保持活动状态,第二个命令是 WRA,它在写入完成后停用该行。

DDR模块

为了在容量和带宽方面增加整体内存大小,多个DRAM组合在单个 PCB 上,称为模组。每个 DIMM 可以有多个芯片,一般为 4-16 个 IC,放置在 PCB 的两侧,组成2GB、4GB、8GB、16GB、32GB 的内存模块。例如,DIMM 的 64 位数据总线至少需要 8 个X8 DRAM。

根据大小,它们具有三种外形,它们是 DIMM(双列直插式内存模块)、SODIMM 和 MICRODIMM。

| Type of DIMM | DDR | Pin count |

|---|---|---|

| DIMM SODIMM MICRODIMM |

DDR1 | 184 200 172 |

| DIMM SODIMM MICRODIMM |

DDR2 | 240 200 214 |

| DIMM SODIMM MICRODIMM |

DDR3 | 240 204 214 |

| DIMM SODIMM MICRODIMM |

DDR4 | 288 260 |

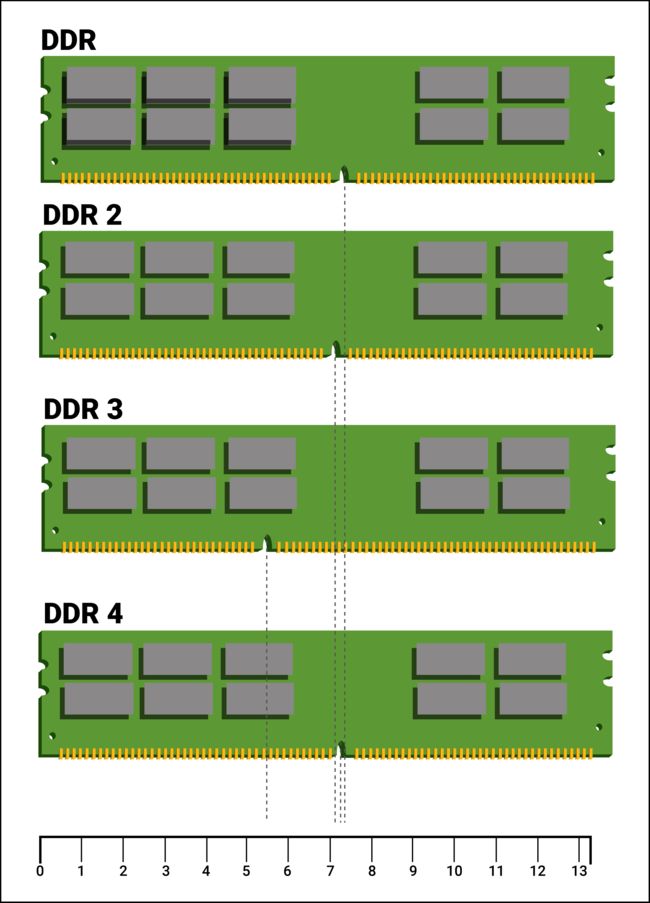

不同DDR 内存都互不兼容。DDR2/3/4 DIMM 只能用于各自的 DDR2/3/4 插槽,槽口位置不同,且电源也有变化:DDR1 DIMM 为 2.5V;DDR2,1.8V;DDR3,1.5V;DDR4,1.2V。

DDR 模块插槽

DDR存储器的应用及选择参数

内存用于以下设备/系统:

- 计算机、笔记本电脑、超级计算机、服务器等。

- 移动设备、平板电脑

- 游戏设备

选择参数:

- 验证处理器内存控制器接口和对 DDR4 接口的支持

- 设计中所需的内存类型

- 内存大小

- 时钟频率要求

- 接口速度

- 时钟和数据总线的上升时间

- 访问时间

- 写周期时间

- 建立和保持时间值命令、地址、控制

- 核心和 IO 电压要求

- VIO/VIH 和 VOL/VOH 信号

- 封装类型

封装:

广泛用于大尺寸存储器的封装有 BGA、FBBGA、WFBGA、TFBGA、QFPN 等。

IC厂商:

Micron Technology、ISSI、Winbond、Cypress、STMicroelectronics、Alliance Memory等

模组厂商:

Cypress, Kingmax, Micron, Electronics, Centon Electronics 等

DDR 存储器 PCB 布线的主要挑战

高速 PCB设计通常需要满足某些时序要求才能正常执行。但是,在 DDR4 的情况下,由于更高的数据速率,对时序的要求更高,为减少误码率/数据损坏,设计人员需要在每一步进行电路模拟以确保信号完整性。

由于在时钟/选通的两个边缘和高时钟速率 1.6GHz 的数据传输,建立和保持时间更短,因此时序延迟起着重要作用。下面讨论实现这些要求的方法。

使用千兆传输 DDR4 SDRAM 接口的主要挑战包括:

- 最大化数据传输时序余量的方法;控制正确的建立/保持时间

- 具有多个接收器的网络的路径拓扑和适当的端接方案

- 最小化串扰的路径技术

- 减轻由于过孔缺陷导致的阻抗不连续性的方法。

- 稳定电源电压

- 走线长度匹配

11 种最佳高速 PCB 布线实践。

DDR存储器PCB设计要求规则

正确的设置时间和保持时间

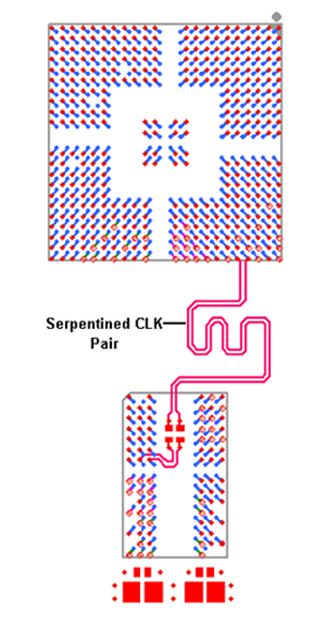

调整时钟相对于数据线和控制信号的走线长度,以符合存储器IC的建立和保持时间,可以通过以蛇形方式路由时钟信号来延迟时钟信号。

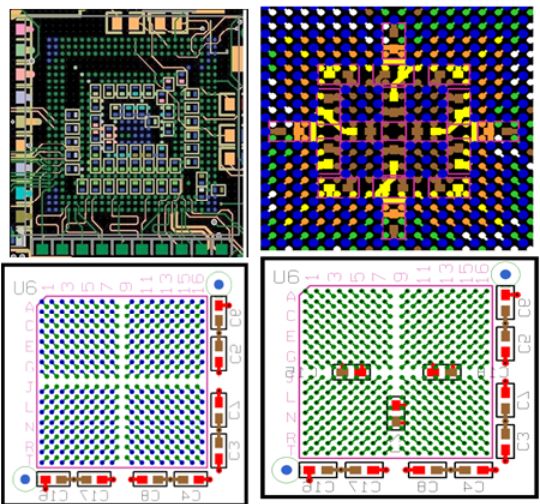

稳定的参考电压

DDR4 需要非常干净和稳定的电压,因为它在低电压 (1.2V) 下运行,电源电压通过电源层传送到存储器和电路板同一侧的端接电阻器,从而消除了由于过孔造成的阻抗,电容器也应均匀放置,以创建一致、干净的旁路参考。下图显示了处理器/FPGA 中电容器的位置。

在处理器/FPGA 中放置电容器

在 DDR 中放置电容器

去电容和旁路电容器放置

- 扇出方案创建了一个四象限结构,便于在 PCB 底部放置去耦电容器和大容量电容器。

- 通常 0210 或定制的 0402 封装电容器应安装在尽可能靠近电源过孔的位置,它们之间的距离应小于 50 mils。

- 可以在 BGA 通孔阵列边缘附近放置一个额外的大容量电容器。

- 将去耦电容器靠近电源球放置对于最小化电感至关重要,这也确保了处理器对高速瞬态电流的需求。

- 选择合适的过孔尺寸有助于设计人员保留足够的布线空间。

- 过孔焊盘的推荐几何形状是:焊盘尺寸为 18 mils,钻孔为 8 mils。

- 将最大的电容放在预算和制造可以支持的最小封装中。对于高速旁路,选择最小封装的所需电容(例如,0.22uF 和封装 0201)

- 最小化到小型电容的走线长度(电感)。

- 串联电感抵消了电容。

- 使用通孔将帽直接连接到 GND 平面。

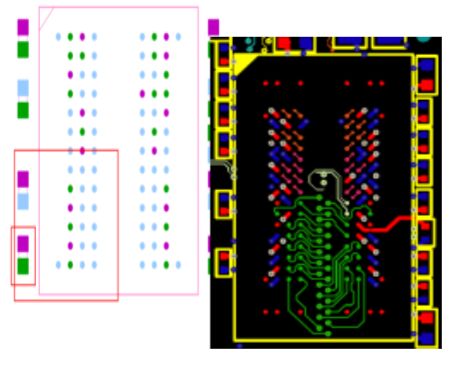

DDR 布局布线规则

- 布局的最终目的是限制最大走线长度并留出适当的布线空间。

- 放置位置不限制安装设备的 PCB 一侧。

- 根据研究人员进行的研究,FLY-by拓扑优于树拓扑。Fly-by 拓扑的优势在于它支持更高频率的操作,减少了stub的数量和长度,从而提高了重载信号的信号完整性和时序。

板载 DDR 和 DIMM 的布线如下所示。

总线拓扑 - 板载两个 UDIMM

信号分组

在路由 DDR 信号之前,我们必须首先以特定方式对信号进行分组,

- 组应包括 8 位数据、数据选通和掩码数据/数据反转,产生 11 个信号。例如,信号如下:

- BYTELANE0 DQ [7:0]、DM0/DBI0、DQS_P0、DQS_N0

- BYTELANE1 DQ [15:8]、DM1/DBI1、DQS_P1、DQS_N1

- 地址可以单独分组,包括控制、命令和时钟信号。

- 数据分组完成后,应尽可能短地将其连接到处理器。

- 地址、命令和控制信号以数据带宽的一半运行,因此它们会更长。

信号路径

- 数据线与处理器之间的布线距离尽可能短。

- 地址线、命令、控制线以数据带宽的一半运行,因此它们会更长。

- 来自同一通道/组的数据字节和控制线应在同一层上布线。

- 地址/命令/控制/差分时钟应该在同一层上布线,但如果出现空间问题,它们也可以在不同的层上布线。

- 地址/命令/控制/差分时钟是路由拓扑

- T型拓扑

- (Fly-by)拓扑

- 从芯片 0 开始的控制器路由到芯片 n 路径,按字节通道号顺序,Chip 0 是低数据位(Bytelane0)/chip,“ n”代表高位数据位(Bytelane3)。

- Fly-by拓扑的优点:

- 支持高频操作

- 减少stub的数量和长度,从而提高重载信号的信号完整性和时序。

- 通过在地址和数据组的点对点拓扑信号之间造成飞行时间偏差来降低同时切换噪声 (SSN)。

- Fly-by 拓扑具有非常短的stub,消除了反射。

- 在 T 型拓扑中,随着存储设备负载数量的增加,trace stub被加长。

- 在 T 拓扑中,时钟走线需要以比每个字节通道的选通走线更长的延迟进行布线。

- 在大多数情况下,DDR2 及其以前的类别遵循 T 拓扑布线。

- DDR3 及其下一代所有类别都遵循 Fly-by 拓扑。

走线长度匹配

长度匹配是分组进行的。常见的长度匹配路由组有:

- 时钟到地址/命令组

- 时钟到选通组

- 选通数据组

使用蛇形路径匹配信号的长度,按照制造数据表遵循数据字节通道的布线指南,所有信号之间的最大偏差应小于存储器控制器驱动的时钟周期的 +/-2.5%,时钟走线应该比数据/选通/控制线稍长,以便时钟到达目的地晚于数据/选通/控制。

例如,如果在PCB上使用介电常数为4的普通FR4材料,在1.2GHz的不同时钟频率(即833ps时钟周期)下,最大偏差应为+/-125mil(25psec)信号。

相对传播延迟

- 字节通道内所有成员之间 1 –5mils

地址/命令/控制

- 控制器与第一个存储器 IC 之间的距离为 100 –200 mils

- 时钟到地址/命令 +/- 25psec(125 毫秒)

- 存储器 IC 之间 10 –20 mils

传播延迟

- 从控制器到第一个存储器 IC 1500 –1750mils。

- 存储器 IC 之间的距离为 650 –750 mils。

差分相位容限

- 所有数据选通和时钟差分对为 1 –5mils

数据总线终端

- 当点对点连接在 2” 到 2.5” 范围内时,可以使用串联电阻器端接,电阻器位于传输线的中心。

- 使用片上端接 (ODT) 直接连接 DRAM 端接,以提高信号质量和降低价格。

时钟终止

- 在链中的最后一个 SDRAM 设备上放置了 100 欧姆差分终端器,这是 100 欧姆差分信号。

走线特性阻抗

对于单端走线,如数据线特性阻抗为 50Ω,差分走线如 Clock 和 Strobe 为 100Ω。

- 单端阻抗 = 50Ω

- 可以使用更小的走线宽度 (5–6 mils)。

- 相似信号之间的间距应分别扩展到 3x(5 mils)或 2.5x(6 mils)。

Crosstalk

当走线以高频率和高边缘速率运行时,串扰问题变得更加严重,尤其是在 HDI PCB 中,为了最小化耦合效应,两条相邻信号走线之间的间距应至少为走线宽度的 2 倍,通常为 3 倍。然而,由于空间限制,大的走线间距很难在 PCB 上实现。

BGA 逃逸布线是将阻抗和 HDI 串扰保持在限制范围内的有效方法。

HDI PCB 设计中阻抗匹配的文章。

电路模拟

为了获得最佳性能,布局设计师需要对信号完整性和串扰进行电路板模拟, 设计人员应确保通过对存储器实现中每个信号组的仿真确定最佳端接值、信号拓扑和走线长度,要了解如何消除 HDI PCB 中的串扰问题,

如何避免 HDI 基板中的串扰?

PCB的一般设计指南

- 规划电路板堆叠。

- 规划走线宽度和走线间距。

- 仔细规划组件放置,例如Fly-by拓扑中的存储器 IC,并根据指南放置终端电阻器、滤波电容器等

- 根据数字和模拟组件规划接地层和电源层。

- 测量字节通道的网络/信号的长度。

- 导入 IC 制造商提供的正确 IBIS(输入/输出缓冲器信息规范)模型。

- 按计划放置元件和电源平面,并首先路由一些关键的单端和差分信号(时钟/选通)并测量总线的第一位/最后一位长度以进行长度匹配。

- 在必要的地方使用额外的蛇形轨迹在线路中添加延迟。

- 测量过孔阻抗。

- 设计师需要在布局与仿真之间来回处理。

- 验证是否符合建立/保持时间/偏斜/延迟。

- 检查信号之间的串扰。

- 获取信号完整性解决问题是的关键,以获得最佳的性能。