台湾普瑞Parade PS8625| PS8625芯片方案|EDP转LVDS方案| 替代与兼容PS8625

PS8625是一个显示端口™ 到LVDS转换器设计的PC机,利用GPU和显示端口(DP™) 或嵌入式显示端口(eDP™) 输出和接受LVDS输入的显示面板。

PS8625将作为DP或eDP接收器设备出现在视频源中,并将作为LVDS显示面板的LVDS源设备。该设备是一个完全集成的解决方案,不需要外部CPU、内存、时钟基准或电压调节器。PS8625可配置为从显示器DDC通道或从连接到PS8625(提供I2C主机)的选件外部ROM读取EDID。外部ROM还可以包括配置代码,以定制设备操作和接口定时。PS8625提供显示面板上电顺序和背光控制,包括PWM生成。背光特性可通过使用eDP v1.2 DPCD控制寄存器的DP AUX信道上的视频源进行控制。或者,视频源可以将背光控制信号提供给PS8625,PS8625将其选通以进行面板通电排序,或者视频源可以绕过设备直接控制面板背光。

PS8625主要特性

允许使用带DisplayPort的LVDS显示面板™ 或eDP™ 视频源设备

支持1920×1200@60Hz时24位色深

Parade的CrystalFree不需要外部水晶或时间参考™ 技术

单台3.3V或2.5V低功耗电源,1920×400mW以下1200@60Hz时,每像素24位

双电源选项为I/O使用3.3V或2.5V,核心使用1.35V或1.2V

无固件操作,支持硬件引脚配置或初始代码配置

可选I2C主机,用于外部EEPROM初始代码加载和设备配置

芯片控制的可选I2C从接口

ESD:HBM 8kV at连接器引脚

工作温度范围可用性:-20°C至70°C(商用),-40°至85°C(工业)

7x7mm 56针QFN封装(无卤素,符合RoHS)

DisplayPort输入

符合VESA DisplayPort™ 规范1.1a

支持18、24和30 bpp RGB颜色格式输入

包括带集成HDCP密钥ROM的HDCP 1.3解密引擎

符合VESA嵌入式显示端口(eDP™) 规范1.2,带辅助启动背光控制

支持1通道和2通道主连接配置

1.62 Gbps和2.7Gbps的链路速率

支持各种特定于GPU的电源管理协议

支持所有eDP显示身份验证方案,包括ASSR

支持SSC 0.5%向下扩展

支持全链接训练、快速链接训练和无链接训练

低电压差分信号接口

单链路或双链路LVDS输出,时钟速度高达135MHz

支持1920×1200@60Hz时18或24位色深

LVDS扩频时钟频率高达2%

支持LCD面板电源顺序控制

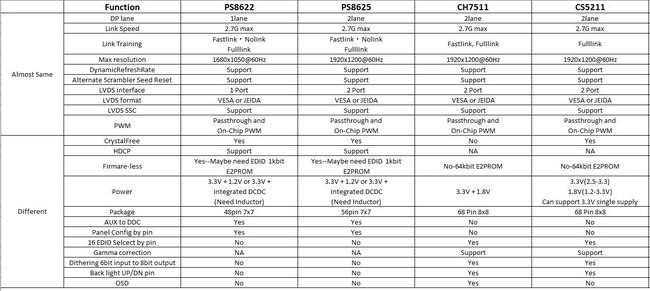

CS5211可替代与兼容台湾普瑞Parade PS8625芯片,且性能更优,芯片成本更低,具体下面详细介绍一下CS5211的先关特性和参数。

CS5211是一个eDP到LVDS转换器,配置灵活,适用于低成本显示系统。CS5211与eDP 1.2兼容,支持1通道和2通道模式,每通道速度为1.62Gbps和2.7Gbps。CS5211采用强大的SerDes技术,可以以较低的误码率恢复高速串行数据。

CS5211 LVDS发射机支持单端口和双端口模式。CS5211支持的最大分辨率是WUXGA(1920x1200)。CS5211有4个配置引脚,可支持16种不同的组合一个EEPROM图像的面板分辨率和LVDS工作模式。此外,还提供了一个简便的工具来编辑、生成和更新EEPROM图像以供定制配置。

通过优化设计,使用CS5211有利于节约BoM成本。该芯片集成了时钟源,节省了外接晶体,支持宽范围电源(核心功率为1.8~1.2V),节省了车载电源设备,CS5211的总功率小于300mW,简化了供电网络设计。很容易将CS5211集成到流行的低成本显示系统中。

CS5211详细功能描述

1.1概述

CS5211是一种桥接芯片,可将eDP输入转换为LVDS信号。CS5211的高级接收器支持嵌入式显示端口(eDP)1.1规范。该设备将解码RGB格式的高速eDP的交流耦合差分信号,并驱动与LVDS接口集成的TFT面板。内置LVDS发射机配备灵活的OpenLDI/SPWG位映射,能够驱动单端口或双端口(18/24位)LVDS面板。CS5211的LVDS输出可以配置为支持高达1920x1200分辨率,刷新率为60赫兹。此外,CS5211还具有背光逆变器控制、亮度调节、图像抖动算法和EMI抑制机制等增强显示功能,有利于系统制造商。

CS5211配置为eDP到LVDS转换器;LVDS发送器支持单端口18位、单端口24位、双端口18位和双端口24位传输,并支持OpenLDI和SPWG位映射。

1.2主链路接收机

CS5211的主链路接收器功能块配备了两个eDP主链路通道,以支持高速、高带宽和单向数据流,以驱动高达1920x1200分辨率的TFT-LCD显示器。

通过交流耦合差分对(DP0P/DP0N和DP1P/DP1N引脚)接收的2.7Gbps和1.62Gbps两种类型的链路速率被CS5211的解码器块反序列化为三个分量(RGB)流。

CS5211利用其先进的时钟数据恢复技术同步链路速率,并将输入流反序列化为并行数据,这些数据将根据ANSI8B/10B编码方案(信道编码在ANSI X3.230-1994中指定)解码为特殊符号。解码后的码元被CS5211的主流解压块解包,以恢复RGB分量视频流和原始视频定时信息,这些信息将被CS5211的LVDS编码电路用于驱动LCD显示。

CS5211支持通过ASSR进行eDP身份验证。

1.3辅助通道

CS5211的AUXP/AUXN管脚对用作eDP AUX信道,支持半双工双向耦合差分信号,数据速率为1Mbps,用于链路通信。当系统上电时检测到热插拔管脚连接状态发生变化时,CS5211将其AUX通道置为空闲状态,等待来自源设备的请求事务。当源设备需要从同步模式开始为链路服务或设备服务启动事务时,CS5211的接收器将自动锁定并响应辅助信道通信所需的manchester II编码方块。还有, 差分对允许源系统在链路训练/链路维护期间更新CS5211的DPCD并检索EDID数据。源设备可以利用CS5211的AUXP/AUXN引脚在正常操作期间调整面板的亮度水平。

1.4 LVDS面板选择

不同的LVDS面板可能具有不同的EDID,并且需要特定的配置,例如电源顺序定时。

CS5211支持由GPIO[3:0]引脚选择的16种不同LVDS面板配置。CS5211在上电加载固件后读取SGPIO[3:0]状态,然后CS5211加载LVDS特定配置。

在实际应用中,GPIO[3:0]可以由电阻或其他芯片的GPIO控制。控制电阻(1)GPIO[3:0]可通过CS5211 PCB板上的上拉/下拉电阻连接到高/低电平;CS5211上电后可获得正确的LVDS面板选择值或获得复位信号。

方法2(由其他芯片的GPIO控制)

在CS5211应用系统中,GPIO[3:0]可以由其它芯片的GPIO引脚控制。重置信号被发送给CS5211 resetb引脚后,GPIO引脚必须在100ms内保持稳定值。否则,必须再次发出复位信号。建议每次改变LVDS面板选择值时,通过控制芯片重置CS5211。

1.5 LVDS输出数据映射

SPWG和OpenLDI是CS5211支持的两种LVDS编码方案,可以通过编程CS5211寄存器进行选择。这些OpenLDI/SPWG配置参数可以存储在启动ROM并在系统通电期间加载到CS5211寄存器中。

表1-1双LVDS信道的信号映射

1.6 PWM占空比模式

CS5211'有两个用于面板背光亮度调光控制的PWM输出引脚,两个引脚都可以支持0%到100%的占空比范围。

CS5211支持两种PWM控制模式:直通模式和TCON PWM输出模式。t根据寄存器DPCD:0x00721位[1:0]的设置切换两种模式,此寄存器可由DP源设置。

方法1(直通模式)

在此模式下,CS5211将PWM输入旁路到PWM输出。

方法2(TCON PWM输出模式)

在此模式下,CS5211可自行产生PWM输出,预设频率为400kHz。在这种模式下,通过对CS5211的BLUP或BLDN引脚施加脉冲,可以增加或降低背光亮度。

如果DP Source将DYNAMIC _backlight_ ENABLE设置为1,CS5211可以通过分析视频数据的亮度水平来动态调整背光亮度。

如果不使用PWM控制,CS5211可以通过软件将PWM输出引脚设置为高或低。

1.7 LVDS功率排序

CS5211符合SPWG LVDS面板电源顺序要求。图6所示的定时规范是VESA电视面板标准中要求的超集。面板的控制时序参数可以通过软件设置为E2PROM ROM,并在设备通电时被编程到CS5211的电源控制寄存器中。

1.8 LVDS变送器

除了支持OpenLDI和SPWG规范外,CS5211的LVDS发射机还能够驱动四种类型的面板电气接口——18位单通道、24位单端口、18位双通道和24位双通道。LVDS输出块还支持:

1.8.1灵活的同步控制

从DisplayPort主链路恢复的HSYNC/VSYNC可以单独反转,以满足特定LCD面板的输入要求。两个同步信号也可以强制为0以支持智能面板。

1.8.2灵活的LVDS数据输出映射

CS5211有一个灵活的LVDS输出引脚映射数据和时钟,以支持PCB顶部/底部安装。请参考寄存器编程部分如何更改LVDS引脚输出映射。

CS5211结构设计方框图:

CS5211与PS8625 PS8622各种参数对如下: