【Tessent】Tessent Scan and ATPG Users Manual 2022 ch8 Test Pattern Generation

Test Pattern Generation

- ATPG Basic Tool Flow

-

- ATPG inputs and outputs

- ATPG Process Overview

-

- Basic ATPG Process

- ATPG Tool Timing Model(理解的不是很明白)

- ATPG Tool Pattern Types

-

- Basic Scan Patterns

- Clock Sequential Patterns

- Multiple Load Patterns

- Sequential Transparent Patterns

- ATPG Procedures

-

- Tool Invocation

- Circuit Behavior Setup

-

- Equivalent or Inverted Primary Input Definition

- Primary Inputs and Outputs Addition

- Bidirectional Pins as Primary Inputs or Outputs

- How to Tie Undriven Signals

- Primary Input Constraints

- How to Mask Primary Outputs

- Slow Pad Addition

- Tool Behavior Setup

-

- Bus Contention Checks

- Multi-Driven Net Behavior Setup

- Z-State Handling Setup

- The ATPG Learning Process

- Capture Handling Setup

- Transient Detection Setup

- Scan Data Definition

-

- Scan Clocks Definition

- Scan Groups Definition

- Scan Chains Definition

- Clock Restriction Setup

- How to Add Constraint to Scan Cells

- Nofault Settings

- Rules Checks and Violations

- Good/Fault Simulaiton With Existing Patterns

-

- Fault Simulation

-

- Fault Type Designation

- Faults List Creation

- Pattern Source Designation

- Running Fault Simulation

- Undetected Faults List Writing

- Fault Simulation Debugging

- Circuit and Fault Status Reset

- Good-Machine Simulation

-

- External Pattern Source Specification

- Good Machine Simulation Debug

- Random Pattern Simulation

- Fault Information Setup for ATPG

- ATPG Operations

- Low-Power ATPG

- IDDQ Test Set Creation

-

- IDDQ Test Set Generation

-

- When to Perform the Measures

- Pattern Generation

- Running ATPG for IDDQ

- Leakage Current Checks

- Delay Test Set Creation

-

- Transition Delay Test Set Creation

- Transition Fault Detection

-

- Broadside (Launch-Off-Capture) Patterns

- Pseudo Launch-Off-Shift Patterns

- Generating a Transition Test Set

- Timing for Transition Delay Tests

- Transition Fault Detection and Multiple Clocks

- Pattern Failures Due to Timing Exception Paths

- SDC Timing Exception Effects

- Debugging Test Coverage With Timing Exceptions

- Path Delay Test Set Creation

-

- Path Delay Fault Detection

- The Path Definition File

- Path Definition Checks

- Generating a Path Delay Test Set

- Path Delay Testing Limitations

- At-Speed Test With Named Capture Procedures

- Mux-DFF Example

- Support for Internal Clock Control

- Generating Test Patterns for Different Fault Models and Fault Grading

- Timing-Aware ATPG

- Bridge and Open, and Cell Neighborhood Defects UDFM Creation

- Pattern Generation for a Boundary Scan Circuit

- Pattern Generation for a Boundary Scan Circuit

- Verify Test Patterns

-

- Design Simulation With Timing

-

- The Verilog Test Bench

-

- Verilog Simulation

- Verilog Plusargs

- Clock Monitoring During Simulation

- Parallel Scan Cell Monitoring During Serial Scan Pattern Simulation

- Parallel Versus Serial Patterns.

- Potential Causes of Simulation Mismatches

ATPG基本过程。

ATPG Basic Tool Flow

- 使用

tessent -shell调用Tessent Shell,然后set_context patterns -scan设置环境,此时激活了工具的ATPG功能。 - 使用

read_cell_library读取DFT library,使用read_verilog读取结构化设计网表(门级网表)。网表中的每个单元(elements)在指定的DFT库中都必须具有等效的描述,工具读取网表和库之后,会一一检查。 - 读取网表和库之后,工具进入setup模式。该模式下,直接使用命令或者使用dofile可以完成一些认为,如配置设计和扫描电路的信息,指定在设计打平阶段影响仿真模型创建的相关信息。

- setup相关内容配置完成之后,离开setup mode,此时会出发关于网表打平的操作。如果是第一次离开setup mode,工具会创建扁平化设计模型,如果之前已经离开过该模式或者使用了

create_flat_model命令,flatten model就已经存在了,如果改动不影响设计模型,则会生成新的flatten model。 - 详细的学习分析(learning analysis)

- flatten model创建完毕,并且学习其行为之后,开始进行DRC。

- DRC完成之后,工具进入analysis mode,此时可以对设计的向量集进行仿真

- DRC之后,还可以进行向量生成。此时,可以执行一些额外的步骤,如添加故障列表(fault list),然后基于该故障列表运行ATPG。在ATPG运行期间,工具会执行故障仿真,以此来验证生成的测试向量能够检测到目标故障。

不管是全扫描还是部分扫描电路,都可以在不同的约束下或者使用外部测试集的情况下运行ATPG。

使用ATPG工具生成测试集后,应将时序信息应用于测试向量,并在将设计和测试集移交给供应商之前对其进行验证。

ATPG inputs and outputs

ATPG工具基于多个输入文件可以生成测试向量集、故障列表、ATPG信息文件。如下图所示:

ATPG工具的输入:

- Design gate-level Verilog、a cell model from the design library、previously-saved, flattened model

- Tessent Procedure File 定义扫描电路工作过程的文件。可以自己写,也可以使用

write_atpg_setup命令让Tessent Scan工具自动生成。 - Library 设计库包含设计中用到的所有cells的描述。工具使用库将设计转换为用于故障仿真和测试生成的 flat 门级仿真模型

- Fault List 工具使用故障列表和工具当前的状态作为测试生成的起点,可以从外部读入故障列表。

- Test Patterns 工具使用故障列表和工具当前的状态作为测试生成的起点,可以从外部读入故障列表。(这是手册上的描述)(因该是之前提到的,在给定外部测试向量的基础上进行测试生成。)

ATPG工具的输出: - Test patterns 可以生成各种不同格式的测试向量

- ATPG informations Files ATPG过程的一些信息

- Fault List ASCII可读文件,包含标准Tessent故障格式中的内部故障信息。

ATPG Process Overview

要了解ATPG工具是如何工作的,您应该了解ATPG的基本过程、时序模型和工具生成的基本向量类型。

Basic ATPG Process

ATPG工具设置了默认值,因此,通过create_patterns命令第一次启动ATPG时,该工具将对目标故障列表执行随机向量故障仿真和确定性测试生成的有效组合。

Random Pattern Generation Using the ATPG Tool

工具首先对每个捕获时钟(capture clock)执行随机向量故障仿真,当仿真向量未能检测到至少0.5%的剩余故障时停止。然后,工具对没有捕获时钟的向量执行随机向量故障仿真,同时测量连接到时钟的原始输出端口的值。

ATPG约束和具有总线竞争(bus contention)的电路不是随机向量生成的最佳条件。如果指定ATPG约束,则该工具不会执行随机向量生成。

Deterministic Test Generation Using the ATPG Tool

使用随机向量的方法检测某些故障的几率非常低,因此,在完成随机向量仿真后,该工具对当前故障列表中选定的故障执行确定性测试生成。该过程包括为从故障列表中随机选择的一组故障生成测试向量。

在此过程中,该工具会识别并删除故障列表中的冗余故障(redundant faults)。在为故障仿真生成足够的向量之后,工具会给出冗余故障的数量、ATPG不可测故障的数量以及测试生成器识别的中断故障(aborted faults)的数量。然后,工具会选择另一组向量,迭代上述过程,直到除了测试生成过程中断的故障之外(即UC和UO),当前故障列表中没有其他故障,就会停止测试生成。

ATPG Tool Timing Model(理解的不是很明白)

工具使用一个基于周期(cycle-based)的时序模型,将测试向量按不同**测试周期(test cycle)**分组。ATPG工具的仿真器使用非扫描事件(non-scan events):force_pi, measure_po, capture_clock_on, capture_clock_off, ram_clock_on, and ram_clock_off。ATPG工具使用固定的测试周期,即不能对其进行修改。

最常用的test cycle包含以下事件:force_pi, measure_po, capture_clock_on, and capture_clock_off。用于读取或写入RAMs的测试向量包含以下时间: force_pi, ram_clock_on, and ram_clock_off。 可以通过时序文件将真实时间(real times)与每个事件关联起来

ATPG Tool Pattern Types

ATPG工具有几种不同类型的测试模式。也就是说,它可以根据设计的样式和电路以及指定的信息生成几种不同类型的测试向量。默认情况下,该工具生成基本扫描向量(basic scan patterns),该向量用于采用全扫描的设计(full-scan design)。

Basic Scan Patterns

如前所述,该工具默认生成基本扫描向量。扫描向量(scan pattern)包含以下事件:

- force_pi 在所有的扫描单元和原始输入端口施加一组值

- measure_po 观察原始输出和扫描单元的结果响应

- capture_clock_on/capture_clock_off 使用定义的扫描时钟将数据捕获到可观察的扫描单元

扫描向量借助适当的测试程序来定义如何控制和观察扫描单元。工具要求每个扫描向量(scan patterns)独立于所有其他扫描向量。基本扫描向量包含以下事件:

- 将数据加载(load)到扫描链(Load values into scan chains)

- 非时钟PI施加值(时钟关闭,约束引脚的值满足约束条件) (Force values on all non-clock primary inputs )

- 记录原始使出(连接到扫描时钟的端口除外) (Measure all primary outputs (except those connected to scan clocks))

- 给出脉冲捕获时钟或者应用选定的时钟过程 (Pulse a capture clock or apply selected clock procedure.)

- 取出(unload)扫描链中的值 (Unload values from scan chains.)

扫描链的laod 和unload的过程通常是同时发生的。

由于ATPG工具针对扫描设计进行了优化,因此基本扫描向量包含所有其他向量类型中的事件。

Clock Sequential Patterns

该类型的向量用于受限制的时序电路,也有助于RAM的测试,其主要包括以下事件:

- Load the scan chains

- Apply the clock sequential cycle

a. Force values on all primary inputs, except clocks (with constrained pins at their constrained values)

b. Pulse the write lines, read lines, capture clock, or apply selected clock procedure.

c. Repeat steps a and b for a total of “N” times, where N is the clock sequential depth - 1 - Apply the capture cycle.

a. Force pi

b. Measure po

c. Pulse capture clock - Unload the scan chains as you load the next pattern

要指示工具生成 Clock Sequential Patterns,必须使用set_pattern_type命令将时序深度设置为大于1的数字,如下所示:

SETUP> set_pattern_type -sequential 2

深度为0表示组合电路。深度大于1表示受限制的时序电路(limited sequential circuitry)。然而,时序深度的指定需要格外小心,应首先使用最低的时序深度并分析运行结果。如果需要,可以运行多次,每次都增加时序深度。最大允许深度限制为255,但出于性能原因,通常应将指定的值限制为5或更小。

Multiple Load Patterns

Sequential Transparent Patterns

ATPG Procedures

使用ATPG工具时的一些操作。

Tool Invocation

启动Tessent Shell,然后将context设置为 pattern -scan,命令如下:

% tessent -shell

SETUP> set_context patterns -scan

当启动Tessent Shell时,该工具认为您要做的第一件事是设置电路行为,因此它会自动将您置于setup mode。如果要将系统模式更改为analysis,使用set_system_mode命令。

Circuit Behavior Setup

ATPG工具提供了很多命令学设置电路行为,这些命令必须在setup mode下运行,常用的方法是将命令放到一个dofile文件中。

Equivalent or Inverted Primary Input Definition

在电路应用环境中,通常出现被测电路的多个原始输入必须始终具有相同(等效)或相反的值。指定引脚等效 pin equivalences )会将选定的PI引脚约束为上一次PI引脚值的相同值或相反值。

相关命令如下:

- add_input_constraints — Adds pin equivalences.

- delete_input_constraints — Deletes the specified pin equivalences.

- report_input_constraints — Displays the specified pin equivalences

Primary Inputs and Outputs Addition

在某些情况下,您可能需要更改测试向量应用的点(PI)或输出值测量点(PO)。当添加之前未定义的PI时,它们被称为用户类PI(user class primary inputs),而原始的PI被称为系统类PI(system class primary inputs)。

添加PI和PO的命令分别为add_primary_inputs和add_primary_outputs,其他相关命令如下:

- delete_primary_inputs — Deletes the specified types of primary inputs.

- report_primary_inputs — Reports the specified types of primary inputs.

- delete_primary_outputs — Deletes the specified types of primary outputs.

- report_primary_outputs — Reports the specified types of primary outputs.

Bidirectional Pins as Primary Inputs or Outputs

在测试生成过程中,ATPG工具自动确定双向引脚(bidis)的工作模式,并避免在这些引脚不处于输入模式时创建驱动这些引脚上的值的向量。然而,在某些情况下,你可能需要让工具将双向引脚视为PI或PO。

How to Tie Undriven Signals

Primary Input Constraints

工具可以在ATPG过程中约束PI。

使用add_input_contraints命令对特定一脚添加引脚约束。可以指定一个或多个PI引脚路径名,将其约束为以下格式之一:constant 0 (C0), constant 1 (C1), high impedance (CZ), or unknown (CX)。

How to Mask Primary Outputs

设计可能包含某些没有选通功能PI,或者在类似的情况下,您可能希望屏蔽某些输出,使其不受观察,以进行设计权衡实验(design trade-off experimentation)。

在这些情况下,可以使用add_output_masks命令屏蔽这些POs。

Notes:

对用只能通过masked outputs检测到的故障,ATPG工具将其归类为AU,而不是UO。

Slow Pad Addition

告诉运行测试向量的时候(可能用于路径延迟测试),从内部寄存器通过I/O pad 返回到内部寄存器的回路可以在单个时钟周期内稳定下来的假设并不总是安全的。回路(loopback path)在单个时钟周期内稳定的假设可能会导致ATPG向量的验证出现问题,或者导致测试期间的良率损失。

Tool Behavior Setup

除了为ATPG工具指定有关设计的信息外,还可以设置您希望ATPG工具如何处理某些情况,以及在各种过程中投入多少精力。相关命令如下:

- set_learn_report — Enables access to certain data learned during analysis

- set_loop_handling — Specifies the method in which to break loops.

- set_pattern_buffer — Enables the use of temporary buffer files for pattern data.

- set_possible_credit — Sets credit for possibly-detected faults.

Bus Contention Checks

Multi-Driven Net Behavior Setup

Z-State Handling Setup

The ATPG Learning Process

Capture Handling Setup

Transient Detection Setup

Scan Data Definition

必须先定义扫描时钟和扫描链,然后应用程序才能执行规则检查(在退出setup mode时进行)。

Scan Clocks Definition

工具将任意能够将数据捕获到到时序单元(sequential elemetns)的信号(如系统时钟,sets和resets)看作扫描时钟。因此,为了利用扫描电路,您要通过将这些“时钟信号”添加到时钟列表(clock list)来定义它们。

Scan Groups Definition

Scan Chains Definition

Clock Restriction Setup

How to Add Constraint to Scan Cells

Nofault Settings

Rules Checks and Violations

在退出setup模式时,ATPG工具会执行模型扁平化、学习分析和规则检查。如果在规则检查过程中发生错误,应用程序将保持在setup模式,以便更正错误。有些错误时容易解决的,如测试过程文件(test procedure file)解析时出现的错误;有些错误时复杂难解的,如和时钟定义或者通过扫描链的数据移位等。

Good/Fault Simulaiton With Existing Patterns

故障仿真的目的是确定当前向量对故障列表中的故障的覆盖范围。“good” simulation的目的是验证仿真模型。通常使用ATPG工具的good and fault simulation功能来对现有手动或ATPG生成的向量集进行评级。

Fault Simulation

故障仿真在analysis模式下运行,无需额外设置。

Fault Type Designation

默认故障类型时 stuck-at,使用set_fault_type命令可以更改故障类型,故障类型包括: toggle, pseudo stuck-at (IDDQ), transition, path delay, or bridge。(如果是生成测试 stuck-at故障的测试集,是可以不用设置故障类型的。)

无论何时更改故障类型,应用程序都会删除当前故障列表和当前内部测试集。

Faults List Creation

运行故障仿真之前,需要一个故障列表。使用add_faults命令创建故障列表。通常会使用如下所示的使用全部故障创建此列表

>add_faults -all

Pattern Source Designation

使用read_patterns可以读取外部向量,然后在此基础进行故障仿真和测试生成。

ATPG工具可以使用选定数量的随机向量执行仿真,相关命令为simulate_patterns。

和向量仿真一起使用的其他命令如下:

- set_capture_clock — Specifies the capture clock for random pattern simulation.

- set_random_clocks — Specifies the selection of clock_sequential patterns for random pattern simulation.

- set_random_patterns — Specifies the number of random patterns to be simulated.

Running Fault Simulation

使用simulate_patterns命令运行故障仿真过程。对于不同的向量源,可以根据需要多次重复此命令。

其他相关命令如下:

- simulate_patterns— Runs the fault simulation process.

- report_faults — Displays faults for selected fault classes.

- report_statistics — Displays a statistics report.

Undetected Faults List Writing

通常,在对外部向量集执行故障仿真后,应保存故障列表。然后,可以使用此列表作为ATPG的起点。

write_faults命令可以保存故障。

在analysis模式下,使用read_faults命令可以将故障重新读入ATPG工具。

Fault Simulation Debugging

为了调试故障模拟,可以使用add_lists和set_list_file命令编写一个引脚值列表,这些值在有无故障的情况下是不同的。

add_lists命令指定要报告的引脚。

set_list_file命令指定存放选定引脚仿真值的文件的名称。默认行为是将引脚值写入到标准输出。

Circuit and Fault Status Reset

使用reset_state命令可以将电路状态和故障列表中所有可测试故障的状态重置为未检测到。

这样做可以使用当前故障列表重新运行故障仿真,不会删除当前内部测试集。

Good-Machine Simulation

给定一个测试向量,可以Good-Machine Simulation来预测无故障电路的输出逻辑值。

Good-Machine Simulation 在 annalysis 模式下运行,无需其他额设置。

External Pattern Source Specification

默认情况下,仿真使用的ATPG生成的内部向量源。使用如下命令可以对外部向量执行仿真。

ANALYSIS> read_patterns filename

Good Machine Simulation Debug

您以通过多种方式调试 Good Machine Simulation 。

如果要在批处理模式(batch mode)下运行仿真并保存某些引脚的值,可以使用add_lists和set_list_file命令。add_lists命令指定要报告的引脚。set_list_file命令指定存放选定引脚仿真值的文件的名称。

如果欢执行交互式调试(interactive debugging),可以使用simulate_patterns和report_gates命令来检查内部pin的值。

Random Pattern Simulation

运行随机向量仿真的典型过程。

Fault Information Setup for ATPG

ATPG Operations

Low-Power ATPG

IDDQ Test Set Creation

ATPG工具支持用于IDDQ测试的伪固定故障模型(pseudo stuck0-at fault model)。

该故障模型可以检测CMOS电路中的大多数常见缺陷(如电阻短路),而无需昂贵的晶体管级建模。

工具基于伪固定故障模型创建IDDQ向量。首先使用set_fault_type命令将故障类型设置为IDDQ。

在IDDQ测试生成过程中,工具将时序器件(如扫描单元或非扫描单元)输入端的故障划分为BL (Blocked)故障。这是因为触发器和锁存器(filp-flop and latch)实现方式的多样性意味着伪固定故障模型不能可靠地指导ATPG工具为其创建良好的IDDQ测试向量。

相比之下,一个简单的组合逻辑门有一个共同的、完全互补的实现方式(例如,一个NAND门在其输出和Vdd之间有两个并行的pFETs,在其输出和Vss之间有两个串联的nFETs),因此该工具可以更可靠地声明检测到的伪固定故障。

触发器的开关级(switch level)实现变化如此之大,以至于假设一个特定的实现是非常可疑的。因此,工具持悲观态度,报告的覆盖率低于实际水平,因为对于所有IDDQ向量,不太可能未检测到这种缺陷。

使用ATPG工具,可以基于用户指定的检查(user-specified checks)生成IDDQ模式。这些检查可以帮助确保IDDQ测试向量不会增加无故障电路中的IDDQ。

IDDQ Test Set Generation

基本的IDDQ模式生成过程,并提供了一个典型的IDDQ模式生成运行示例。

When to Perform the Measures

IDDQ测试向量中,必须包含告诉tester进行IDDQ测量的语句。在文本格式中,这个IDDQ测量语句或标签如下所示:

measure IDDQ ALL 默认情况下,ATPG工具将这些语句放在可以包含IDDQ测量的向量(周期)的末尾。您可以手动将这些语句添加到外部向量集的向量(循环)中。

Notes:

对于具有IDDQ向量的SSN设计,重定向向量(retargeted patterns)的捕获周期是同步的。这为测量IDDQ提供了一致的周期。这个重定向向量集之外的块必须被控制为静止状态(quiet state),这样IDDQ测量才能最有效。

Pattern Generation

在向量生成之前,您可能设置工具在创建最佳IDDQ向量时必须遵守的限制。与任何其他故障类型一样,在分析模式中发出create_patterns命令,将生成一个针对当前列表中的IDDQ故障的内部测试集。

Running ATPG for IDDQ

基于IDDQ故障类型的ATPG基本过程。

- Invoke Tessent Shell, set the context to “patterns -scan,” read in the netlist, set up the appropriate parameters for the ATPG run, pass rules checking, and then enter analysis mode.

SETUP> set_system_mode analysis

- Set the fault type to IDDQ

ANALYSIS> set_fault_type iddq

- Specify the number of desirable IDDQ patterns.

ANALYSIS> set_atpg_limits -pattern_count 128

- Run ATPG, generating patterns that target the IDDQ faults in the current fault list

可以在运行ATPG之前使用set_iddq_checks命令对生成的向量施加限制。还可以选择用read_faults命令在此时添加目标故障列表。

ANALYSIS> create_patterns -patterns_per_pass 1

然后,该工具自动添加所有故障。生成的内部向量已经包含了合适的IDDQ测量语句。

- Save these IDDQ patterns into a file.

ANALYSIS> write_patterns iddq.pats

Leakage Current Checks

对于带有上拉或下拉电阻或三态缓冲器的CMOS电路,无故障电路应该具有接近零的IDDQ电流。ATPG工具允许指定各种IDDQ测量检查,以确保无故障电路在测量过程中IDDQ电流不会增大。

使用set_iddq_checks命令指定这些选项。

默认情况下,该工具不执行IDDQ检查。ATPG和故障仿真过程都考虑指定的检查。

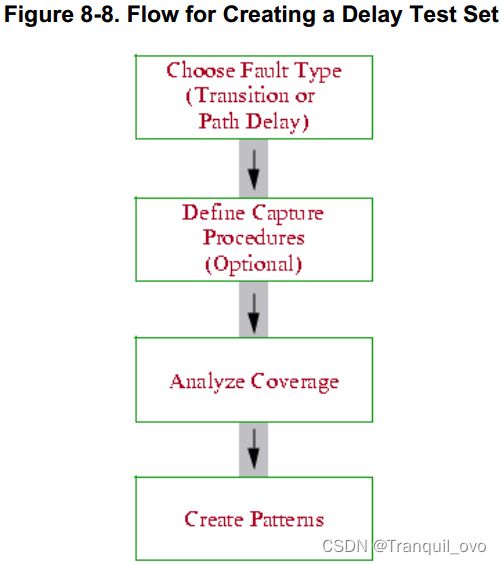

Delay Test Set Creation

ATPG工具中的延迟或“全速(at-speed)”测试有两种类型:转换延迟(transiton delay)和路径延迟(path delay)。延时测试的一般流程如下如所示:

具体的流程可能有所不同,根据设计和覆盖率目标,可能涉及一些步骤的多次迭代。

Transition Delay Test Set Creation

Transition fault逻辑门端口(或nodes)上的大延迟(gross delays)进行建模,能够测试每个端口的slow-to-rise或slow-to-fall行为。该模型可以代表的缺陷包括晶体管或互连的部分导通等。

图8-9所示,给出了了一个简单的与门,每个端都有的 slow-to-rise 和slow-to-fall 两种transition fault,总共有六个潜在的转换故障。由于转换延迟测试检查设备的运行速度,因此需要进行两个周期的测试(two cycle test)。

首先,设置了测试的所有条件,在图中,A和B分别为0和1。然后改变A的值,A端口值的变化应该使Y端口在预定时间(pre-determined time)在产生一个变化。在测试时间(test time)结束时,捕获电路响应,并测量Y端口的值。Y可能不会停留在0,但如果在捕获时间点进行测量时,Y的值仍然为0,则认为设备有故障。ATPG工具自动选择发射(launch)和捕获(capture)扫描单元。

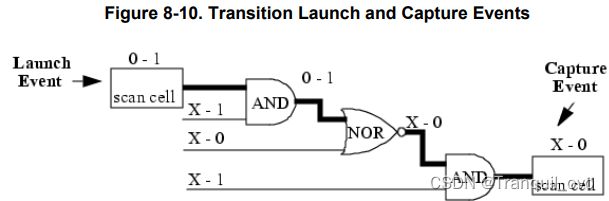

Transition Fault Detection

要检测转换故障,工具必须验证是否满足某些条件。必须检测到相应的stuck-at故障,而且,在前一个周期内,节点值必须与当前周期中检测到的值相反。

下图描述了一个小电路中transition测试过程中的发射和捕获事件(launch and capture events),可以在任何引脚上检测到转换故障。

Broadside (Launch-Off-Capture) Patterns

一种时钟顺序向量(clock sequential pattern),通常被称为boardside pattern。它的基本时序与图8-11所示相似,是ATPG工具在时钟序列深度(clock-sequential depth,设计中非扫描序列元素的深度)为两个或两个以上时默认创建的向量。create_patterns命令会自动为您选择并设置最佳顺序深度,也可以使用set_pattern_type -sequential命令指定此深度。

通常,这种类型的向量降低了对扫描使能时序的限制,因为在最后一次移位(shift)和启动(launch)之间有相对较长的时间。在最后一次移位之后,给定全速度(at-speed)时钟,用于发射和捕获。

生成 broadside transition patterns的向量的示例如下:

SETUP> add_input_constraints scan_en -c0 // force for launch & capture

ANALYSIS> set_fault_type transition

ANALYSIS> create_patterns

Pseudo Launch-Off-Shift Patterns

这种向量生成方法是在ATPG的捕获周期内建模的。向量通常包括两个周期。在第一个捕获周期期间,设计保持在移位模式(shift mode)。在第二周期,扫描使能关闭,执行捕获过程。这种方法更常用,因为它使工具能够使用PLL时钟快速执行移位和捕获。

可以使用命名为捕获的程序强制scan_en在第二个捕获周期从1变为0。scan_en通常是流水线(pipelined)信号,而不是PI,因此它可以在捕获周期具有以全速时序(at-speed timing)来切换,捕获周期通常比移位周期快得多。

Generating a Transition Test Set

转换故障对被测电路中逻辑门端口处的大延迟缺陷进行建模。此基本过程生成转换测试集,以测试逻辑门端口或节点的缓慢上升或缓慢下降行为。

Procedure:

- Perform circuit setup tasks, as discussed in “ATPG Basic Tool Flow” on page 317 and “ATPG Setup” on page 348 in this manual.

- Constrain the scan enable pin to its inactive state. For example:

SETUP> add_input_constraints scan_en -c0

- Set the sequential depth to two or greater (optional):

SETUP> set_pattern_type -sequential 2

- Enter analysis system mode. This triggers the tool’s automatic design flattening and rules checking processes.

SETUP> set_system_mode analysis

- Set the fault type to transition:

ANALYSIS> set_fault_type transition

- Run test generation:

ANALYSIS> create_patterns

如果故障类型设置为“transition”,执行create_patterns命令时,工具会自动执行add_faults -clock all

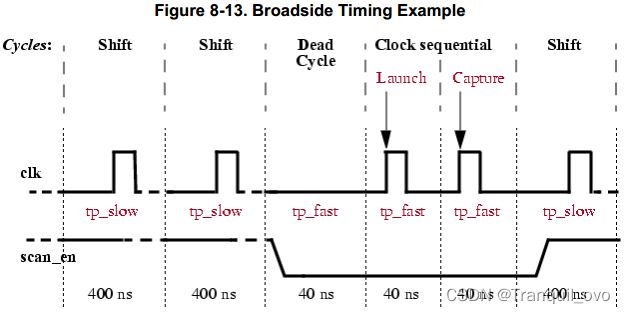

Timing for Transition Delay Tests

对于转换延迟测试,工具从测试过程文件(test procedure file)中获取时间信息。该文件描述了扫描电路工作过程。可以手动创建扫描电路,也可以使用Tessent scan为创建扫描电路。

测试过程文件包含基于周期的过程和时序定义,告诉ATPG工具如何操作设计中的扫描结构。

在测试过程文件中,时间板(timeplates)是用于定义测试循环(tester cycles)并指定每个循环中所有事件边缘触发的位置。如图8-11中所示的broadside testing概念,低速(slow cycles)用于 shifting (load and unload cycles) ,高速(fast cycles)用于发射和捕获( launch and capture)。图8-13为添加了示例时序的相同图表。

如上图所示,命名为tp_slow的timeplate定义了slow shift cycles的时钟周期为400ns,命名为tp_fast的timeplate定义了快速发射和捕获循环的时钟周期为40ns。

提供图8-13所示时序的 timeplates and procedures 如下所示。为了简洁起见,给出的不是完整的测试程序。通常情况下,还会有其他程序,比如设置程序(setup procedures)等。

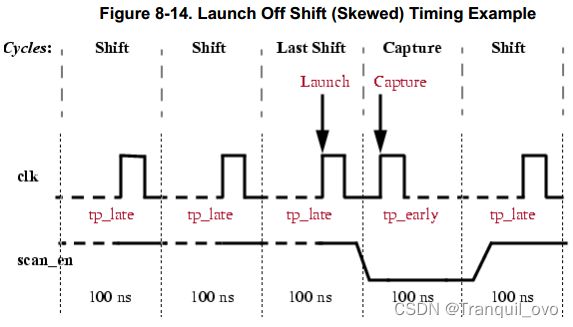

在这个例子中,launch和capture时钟之间有40ns。如果您想在launch和capture事件之间创建相同的时间,但所有时钟循环都有相同的周期,您可以在其周期内使时钟脉冲偏斜(skew)(如果您的测试仪能够提供此功能)。图8-14显示了这种偏斜的时序的具体样子。

以下 从timeplate and procedure拿出的部分显示了在测试过程文件中,称为tp_late和tp_early的timeplate定义如何管理skewed launch off shift pattern events:

通过将时钟脉冲移动到load_unload和shift循环的周期中的较晚时间段以及捕获周期的周期的较早时间段,实现了发射时钟和捕获时钟之间的40ns时间间隔。

Transition Fault Detection and Multiple Clocks

Pattern Failures Due to Timing Exception Paths

SDC Timing Exception Effects

Debugging Test Coverage With Timing Exceptions

Path Delay Test Set Creation

ATPG工具可以生成向量来检测路径延迟故障。这些向量确定用户定义的路径是否全速度(at-speed)正确运行。

确定要测试的路径(大多数人使用静态时序分析工具来确定这些路径),并将它们放在ASCII格式的路径定义文件中形成路径列表,然后将路径列表加载到工具中。

Path Delay Fault Detection

路径延迟测试需要逻辑值转换,这意味着需要发生两个事件来检测故障,即launch eevent和capture event。通常,发射和捕获都发生在扫描单元上,但它们可以发生在RAM上或PIs和POs上。

下图描述了路径延迟测试中的发射和捕获事件。

路径延迟向量是时钟序列向量(clock-sequential patterns)的一种变体。检测路径延迟故障的典型过程包含以下内容:

- Load scan chains.

- Force primary inputs.

- Pulse clock (to create a launch event for a launch point that is a state element).

- Force primary inputs (to create a launch event for a launch point that is a primary input)

- Measure primary outputs (to create a capture event for a capture point that is a primary output).

- Pulse clock (to create a capture event for a capture point that is a state element).

- Unload scan chains.

额外的force_pi/pulse_ clock循环可以发生在启动或捕获事件前后,循环(cycle)取决于设置发射条件或使捕获值到达观测点所需时序深度(sequential depth)。

Notes:

路径延迟测试通常需要比stuck-at故障测试更大的深度,工具计算和报告的时序深度是stuck-at测试时的最小深度。

为了使路径延迟测试效果最好,发射和捕获事件必须具有准确的时序安排,所有其他事件的时间安排没有很重要。

ATPG工具对路径延时故障的检测是 a hazard-free test, a robust test, a nonrobust test或 a functional test中的一个。如果将路径延迟向量保存为ASCII格式,则该工具会在文件中指向量使用哪种类型的检测, hazard-free test 和 robust test是最严格测试。

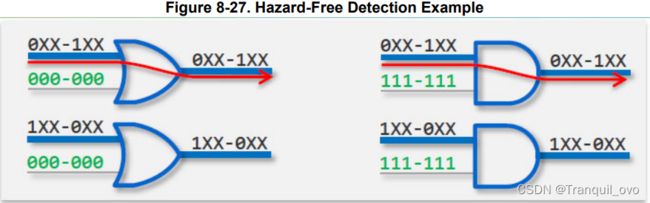

Hazard-free detection的条件是,用于敏化路径的逻辑门的输入值是非控制值,并在每个循环的每个帧(frame)中保持不变,如图8-27所示。与只使用鲁棒检测(robust detection)相比,Hazard-free detection和鲁棒性检测一起使用时,提供了具有额外限制的延迟测试。此外,和鲁棒性检测一起使用时,它能够保证了工具创建的任何鲁棒检测性测试向量( robust detection patterns)都是无冒险的(hazard free)。

鲁棒性检测(robust detection)要求用于敏化路径的逻辑门的输入值仅在每个循环的第一帧保持为非控制值。与无冒险测试类似,鲁棒性检测在故障检测期间保持路径上的逻辑门的值不变,因此不会影响路径时序。由于它避免了任何可能的重汇聚时序影响(reconvergent timing effects),是一种理想的检测类型,因此是ATPG工具首先尝试的方法。然而,由于其限制性,工具无法在许多路径上使用鲁棒性检测,如果无法创建鲁棒性测试,它会自动尝试创建非鲁棒测试()。工具将将通过鲁棒性测试检测到的故障放在DR(det_robust)故障类中。

Notes:

只有当路径中的每个门都是鲁棒的时,路径才能使用鲁棒性检测。如果路径中的任何单个门是非鲁棒的,则该路径只能使用非鲁棒检测。

下图给出了一个简单路径中的鲁棒检测示例。请注意,OR和AND上的选通值(gating value)在每个周期的第一帧上是稳定的,并且能够在发射和捕获事件期间保持适当的检测值。

非鲁棒检测(Non-robust detection)不需要用于敏化路径的选通输入为恒定值,它只需要适当的门控值,这意味着在捕获事件发生时它必须是非控制值。ATPG工具将通过非鲁棒性测试检测到的故障置于DS(det_simulation)故障类别中。

下图给出了一个简单路径中的非鲁棒检测示例。请注意,门控值(以绿色突出显示)在每个帧或周期中都不是恒定的。虽然该值可能会转换,但在捕获周期开始时,它必须是非控制的。

功能检测(Functional detection)进一步放宽了对用于敏化路径的选通输入的要求。路径上逻辑门的值不必像在鲁棒检测中那样保持恒定,也不必像非鲁棒检测所要求的那样在捕获事件时敏感。功能检测只需要选通输入不屏蔽沿着路径的转换的传播。工具将通过功能测试检测到的故障置于det_functional(DF)故障类别中。

图8-30给出了一个简单路径内上升沿转换的功能检测示例。在捕获事件发生时,逻辑门的off-path值既不稳定,也不敏感。然而,路径输入转换仍然传播到路径输出。

路径延时检测时用到的相关命令如下:

- analyze_fault — Analyzes a fault, including path delay faults, to determine why it was not detected.

- delete_fault_sites — Deletes paths from the internal path list.

- read_fault_sites — Loads in a file of path definitions from an external file.

- report_fault_sites — Reports information on paths in the path list.

- report_statistics — Displays simulation statistics, including the number of detected faults in each fault class.

- set_fault_type — Specifies the number of paths the tool should expand to when encountering an ambiguous path, by using the path_delay literal and -expand_ambiguous_paths switch.

- set_pathdelay_holdpi — Sets whether non-clock primary inputs can change after the

first pattern force, during ATPG. - write_fault_sites — Writes information on paths in the path list to an external file.

The Path Definition File

在外部ASCII文件中,必须使用路径定义文件来定义要在测试集中测试的所有路径。

对于每个路径,必须指定以下内容:

- Path_name —— 路径唯一名称

- Path_definition —— 从发射点到捕获点的路径拓扑结构,由**引脚路径名(pin pathnames)**的有序列表定义。每个路径都必须是唯一的。

ASCII格式的路径定义文件有几个语法要求,工具忽略任何以 // 或 # 开头的行作为注释。每个语句都必须在自己的行上,路径定于语法的格式基本格式如下:

PATH =

CONDition <0|1|Z>;

TRANsition_condition ;

PIN [+|-];

PIN [+|-];

...

PIN [+|-];

END [pathname];

- Path —— 指定路径名称语句

- Condition —— 可选语句,用于指定发射和捕获事件所需要的条件。每个条件语句包含两个参数:①内部或外部引脚的全称(full pin pathname);②引脚值。条件语句中引脚的有效值为0,1,Z。条件语句出现的位置必须在path语句和描述路径的第一个pin语句之间。

- Transition_condition —— 可选语句,指定测试向量中需要的额外转换(additional transitons)。该语句包含两个参数:①内部或外部引脚的全称(full pin pathname);②方向(direction)。语句出现的位置必须在path语句和描述路径的第一个pin语句之间。

Direction是以下四种之一:rising,falling,same,opposite。

rising和falling的作用是,在路径的第一个引脚产生一个transition时,在特定引脚上需要一个上升沿或下降沿。

same告诉工具在目标点生成一个和路径的第一个引脚的transition方向相同的transition,opposite则是定义一个相反的。

如图8.31所示的示例说明了transition_condition语句可能的好处。

对于一个robust test,与门的off-path端口,或者说gating inputs需要保持为1,工具在生成robust test测试向量的时候也会优先满足这个条件。然而,假设您希望扫描单元驱动的电路元件接收0-1转换。您可以在路径定义中添加transition_condition语句,为扫描单元指定上升转换。路径捕获点保持0-1转换,因此可以使用非鲁棒测试进行测试,并且还可以获得其他电路元件所需的转换。 - Pin —— 必要语句,使用pin的全称来定义路径上的pin(full pin pathname)。Pin语句必须按照从发射点(launch point)到捕获点(capture point)的顺序进行排列。引脚路径名后的“+”或“-”表示引脚相对于启动点的反转情况。“+”表示没有反转(该引脚上的transition和lunch transition方向相同),而“-”表示反转(和launch transition相反)。

Notes:

如果任意一个pin语句中使用了“+”或“-”,那么launch point必须要有一个 “+”。launch transition 必须总是“+”。

pin语句至少要有两条,第一条语句是有效的launch point(PI,data output of state element or RAM),最后一条语句是有效的capture point(primary output, data or clk input of a state element, or data input of a RAM)。当前引脚必须具有到先前引脚的组合连接路径,并且 edge parity 必须与path circuitry一致。如果语句违反了这两个条件中的任何一个,则该工具将发出错误。如果路径有边缘或路径模糊(edge or path ambiguity),则会发出警告。

路径可以包括state elements(穿过状态单元的数据或时钟输入),但必须明确命名路径中的数据或时钟引脚。如果没有,则该工具将无法识别路径并发出相应的消息。

- End —— 必要语句,表示路径描述结束。

在结束语句之后,可以指定路径的名称(可选操作)。但是,如果名称与path语句指定的路径名不匹配,则该工具会发出错误。

路径定义文件示例:

可以使用read_fault_sites命令读取路径定义文件。该工具将此文件中的路径加载到内部路径列表中。可以通过向新文件添加路径并使用再次使用read_fault_sites命令来添加新的路径到内部列表中。

Path Definition Checks

ATPG工具检查沿着所定义的路径的点是否正确连接,并确定路径是否存在不明确地方。**路径模糊(path amnbiguity)**指的是从一个定义点到下一个定义点有几个不同的路径,如图8.32所示。

在该示例中,所定义的点是Gate2的输入和Gate7的输入。在这些点之间存在两条路径,从而产生路径模糊性。当ATPG工具遇到这种情况时,默认情况下会将不明确路径扩展到最多10个不明确路径。如果希望该工具考虑不同数量的路径,可以使set_fault_type path_delay -expand_ambiquent_path命令指定。

在路径检查过程中,该工具也可能遇到边沿模糊(edge ambiguity)。边沿模糊指的是,沿着路径的门能够保持或反转路径边沿(path edge),具体取决于逻辑门的另一个其他输入端的值。图8-33显示了路径中的XOR门导致边沿模糊路径。

路径中的XOR门可以充当输入路径边沿的的反相器或缓冲器,这取决于其另一端口输入值。因此,XOR输出端的边缘是不明确的。通过路径定义文件,可以指示路径中定义点的边沿关系,通过为每个定义的点指定“+”或“-”来实现这一点。

set_fault_type path_delay -expand_ambiquent_path命令也可以扩展具有边缘模糊性的路径。

Generating a Path Delay Test Set

包含待测路径的路径定义文件确定好之后,就可以使用以下过程生成路径延时测试集。

- Perform circuit setup tasks as described in the ATPG Basic Tool Flow and ATPG Setup sections in this manual.

- Constrain the scan enable pin to its inactive state. For example:

SETUP> add_input_constraints scan_en -c0

- (Optional) Turn on output masking.

SETUP> set_output_masks on

- Add nofaults

- Set the sequential depth to two or greater:

SETUP> set_pattern_type -sequential 2

- Enter analysis system mode. This triggers the tool’s automatic design flattening and rules checking processes.

- Set the fault type to path delay

ANALYSIS> set_fault_type path_delay

- Write a path definition file with all the paths you want to test.If you want, you can do this prior to the session. You can only add faults based on the paths defined in this file.

- Load the path definition file (assumed for the purpose of illustration to be named path_file_1):

ANALYSIS> read_fault_sites path_file_1

- Specify any changes you want in how the tool expands ambiguous paths. By default, the tool expands each ambiguous path internally with up to 10 unambiguous paths. The following example limits the number of expanded unambiguous paths to a maximum of 4

ANALYSIS> set_fault_type path_delay -expand_ambiguous_paths 4

- Define faults for the paths in the tool’s internal path list:

ANALYSIS> add_faults -all

This adds a rising edge and falling edge fault to the tool’s path delay fault list for each defined path.

12. Perform an analysis on the specified paths and delete those the analysis proves are unsensitizable:

ANALYSIS> delete_fault_sites -unsensitizable_paths

- Run test generation:

ANALYSIS> create_patterns

Path Delay Testing Limitations

路径延迟测试不支持以下几种类型的电路配置。

- RAMS Within a Specified Path —— 只有当启动点在RAM的输出端时,才支持将RAM作为启动点。只有当捕获点位于RAM的输入端时,才支持将RAM作为捕获点。

- Paths Starting at a Combinationally Transparent Latch —— 只有当捕获点在锁存器的输入端时,才支持将组合Transparent Latch作为捕获点。

- Path Starting or Ending at ROM —— 应该将ROM建模为只读CRAM原语(即,没有任何_write操作),以使该工具能够支持路径延迟测试以ROM为起点或终点。

At-Speed Test With Named Capture Procedures

Mux-DFF Example

Support for Internal Clock Control

Generating Test Patterns for Different Fault Models and Fault Grading

Timing-Aware ATPG

Bridge and Open, and Cell Neighborhood Defects UDFM Creation

Pattern Generation for a Boundary Scan Circuit

Pattern Generation for a Boundary Scan Circuit

Verify Test Patterns

在使用仿真器测试电路功能并用ATPG工具生成测试向量后,应在基于时序的仿真器中运行测试向量,并将结果与ATPG工具的预测行为进行比较。该仿真可以指出两个工具之间的任何功能差异,还可以显示可能导致不同结果的时间差异。

Design Simulation With Timing

设计过程的这一环节,您应该运行一个完整的定时序验证,以确保Golden simulatiom和ATPG的结果之间的匹配。这种验证对于包含异步电路的设计尤其重要。

使用write_patterns命令保存了生成的测试模式,默认情况下,工具以并行(parallel)形式保存向量,使用 -Serial 选项可以保存为穿行(series)格式。使用-Sample选项可以减小串行模式文件的大小,工具从每个向量类型的向量中进项采样并保存,而不是使用整个测试集(MacroTest模式除外,它们既没有采样,也没有包含在采样的向量文件中)。这在串行向量仿真时很有用,因为采样向量文件的规模减小,仿真所需的时间也会减少。

Notes:

使用-Start和-End选项也会限制文件大小,但其保存的部分内部向量在仿真时无法提供非常可靠的向量特征表征。

采样的向量更接近于从整个图案集中获得的结果。

The Verilog Test Bench

如果选择-Verilog作为向量保存的格式,应用程序会自动创建一个testbench,你可以在基于时序的模拟器(如Questa SIM)中使用该测试台来验证工具生成的向量是否如ATPG工具预测的那样。

如下:

ANALYSIS> write_patterns pat_parallel.v -verilog -replace

该工具将测试向量写入一个或多个向量文件和一个高级的的Verilog测试台文件中,该文件实例化了设计的顶层。这些文件包含测试向量的应用和预期输出与仿真输出进行对比的过程。

在编译(compiling)向量、插入扫描链的网表和适当的仿真库之后,可以在Verilog仿真器中对这些向量进行仿真。如果ATPG工具的预期值和仿真器产生的值之间没有不匹配,则会显示一条消息,报告“no error between simulated and expected patterns”。如果有任何值不匹配,则表明发生了仿真不匹配(simulation mismatch),必须先进行纠正,然后才能在测试仪上使用这些向量。

Verilog Simulation

如果使用Questa SIM作为Verilog仿真器,使+acc=npr选项可以在减少运行时间的同时获得网络、端口和寄存器的可视化。如下:

% vsim -c -voptargs=+acc=npr

+acc=npr选项提供的可见性足以调试高级测试台(advanced test benches)。为了获得更高的可见性,但性能增益较小,可以使用如下命令:

% vsim -c -vopargs=+acc

Verilog Plusargs

Verilog plusargs是Verilog命令行参数,用于向仿真运行提供信息。名称plusarg源于这样一个事实,即参数(argument)名称前面有一个加号(+)。默认的Verilog测试台支持以下集中Verilog plusargs。

- STARTPAT — Sets the starting pattern number for the simulation.

- ENDPAT — Sets the ending pattern number for the simulation.

- CHAINTEST — Makes the STARTPAT and ENDPAT plusargs apply to the chain test patterns instead of scan test.

- END_AFTER_SETUP — Causes the test bench to simulate only the test_setup vectors and then finish without simulating any of the other patterns.

- SKIP_SETUP — Causes the test bench to skip simulating the test_setup vectors and start simulation with the first pattern (either chain or scan test, whichever is present).

- CONFIG — Specifies a name of the .cfg file, which controls which .vec files are simulated. For information about using this plusarg, refer to CONFIG Usage.

- NEWPATH — Sets a new file path for reading the Verilog test bench. The default length of the filename is 512. You can override this value using the SIM_TMP_REG_LENGTH parameter.

Clock Monitoring During Simulation

可以指示该工具生成Verilog test bench,该测试台能够在仿真过程中监测ATPG和IJTAG向量的时钟。此外,可以监控所有处于快速捕获模式的OCC实例的快速输入时钟。