CMOS图像传感器——像素设计基础

这一次,我们来聊聊CIS里最最关键的一个部分:像素!可以说几乎所有CIS的性能指标最终都由像素设计的好坏而决定。这么说吧:读出电路的设计决定了一个图像传感器的性能下限,而像素的设计决定了一个图像传感器的性能上限!

像素的种类可以是非常多的,比如:

- 可见光最常用的就是3T,4T,5T像素,如果还要加入更多的功能,比如全局快门(GS,Global Shutter),高动态(HDR,High Dynamic Range)等就要加入更多的晶体管;

- X光用于做Photon Counting的CTIA-based pixel;

- 用于Event sensor的DVS pixel;

- 用于3D成像的常作dToF(direct time-of-flight)的SPAD像素,常作iToF(indirect time-of-flight)的demodulation pixel;

- 再比如红外的direct injection, CTIA等,bolometer使用测电阻的pixel;

- 另外还有 TDI pixel,CCD的2/3/4-phase pixel 等等等等。

大的类别我们就有几十种像素,如果把所有人类设计过的像素都列出来,可能几百上千种,所以我们是不可能把所有这些像素全讲一遍的。这个世界上绝大多数CMOS图像传感器(>95%)都是基于可见光的2D成像,所以我们这里只重点介绍3/4/5T像素。如果大家有机会进入不同的公司工作,或者做全定制设计,再去接触更多好玩的东西。

首先我们来了解一个概念:快门 Shutter。快门决定了像素的进光方式和进光量,这也就决定了成像质量。快门可以分为机械快门(Mechanical Shutter)和电子快门(Electronical Shutter),而电子快门里又可分为卷帘快门(Rolling Shutter)和全局快门(Global Shutter)。

机械快门是由两块shutter blade组成,曝光前,第一块blade把整个sensor遮住,然后通常来说是有上至下将blade移开,开始曝光,随后第二块blade再从上至下移出,将sensor整个挡住,曝光结束。这两个blade的移动速度是非常非常快的,差不多可以达到35km/h,所以一个35mm的全画幅相机,blade可以让sensor在差不多1/400s内开始或结束曝光,所以可以说所有的机械快门都是“近似”全局快门的。那么机械快门如何实现更快的曝光时间呢?这个比较“简单”,就是在第一块blade还没有完全打开的时候,第二块blade就已经开始向下移进行遮挡,当然这个也是有极限的,最快大概就在1/8000s这个样子,想要更快的速度,那就需要电子快门了。

如下图,你就可以看到电子快门中卷帘快门和全局快门的区别。对于卷帘快门来说,每一行像素的曝光时间都至少间隔了一行像素的读取时间,比如我们读取一行需要10us,我们有1000行像素,那么第一行像素和最后一行像素曝光开始/结束时间就间隔了差不多10ms,这样在拍摄运动物理时,图像就会有明显的失真了;相应的,全局快门指的就是所有的像素都具有相同的曝光开始和结束时间了。

在开始讲解像素之前,我们解决上一讲提到的如何收集光产生的电子的问题,下图是一个4T像素剖面图。现代sensor基本都是使用pinned-photodiode(PPD)来收集电子的。PPD的结构就是有一个深度大致到1~2um深度的N-type layer,然后从硅表面到10~100nm深度内有一层掺杂浓度较高的pinning层,这一层pinning层和sub一起需要能让整个N掺杂层fully depleted,这个时候PPD内的电势就无法再升高了,即pinned,此时的电压即称为pinning voltage,它的范围一般在0.6~1.2V之间。Pinning voltage的选择,可以影响像素的很多性能,比如full well,dark current等等,所以如何进行pinning voltage的选择对各厂家来说是保密的,所以我也就不多说了。另外,因为pinning层比较浅,所以他的离子注入能量大概在10~20keV左右,而对于PPD层,他的离子注入能量范围就比较宽了,大概在50~500keV左右,而对于某些需要深PPD的像素,其注入能量可能高达几个MeV,而且PPD的离子注入也可能需要多次进行,比如50keV一次,100keV一次,200keV一次,每次掺杂的浓度也不尽相同,而这些掺杂具体该怎么做,对最后的性能影响很大,所以就需要做TCAD仿真了,这个仿真你有实力(有钱&有人)的话,可以自己做;或者在foundry厂的辅助下做。这里再说一下,当你从foundry厂拿回芯片以后,怎么确定pinning voltage做的对不对呢?一般foundry会有自己的test structure去测试这个,当然你也可以自己做一个test structure,而最常用的方法就是做一个基于PPD doping(P+ Pinning&N- PPD)的JFET,然后不断source和drain的电压,看什么时候测不到电流了,就说明整个PPD已经fully depleted,这个时候的电压就是pinning voltage。这种测试方法,其实也是有一定误差的,当然也有其他办法去测,但是我觉得这些讨论相对就比较学术了,这里就也不展开了。工程,就是用最简单的方法找到最优的近似 ,你说呢?

当有了N-doped PPD层之后,就会在其周围形成depletion region,这个depletion region的深度有多少,也是非常重要的。这是为什么呢?如图所示,如果光进入到depletion region才被吸收,产生的电子就会被立即扫入到PPD层中而储存在那里,空穴也会被扫出到sub里;但是如果光子是在sub里被吸收的,产生的电子就会在sub里随机移动,他的终结方式有三种:1)进入到该像素depletion region,从而被扫入到该像素PPD储存起来;2)进入到旁边像素的depletion region,而被旁边像素当作正常信号储存起来,这样就会降低MTF,图像质量下降,这个现象在越小的像素里越明显,所以你可以看到现在手机里的像素的都会加入DTI(deep trench isolation),就是为了减小这个串扰;3)再次跟其他的空穴recombine,同时产生一个能量大约等于禁带1.12eV的光子,这个光子有可能直接射出,或者在硅里经过一定的距离后再次产生一对电子-空穴对,这样就有很大概率,这个电子就丢掉了,导致QE降低。但是除非是某些科学级应用,我们的epitaxy厚度只会做到3~5um左右,电子大概率还是会被PPD存储起来的。那么如果光子是在MOS管的P well中被吸收的呢?那么电子就有可能直接进入FD(floating diffusion)中,这就会影响CIS中,特别是全局快门中,一个很重要的指标PLS(Parasitic Light Sensitivity)。根据以上讨论,可以发现,我们希望PPD下的整个epi也都是depletion region,这样产生的电子立马就会进入到正确的pixel中。所以你看,epi的选择也是很重要的。

下面就来解决我们上面提到的问题:为什么要用外延层呢?这里我说几个比较重要的原因。

- 首先bulk wafer在生产过程中,不可避免的会引入不少杂质,而这些杂质呢,就会成为产生dark current的源头。啥叫dark current?就是在无光照条件下,我们这个反偏的PN结中会产生并存储的电子数量。Dark current产生的原因有很多,我们这里先不展开了,这里说下有个主要原因就是各种杂质,或者表面态会在禁带中,特别是禁带中央,引入额外的能级,这样电子更容易跃迁,即Shockley-Read-Hall(SHR)效应。而使用epi呢,就能较好的控制杂质浓度。这里再补充一个小知识,就是gettering工艺,就是为了将epi中的杂质量减到最小。gettering在image sensor中用的很多,但在其他地方确不常见。不同的工艺厂,gettering方法不尽相同,比如引入oxygen precipitates等,取决于工艺厂的gettering方法,有的厂会让你在版图中某块区域加个特别的层指示gettering位置,而有的厂则不会。Gettering的基本原理就是故意引入一些晶格缺陷或掺杂,当Fe, Cu, W的等金属原子在硅片中游移时,就会被这些gettering sites锁住,这样就不会与正常的硅晶格产生作用,造成杂质能级。

- 其次bulk wafer的掺杂浓度不易控制,而我们从前面的讨论可以看到,衬底的掺杂浓度影响了depletion region的深度,为了保证芯片性能一致性,我们就希望很好的控制衬底的浓度。一般的应用,我们的衬底浓度水平会在10^15~16 /cm3,衬底电阻率大概是1~10 Ohm*cm,我们叫 Low-Res epi;而某些应用当我们需要depletion region比较深时,我们就会使用掺杂浓度在10^12~13 /cm3的epi,此时电阻率大概是500~5000 Ohm*cm,我们叫 High-Res epi,但是这里要注意,越低的掺杂越不好控制其一致性。

那么为什么外延层的厚度一般是3~5um呢?这个就跟我们前一讲说的absorption length相关了。以我们人眼灵敏度最高的555nm的光来说,其在硅中absorption length大约为1.6um。那么对于3um的epi,85%的光子都能被吸收;对于4um的epi,92%的光子都能被吸收;对于5um的epi,96%的光子都能被吸收。所以你看,在epi厚度大于5um后,意义就不大了。当然对于科学级应用来说,我们希望QE越大越好,比如对于800nm的光,其absorption length大约是12um,所以我们epi能有12um后,就能吸收63%的光子了。再增加厚度还有没有意义呢?其实意义也不大了,因为本身对于长波长的光,absoprtion length就很大,epi厚度要增加非常多才能对QE有一个比较大的提升,这样就会增加成本,另外就是把depletion region深度做到10um以上也是颇有难度的,因此将epi厚度增加到10um以上,对QE帮助不大,但会增加像素间的crosstalk,这样就划不来了。

对于dark current,我想再补充一点儿以此让大家明白这个指标的重要性。相信熟悉电路的大家都知道,一般对于nA级别以下的漏电流来说,我们一般就不怎么关心了,因为可控的ON电流大多情况下也到uA级别了。而对于我们的像素来说,如果他的漏电流能到fA级别,我们的像素都废掉了。1fA啥意思?1fA~6000e-/s,我们整个PPD可能也只能存10ke-,如果曝光1秒钟,这还没光照呢,我们整个PPD就快满了,那还感个啥光呢。。。另外我们知道对于流过二极管的电流,他会产生shot noise,这对于dark current也是一样的,因为原理是差不多的,很大一部分都是由于热导致的,所以如果我们有100e-的dark current流过了,这里就会有10e-的dark current shot noise,那么我们想要的single-photon imaging就不可能了。像一些科学级应用,比如说天文台吧,我们常常需要曝光高达几分钟,甚至几小时,那怎么办呢?最常用也最有效的方法就是降温。通常来说,dark current每降低5~10度会降低一倍。假如我们的像素在20C时dark current有30e-/s,那么如果我们能将温度降到 -30C,dark current的doubling temperature有5C的话,那么他就能降到0.03e-/s,这样即使曝光时间长达1小时,也只有100e-的暗电流流过了。当然真实情况不会像我说的这么理想,在温度降到一定程度,降低dark current 的有效程度就越来越低了,另外温度越低,降温也越困难,需要的功耗也越大,而且其他的电学性能也会受到影响,所以一般最低也就做到 -40~-50C。为了降低dark current,我们在layout上也要注意,首先就是在STI附近,要用P+层将其包起来(所谓的passivation),不让他和PPD接触,我们都知道SiO2和Si接触,就会产生表面态,而这也是产生dark current的源头之一;另外,在画PPD的active层时,不要出现90度角,尽量用45度角,因为使用45度角生产出来的PPD的边界也就越圆滑,STI造成的machnical stress也就越低,这样dark current自然也就越低。

再讲一个关于像素比较general的一个知识,就是像素中我们是不做silicide的!大家都知道,我们做silicide的主要目的就是降低金属和硅的接触电阻以及增强可靠性。但是silicide最大的问题就是他是金属和硅的化合物,他是不透光的!如果我们是个前照的sensor,那整个PPD就被silicide给遮住了,那还整个啥啊;如果是背照呢?也是有一定问题的。因为silicide还是有可能会引入金属杂质,silicide和硅接触的地方也会产生表面态,这些都是增加dark current的源头;另外对于前照我们都不用silicide了,使用背照的时候我们也没必要画蛇添足来增加成本。那么不加silicide有没有什么潜在问题呢?有的。大家应该知道金属直接跟硅接触的话,不一定是Ohmic contact,而有可能是Schottky contact,所以对于FD和MOS管需要与金属直接接触的地方,我们一定要保证掺杂浓度还是足够高的,以保证形成欧姆接触,所以这些地方的掺杂也是比较重要的。不加silicide当然会增加一些接触电阻,但其实这个是关系不大的,想想MOS管的沟道电阻一般都在kOhm级别,所以这里增加一些接触电阻关系不大的。

以上这些是对所有的像素设计来说,都比较通用的一些概念。下面我们对3T, 4T, 5T像素分别作出说明。3T像素的剖面图与电路图如下:

观察3T像素电路图,我们可以发现,3T像素是无法实现全局快门的,因为我们是无法关闭PPD的,一旦RST管关断,像素便开始积累光子(如下时序图)。

读取每行像素时,我们先读取FD上的信号电平S,然后给一个RST脉冲,将像素复位,然后立马读取复位电平R,用 R-S 我们即可知道之前我们积累了多少光子。这里首先有个问题,我们能不能只读S,而不读R呢?可以,但很不好。这个主要原因就是:像素间的SF的阈值会有variation,我们用 R-S 的主要目的就是要消掉这个variation。那么我们能不能先把所有像素的R信号读出来并作记录,然后以后所有的图像都只读S,然后再去用之前得到的R减S呢?可以,但不是很好。因为温度一旦变了,Vth就变了,那这种off-chip calibration就不奏效了,但是读取一行像素的时间都在us级别,这么短的时间,温度几乎是不会改变的。

3T像素还有一个问题,就是我们只能先读S,再读R,所以他只是DS(double sampling),而不是CDS(correlated DS),最终读取的信号R-S中就含有因像素复位引入的kTC噪声,我们通常称这个为reset noise。如果vdd电压较低,复位电平可以等于vdd,我们就称为hard reset,此时噪声即为sqrt(kT/C);而如果vdd电压比较高,复位电平就只能到达Vrst-Vth,我们称为soft reset,此时的噪声为sqrt(kT/2C),因为此时相当于电子只能朝一个方向任意流动,所以噪声会减小,但soft reset有个比较大的问题就是他的最终稳定的电压值是与复位之前FD上的电压值和复位时间长短相关了,这里就可能产生image lag的问题,所以后来人们又发明了hard-soft reset,当然还有更复杂的active reset。但这些方法,包括3T像素本身,现在都用的不多了,我们就不再做详细介绍了,大家有个了解就行了。

这里可能有人质疑了,我们其实可以做CDS啊?可以先把R信号用ADC读取出来,然后积分,再将S信号用ADC读取出来,片外再用R-S啊。这样是可以,但是很明显数据量加倍了,然后还有一个问题就是CDS的R,S间隔时间太长(积分时间~ms级),CDS的有效性就会大打折扣了。因为我们使用CDS不光只是因为他可以消除reset noise,还因为这么做可以减小SF管的flicker noise,如果CDS的间隔太长,就不那么有效了。另外间隔时间太长后,SF的Vth也可能因为温度产生变化。

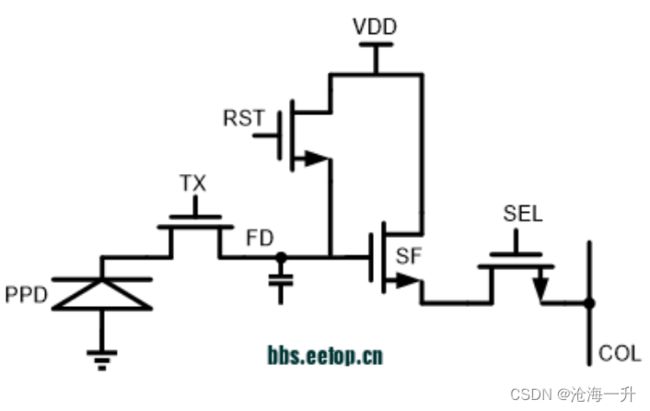

4T像素的电路图如下:

4T像素相对于3T像素最大的优势就是在于他能够做CDS(如下时序图)。在读取每一行像素时,我们先将FD进行复位,然后读取复位电平R,再给入TG脉冲,随后读取信号电平S,即可用 R-S 得到CDS之后的信号。因此,如今的4T像素在RS下是可以做到读出噪声<1e-的!

此外4T像素还能够实现全局快门(如下时序图)。我们可先将所有像素的R电平用ADC读出,接着同时翻转所有像素的TX,再将所有像素的S电平用ADC读出。我们可以看到,这并不是一个很完美的全局快门。首先数据量还是加倍了,另外CDS的间隔时间也较长,FD上的dark current的积累时间大约是总积分时间的一半,所以除非将温度降到很低,这样的全局快门的读出噪声还是会比较高的。我们还可以看到4T全局快门的像素积分时间也是无法小于读取像素两次所需时间的,导致这样的全局快门应用有限。

当然,我们也可以采取类似3T的读取方式以减小数据量(如下图所示),因为加入了TX,还是可以实现全局快门的,但这样便没有了CDS的优势了。

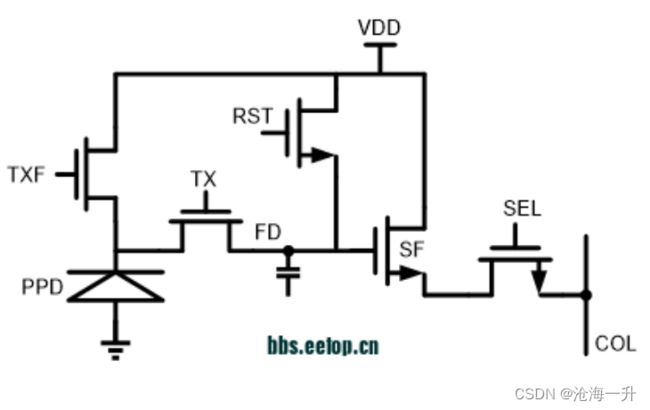

为了解决4T像素只能有较长积分时间的问题,便引入了5T像素,其电路图如下:

他和4T像素唯一的不同便是在PPD上增加了一个transfer gate,可命名为TXF。如下图时序,在读取像素信号的同时,我们可以翻转所有像素的TXF信号,这样像素的积分时间长短便可任意改变了。

此外,我再说一下,设计一个好的4T像素的关键点在哪些地方:

- PPD的pinning voltage选择及版图:有关QE, FW(Full Well) 及 dark current

- TX的版图设计: 有关 dark current 及 Image lag

- FD的掺杂及版图:有关 dark current,noise,conversion gain 及 PRNU

- SF器件选择及版图:有关noise,linearity 及 FPN

我这里只是指出一些需要注意的点,但具体如何做选择及设计,由于涉及的公司机密较多,因此不便给出,望大家见谅!另外,写这个系列的主要目的是想向初学者做一些CIS的基本知识介绍,吸引大家对这个行业感兴趣,加入我们image sensor society这个大家庭:lol 而不是期望大家看完之后就能做出顶尖的设计

最后,我想给一个4T像素版图的简单例子:大家可以结合前面所讲的,想想为什么4T像素的layout是长这样的? 当然,这个例子做的并不完美,也还是有些问题的,这里只是让大家有一个大致的概念。

希望这次讲的能让大家多少有些收获吧! 说实话,讲像素设计蛮难的,就这么5000来字,写到现在我斟酌了已经7,8个小时了,想要让讲解尽量完备,而又不透漏一些设计上的机密,确实很难取舍。相信这里讲的有大家所熟知的,可能也有一些不那么熟知的,总之能让大家有收获就好。