《嵌入式存储器架构、电路与应用》----学习记录(一)

前言

本书系统介绍嵌入式存储器在架构、电路和应用方面的技术进展,包括SRAM、eDRAM、eFlash和近几年兴起的阻变型存储器,并着重介绍我国研究人员在嵌入式存储器方面的研究工作。

第1章 绪论

1.1 什么是嵌入式存储器

存储器(Memory)是现代信息技术中用于保存信息的记忆设备:

- 在数字系统中,能保存二进制数据的器件或电路

- 在集成电路中,没有实物形式的具有存储功能的电路,如RAM、FIFO

- 在系统中,具有实物形式的存储设备,如内存条、TF卡

计算机中的存储器按用途可分为:主存储器(内存)和辅助存储器(外存),也可分为外部存储器和内部存储器。

- 外存:固态硬盘、机械硬盘、光盘,能够长期保存信息

- 内存:主板上的存储部件,用来存放当前正在执行的数据和程序,仅用于暂时存放程序和数据,关闭电源,数据丢失

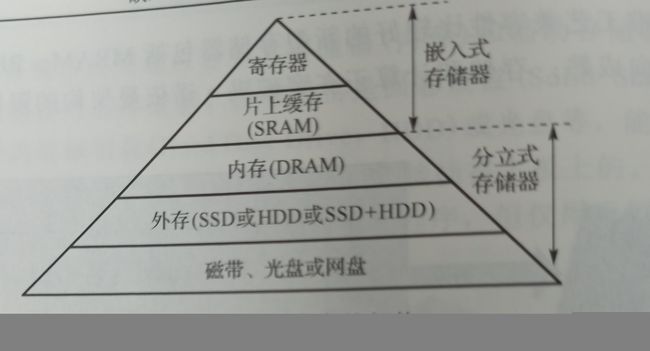

传统冯·诺依曼计算架构中,计算和存储是两个最重要的模块,计算在处理器核(CPU Core)内部,数据存储在片上的嵌入式存储器(Cache)或片外的分立式存储器,如图1-3所示:

- 典型的嵌入式存储器:SRAM、eDRAM和eFlash(e是embedded)

- 典型的片外存储类型:DRAM、Flash、SSD和HDD

1.2 存储器的组织架构

计算设备中的存储系统一般采用层次化的组织架构,如图1-4所示:

第2章 静态随机存储器

2.1 SRAM介绍

静态随机存储器(Static Random Access Memory, SRAM)是最重要的存储器类型之一,在CPU、GPU、NPU、DSP等处理器中用作缓存。

2.1.1 嵌入式SRAM

SRAM占据嵌入式存储系统的主导地位:

- SRAM可以提供最高的数据读、写速度。

- SRAM良好的工艺和工作电压兼容性。

- 在ASIC设计中,SRAM可以做成存储编译器(Memory Compiler)。

2.1.2 低电压SRAM

低压SRAM应用于以下两种芯片:

- 工作频率较低的芯片

- 动态电压频率调整(DVFS)技术

2.2 SRAM组织架构

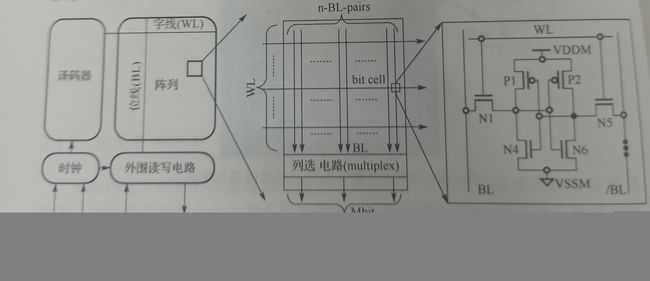

SRAM主要由译码器、存储阵列和外围读写电路组成,如图2-3所示:

其中,存储阵列是SRAM的核心,由存储单元组成的行、列阵列。目前通用的SRAM中,存储单元通常是6管(6T)存储单元。每一行存储单元共享一条字线(Wordline, WL),每一列存储单元共享一条位线(Bitline, BL)。

2.3 6T存储单元

2.3.1 电路结构

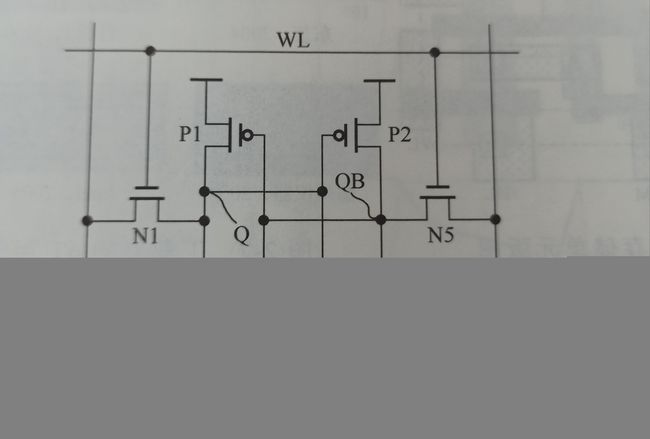

存储单元是SRAM的核心部件,用于存储SRAM写入的数据。如图2-5所示为6T存储单元的电路结构,它的基本存储核心是一对完全对称、首位相连、交叉耦合的反相器,即上拉PMOS管P1和下拉NMOS管N4构成一个反相器,上拉PMOS管P2与下拉NMOS管N6构成另一个反相器,两个反相器交叉耦合形成一个正反馈环,结点Q和QB则是6T存储单元的两个存储结点。正常情况下,两个结点存储的数据是相反的,即结点Q存“0”,则结点QB存“1”。

两个完全对称的传输NMOS管(N1和N5)用于数据的写入和读出。正常情况下,字线WL处于低电平,而两条位线处于高电平,此时,交叉耦合的反相器构成的正反馈系统可以有效地将两个存储结点的数据保持住。

2.3.2 Thin-cell版图

如图2-6为标准6T存储单元的版图:

2.3.3 读操作

- 存储单元处于保持状态时:字线WL被下拉至“0”,而位线BL和/BL则预充至“1”,两个传输NMOS管被切断,数据由两个交叉耦合的反相器进行保持

- SRAM进行读操作时,WL被预充至高电平,两个传输NMOS管处于开启状态,而两条位线则处于悬空状态

如图2-8所示,6T存储单元的读操作电路示意图以及操作波形图。此时,存“0”侧,位线与地之间通过传输NMOS管和下拉NMOS管形成一条低阻通路,产生读电流;而存“1”侧,由于存储结点与位线都是高电平,不存在读电流。

从图中看,存储结点VL存储的数据为“1”,而存储结点VR存储的数据为“0”,位线/BL通过NMOS管PG和PD对地进行放电。当位线/BL的电压被下拉到一定值时,两条位线BL和/BL之间有了一定的电压差,该电压差被灵敏放大电路捕捉,然后进行放大输出,从而完成读操作。

在读操作过程中,由于位线BL与结点VL的电平相等,所以VL数据保持不变。而结点VR与位线/BL之间存在一个大的电压差,使得VR在读操作过程中会抬高一定的电压,该电压是由下拉管PD与传输管PG之间的驱动能力比决定的

- 读失败:若下拉管PD的驱动能力小于传输管PG,则VR的电压值会抬升至一个比较高的电平,抬升的电压值大于反相器的阈值电压时,存“1”侧的下拉管被打开,数据“1”被下拉。由于存储单元正反馈环的存在,读操作的误差电压会被正向放大,导致两个结点存储的数据发生翻转,造成读失败

- 读成功:若下拉管PD的驱动能力大于传输管PG,则VR的电压值只会抬升至一个很低的电平,不足以产生数据翻转,待读操作完成后,存储结点的电平又将回到原来的状态,读成功

2.3.4 写操作

- 存储单元执行写操作时,字线WL开启,相反的数据传输到位线BL和/BL上

- 写入的数据为“0”,则BL下拉到“0”,/BL保持为“1”

- 写入的数据为“1”,则BL保持为“1”,而/BL下拉至“0”

如图2-9所示6T存储单元的写操作电路示意图以及其操作波形图。存储单元执行的是写“0”操作,写操作开始前,VL存储的数据为“1”,而VR存储的数据为“0”。写操作开始后,VL通过传输管对位线放电,而VR则通过传输管充电。此时,数据能否正确写入存储单元是由传输管PG与上拉管PU之间的驱动能力比决定的。

- 写成功:若传输管的驱动能力大于上拉管(PG>PU),由于NMOS管的强传“0”特性,VL结点会被快速下拉至“0”,配合VR预充的高电平和正反馈环,存储单元存储的数据发生翻转。待字线WL关闭后,新写入的数据进入保持状态

- 写失败:若传输管的驱动能力小于上拉管(PG

2.4 外围电路

2.4.1 译码器

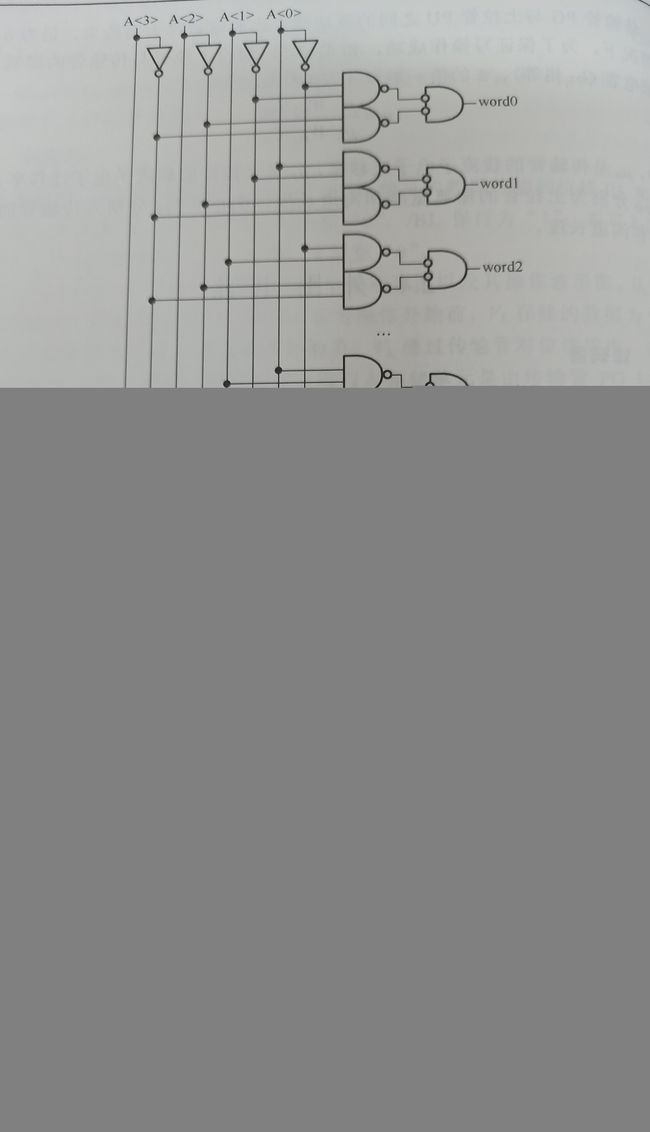

SRAM能随机地根据地址存取数据,就必然有地址译码器。

根据电路结构类型,译码器分为:

- 静态译码器,采用互补的CMOS电路结构

- 动态译码器,采用动态电路结构

在功能作用上译码器分为:

- 行译码器

- 列译码器

如图2-10所示分别为采用一级和二级译码策略的4-16译码电路结构:

如图2-11所示为选择预充的动态n-m译码器,将地址字的最高有效位(MSB)进行预译码,其余位则采用树形结构进行二级译码。

2.4.2 灵敏放大器

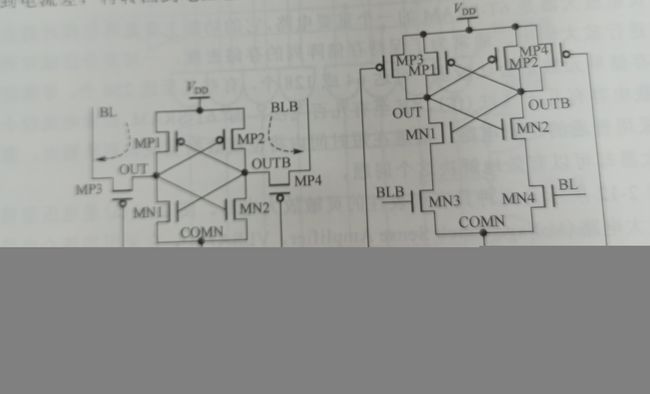

灵敏放大器是6T-SRAM的一个重要电路,功能主要是将位线对的差分数据进行放大输出。如图2-12是两种具有代表性的灵敏放大电路:

电压型锁存灵敏放大电路(VLSA),采用的核心电路和6T存储单元相似,都是交叉耦合反相器构成的正反馈环,灵敏放大器多采用一个尾NMOS管来控制电路的开启和关断。电流型锁存灵敏放大电路(CLSA),与电压型锁存灵敏放大器不同的是采用电流差进行放大输出。

- 电压型锁存灵敏放大电路工作原理:两条位线(BL和BLB)开始阶段都处于浮空的高电平状态,当进行读操作后,其中一条位线存在读电流,使得它的位线电压开始下降,而另一条位线则保持不变,结果在两条位线上建立了电压差,该电压差被PMOS管MP3和MP4传递到了结点OUT和OUTB,当电压差达到一定数值,信号SAE开启(跳变为“1”),灵敏放大器开始工作,将电压差通过正反馈进行放大,实现轨到轨输出。待读操作完成后,SAE关闭(跳变为“0”),结点OUT和OUTB上的数据被传输到输出端口

- 电流型锁存灵敏放大电路工作原理:当位线BL和BLB建立电压差后,信号SAE开启,灵敏放大器开始工作。位线BL与BLB之间的电压差导致NMOS管MN3与MN4的VGS不一样,结果导致通过MN3与MN4的电流不一样,使得电流路径MN1-MN3与电流路径MN2-MN4存在电流差。电流差导致结点OUT和OUTB的放电速度不一样,结果结点OUT和OUTB之间形成了电压差,然后被正反馈环放大,实现差分电压轨到轨的输出

2.5 传统SRAM遇到的挑战

2.5.1 稳定性挑战

静态噪声容限(SNM)是衡量一个存储单元稳定性的重要指标,通常定义为使存储数据发生翻转的最小直流噪声电压。电压传输曲线(VTC)是目前最常用的分析存储单元噪声容限的方法,它是对存储单元中两个反相器进行直流输入扫描,然后将VTC曲线进行叠加,通过图表来分析静态噪声容限。

2.5.2 SARM的最小工作电压

降低电源电压是减少芯片功耗最直接且最为有效的方法,如图2-18是6T-SRAM的存储单元面积和工作电压随工艺发展的变化图。

无论采用何种辅助技术,6T-SRAM的最小工作电压仍徘徊在0.5V~0.7V。

2.5.3 读破坏

传统6T存储单元在读操作过程中,由于存在传输NMOS管与下拉NMOS管的电压分配,“0”存储结点的电压会被上拉,当上拉电压大于另一个反相器的翻转电压时,存储数据便发生了改变,称该情况为读破坏,破坏存储单元稳定的电压称为读破坏电压。

2.5.4 半选择破坏

列选(位交叉)结构是SRAM的存储阵列常用的一种版图排列结构,是将存储阵列通过分成多个小列来实现版图布局,从而提高存储阵列的面积效率。列选结构另一个比较重要的功能:可以结合纠错码(ECC)电路降低SRAM的软错误率(SER)。

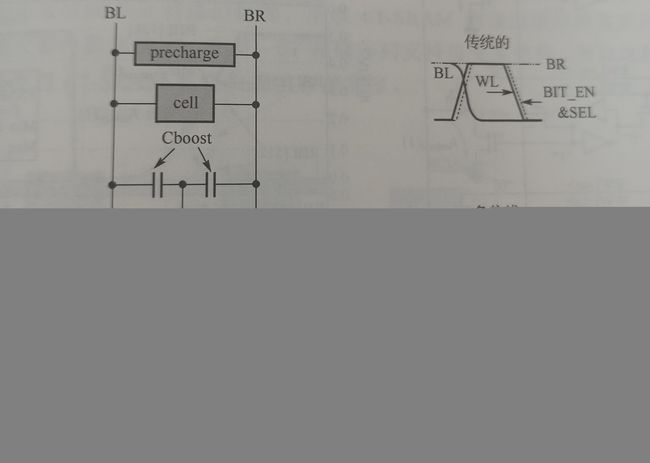

当SRAM采用列选结构时,它不仅可能产生读破坏,而且还可能产生半选择破坏,如图2-20所示:

半选择破坏:SRAM在读/写操作过程,同一字线的存储单元全部打开,选中的单元将数据读出/写入,未选择(半选择)的单元由于位线都预充到高电平,相当于要经历一次读操作过程,在读操作过程中这些半选择单元有可能发生读破坏。

半选择破坏是因为单元之间的列选关系发生的读破坏,它是变相的度破坏,只不过读破坏发生在单元内部,而它却发生在单元之间。

写返回是通过将读出的数据重新写入半选择单元来避免发生半选择破坏,以牺牲SRAM的功耗为代价。

2.5.5 读电流波动

读电流的波动决定了灵敏放大器的放大区间,位线的放电时间具有非常大的波动区间,如图2-21所示:

2.5.6 NBTI和PBTI效应

由栅氧厚度变薄引发的负偏压温度不稳定性NBTI与正偏压温度不稳定性PBTI效应造成器件性能降低或者失效。

- NBTI:在高温下对PMOS管施加负的栅电压而引起的一系列电学参数的退化(一般应力条件为125℃恒温下栅氧电场,源、漏极和衬底接地)

- PBTI:针对NMOS管施加的正栅电压引起的电学参数退化

NBTI效应对器件性能参数的影响有:

- PMOS器件栅电流增大

- 阈值电压负向漂移

- 亚阈值斜率减小

- 跨导和漏电流变小

电路受到NBTI效应的影响:

- 在模拟电路中引起晶体管间失配

- 在数字电路中导致时序漂移、噪声容限缩小,甚至产品失效

2.6 低电压SRAM遇到的挑战

2.6.1 概述

对于速度要求不高而功耗和功耗要求极其严格的芯片,降低电源电压是目前满足其性能要求最直接且有效的方法。随着工作电压的降低,其他问题随之而来:

- 电路静态噪声容限越来越小

- 器件驱动电流变小

- 对工艺偏差越来越敏感

- 晶体管的开关电流比越来越小

这些因素使得低电压电路鲁棒性变差,抗噪声能力越来越弱。

2.6.2 最小功耗和最佳能耗操作

- 功耗由动态功耗和静态功耗组成,其中静态功耗主要是漏电流功耗。降低电源电压可以以平方关系降低动态功耗,以指数关系降低漏电流功耗。

- 能耗是功耗对时间的积分,由动态能耗和静态能耗组成,静态能耗主要由漏电流能耗构成。

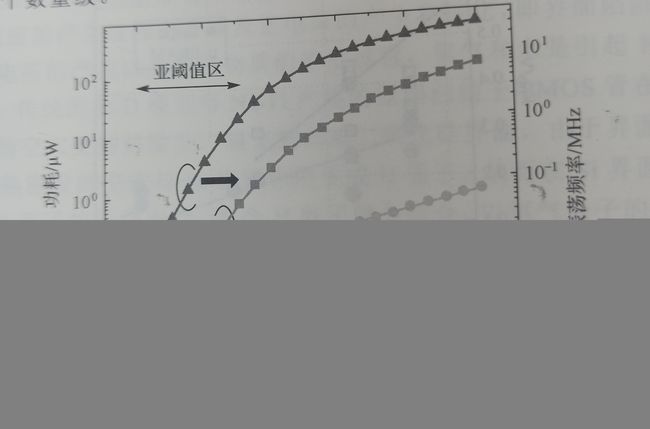

图2-23和图2-24所示为在65nmCMOS工艺下,电路功耗与能耗随电源电压变化的曲线。随着电源电压的降低,电路的频率逐渐降低,同时电路的功耗也逐渐降低,电压降低至亚阈值电压区域后,漏电流功耗成为电路功耗的主要组成部分。

2.6.3 读电流衰减

存储单元的读电流是位线对地放电过程中,流过传输管PG和下拉管PD的电流。随着电源电压的降低,晶体管门驱动电流越来越小,导致存储单元的读电流也越来越小。图2-25所示是不同电压下读电流因工艺偏差而产生的变化。

2.6.4 开关电流比

随着电源电压的降低,晶体管的驱动电压VGS逐渐减小,当VGS降至小于晶体管的阈值电压时,晶体管从强反型区进入弱反型区。此时,晶体管并未完全关断,处于一种弱开启状态。相比于强反型区的驱动电流,弱反型区的驱动电流要小很多。

2.6.5 位线漏电流

在亚阈值工作区,漏电流功耗是功耗的主要来源。随着电压的降低,MOS管的漏电流是快速降低的,而且工艺越先进,晶体管的漏电流越小。

2.7 新型低电压存储单元

低电压SRAM遇到的挑战意味着传统的6T存储单元已不能满足超低功耗芯片的需求,迫切需要新型存储单元来替代6T存储单元。

2.7.1 5T存储单元

图2-30所示为5T存储单元的电路结构和版图,与传统的6T存储单元相比,它右边的反相器少了一个下拉NMOS管,并且读、写字线是分开的。5T存储单元同样采用差分位线的方式将数据写入,但是,数据的读出却通过M0、M4单端进行。

设计巧妙点:巧妙方法消除存储单元的读破坏,当存储单元进行读操作时,存储结点Q的电压有可能抬升。但是,由于右边反相器缺少下拉NMOS管,所以,即使Q点的电压抬升了,也无法影响到另一存储结点QB的值。

致命缺点:当存储结点QB的值为0时,缺少下拉NMOS管使得结点QB长期处于浮空状态,只能完全靠通过M1的漏电流进行数据保持,这导致整个存储单元的数据保持能力非常差。

2.7.2 单端6T存储单元

图2-31所示是一个单端6T存储单元的电路结构,只有一条位线,完全通过一个传输门进行数据的写入与读出。由于采用单位线写入方式,需要左边反相器采用虚拟电源、地辅助进行写操作。

2.7.3 单端7T存储单元

图2-32所示为一个单端7T存储单元的电路结构,将一个NMOS插入到左边的反相器中,并通过关断这个NMOS管来切断正反馈环。当存储单元进行读操作时,字线WL开启,数据通过传输管M1和下拉管M5单端读出到位线BL上,此时,由于WL_为“0”,所以晶体管M6是关断的,导致存储单元的正反馈被切断,结点Q与结点QB是隔离的,从而避免存储单元产生读破坏。但是,在关断M6管期间,存储结点Q处于浮空状态,易受到来自PMOS管M2亚阈值电流的影响。

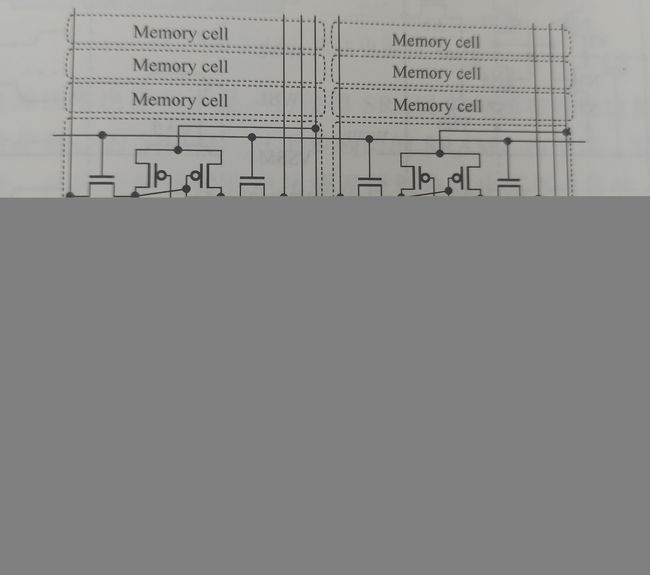

2.7.4 8T存储单元

8T存储单元的电路结构和版图如图2-34和2-35所示,电路结构简单,在6T存储单元的基础上增加了两个堆叠NMOS管,同时增加一条读字线与一条读位线。

![]()

图片来源于《嵌入式存储器架构、电路与应用》

写操作:8T结构的写操作与6T结构一样,当写字线WWL上升时(此时读字线RWL为0),存储单元开始进行写操作,通过保持写位线WBL、WBLB的预充高电平或强制将写位线的电压下拉至低电平,来进行写“1”或写“0”的操作

读操作:8T结构的读操作通过两个堆叠N管M6、M7来实现。读操作前,读位线预充至高电平,当读字线RWL上升时(此时写字线WWL为0),存储单元开始进行读操作,M7管打开,若存储结点Q存储的数据值为0,QB点存储的数据值为1,那M6打开,读位线RBL通过M6、M7放电,将数据“0”读出。若存储结点Q存储的数据值为1,QB点存储的数据值为0,则M6关断,RBL保持之前预充的高电平,从而将数据“1”读出

8T存储结构特点:

- 数据输出为全摆幅电压输出

- 消除读破坏

- 减小位线漏电流

- 晶体管尺寸可以等比例缩小

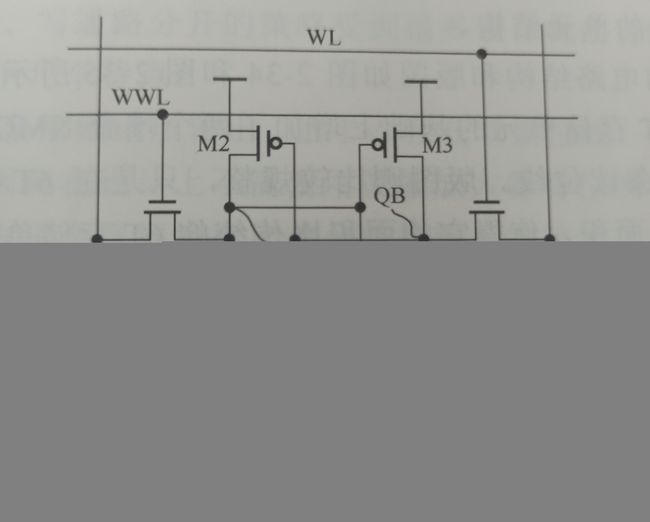

2.7.5 9T存储单元

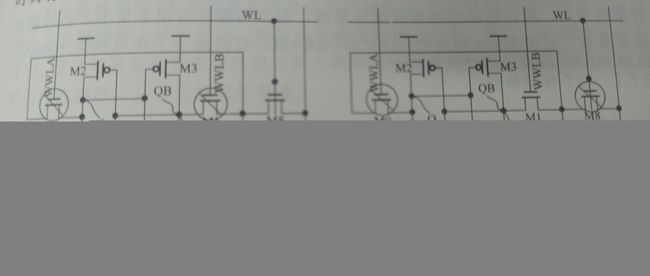

9T存储单元不仅消除了读破坏,而且还支持列选结构。图2-39所示为支持位交叉结构的9T存储单元。它的主体部分采用传统的6T存储单元,只不过传输管M0、M1分别由列字线WWLA与WWLB控制。读出电路则是由M6-M8组成的读buffer构成。

- 读操作:WL为高,M7、M8开启,数据通过M6-M8传输到位线RBL上。由于此时两条列字线处于关闭状态,所以存储结点与位线是隔离的,即不存在读破坏的情况

- 写操作:WL为高,M7、M8开启,位线RBL被下拉至0。若执行写“0”操作,则列字线WWLA开启,WWLB关断,结点Q被M0和M8下拉至“0”,结点QB通过正反馈预充至“1”

图2-40所示是写操作时9T-SRAM的半选择单元情况:

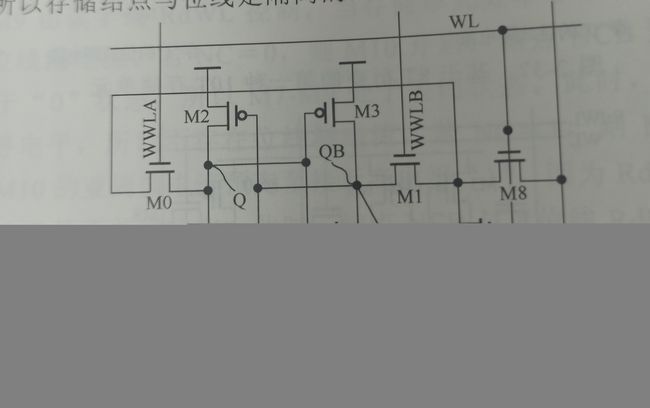

2.7.6 10T存储单元

图2-41所示是10T存储单元的电路结构,它的主体结构也是传统的6T存储单元,但是增加了一对分别由行字线WL控制的传输管M6和M7,以及辅助读操作的下拉管M8和M9

- 读操作:行字线WL开启,列字线WWL关闭,数据通过M6和M8,以及M7和M9组成的差分路径读取到互补的位线对上。由于此时M0和M1处于关闭状态,所以不存在读破坏现象

- 写操作:行字线WL和列字线WWL都开启,数据通过M6和M0,以及M7和M1组成的差分路径写入到存储结点上。此时,对于同一行上的半选择单元,由于列字线WWL为低,所以不存在半选择破坏;对于同一列上的半选择单元,由于行字线WL为低,所以也不存在半选择破坏

2.7.7 12T存储单元

图2-42所示为差分12T存储单元的电路结构,相比于差分10T存储单元,它在存储单元的两条上拉路径中插入了两个PMOS写辅助管M10和M11,并且这两个写辅助管的栅分别由列字线WWLA和WWLB控制

存储单元执行写“0”操作时,字线RWL和WWLA为高,位线BL为低。此时,PMOS管M10处于关闭状态,结点Q的上拉路径被切断,所以结点Q被M0和M6快速下拉至“0”,结点QB被正反馈预充至“1”。同理,当存储单元执行写“1”操作时,字线RWL和WWLA为高,位线BLB为低。此时,PMOS管M11处于关闭状态,结点QB的上拉路径被切断,所以结点QB被M1和M7快速下拉至“0”,结点Q被正反馈预充至“1”。这种切断上拉路径的写辅助技术有效地提高了存储单元的写容限和写速度

2.8 外围辅助电路技术

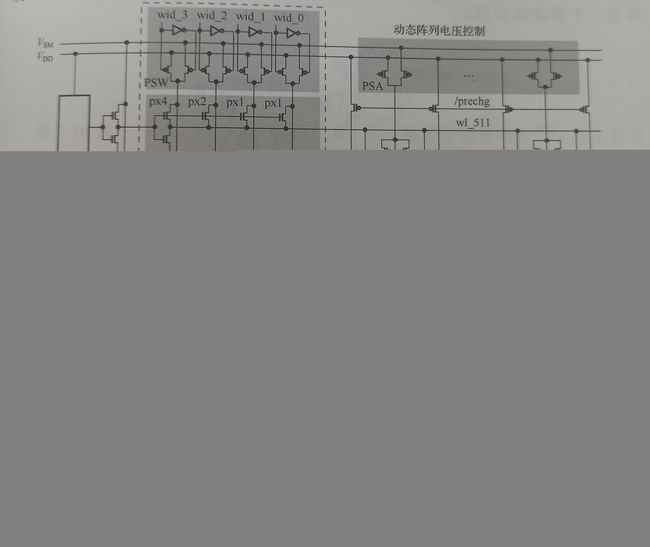

2.8.1 存储阵列电源技术

存储阵列电源技术是通过外围辅助电路将存储阵列的电源电压抬升或下降一定值,从而提高存储单元读、写操作的稳定性。图2-43所示是东芝公司采用的一种存储阵列电源技术:

存储阵列电源技术的另一个形式就是可变阱电压技术,图2-44所示是一种可变阱电压技术和时序波形:

2.8.2 地电平抬升技术

地电平抬升技术是将存储阵列的地电平电压抬高,主要是用于提高存储单元的写噪声容限和降低存储阵列的漏电流功耗。图2-45所示是一种比较常用的地电平抬升技术:

图片来源于《嵌入式存储器架构、电路与应用》

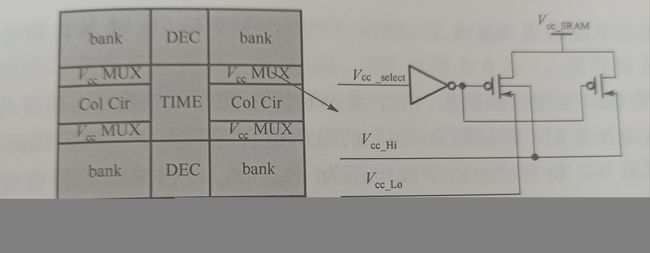

2.8.3 双轨电源技术

双轨电源技术是根据单元的操作类型来动态调节电源电压,从而保证存储单元的读、写稳定性。图2-47所描述的是基于列选控制的双轨电源技术:

2.8.4 动态字线电压技术

动态字线电压是针对6T存储单元提出的,6T存储单元在读操作时容易发生读破坏,影响存储单元的稳定性,而动态字线电压方法却能很好地提升6T单元的读噪声容限。如图2-48所示为动态字线电压产生电路,此电路存在两种工作模式:低摆幅电压输出模式和全摆幅电压输出模式:

2.8.5 负位线电压技术

对于6T存储单元,增强传输NMOS管或是减弱上拉PMOS管可以提高写操作的稳定性。负位线电压策略是在存储单元写操作时给位线一个负电压来加强传输管的驱动能力,从而提高存储单元的写操作稳定性,而且不会影响单元的读操作能力。图2-50所示为一个负位线电压产生电路:

2.8.6 脚踏管技术

脚踏管技术是为了解决单端8T存储单元的位线电流问题而提出的,如图2-52所示,8T存储单元读端口的地接到一个脚踏管输出上。当存储单元处于非读状态时,脚踏管输出为高,完全抑制位线的漏电流。当存储单元进行读操作时,脚踏管输出被拉低,为操作提供读电流

2.8.7 单端灵敏放大电路

针对8T-SRAM提出一种单端的灵敏放大电路,可以有效地增加8T-SRAM的存储密度。图2-54所示是它的电路图和波形图,局部位线(LBL)上一个挂载了256个存储单元。

2.8.8 基准差分灵敏放大器

图2-55为SRAM的阵列布局和基于基准的差分灵敏放大器的电路结构。它也是针对单端8T-SRAM提出的,SRAM的单条位线分割成了4列,每条子位线(RBL)挂载256个存储单元,所有列的读位线通过一级选择电路后,与差分灵敏放大器的一个输入端相连。

灵敏放大电路由两部分构成:基准电压产生器和差分灵敏放大器。

2.9 SRAM技术的其他应用

2.9.1 视频图像处理SRAM

低功耗10T-SRAM的存储单元结构如图2-57所示,结构与8T很相似,只是右边的读出结构由一个反相器与一级传输门构成,其写操作与6T存储单元一样,采用差分的方式写入。

2.9.2 寄存器文件

图2-59所示是一个5W9R(5写9读)的寄存器文件存储阵列结构,采用的是5W9R的存储单元,读端口采用单端8T一样的读buffer,每个读端口有1条字线和1条位线;写端口却采用传输门的写操作方式,每个字端口只有1条字线和1条位线。

2.9.3 PUF技术

物理不可克隆技术(PUF)利用了芯片制造过程中离子注入、抛光和刻蚀等工序的随机工艺偏差,产生芯片的唯一“指纹”信息,经特殊技术提取后,可作为芯片的唯一标识信息。

2.9.4 抗辐射加固SRAM

随着工艺技术的进步和电源电压的降低,电路的结点电容越来越小,抗噪声能力也越来越弱,使得纳米级集成电路很容易受到单粒子瞬态(SET)事件的干扰。图2-61所示描述了一对交叉耦合反相器中SET事件的发生。

致谢《嵌入式存储器架构、电路与应用》

![]()

希望本文对大家有帮助,上文若有不妥之处,欢迎指正

分享决定高度,学习拉开差距