基于STM32 ARM+FPGA的电能质量分析仪方案(一)硬件设计

本章主要给出了本系统的设计目标和硬件设计方案,后面详细介绍了硬件电路的设计

过程,包括数据采集板、 FPGA+ARM 控制板。

3.1系统设计目标

本系统的主要目的是实现电能质量指标的高精度测量和数据分析,其具体技术指标如

下所示:

1.电能质量指标测量精度:

(1) 电压: ±0.3% 额定电压;

(2) 电流: ±0.5% ;

(3) 频率: ±0.01 Hz ;

(4) 三相不平衡度: ±0.2% ;

(5) 谐波分析: 1-17 。

2.能够实时显示电能质量指标和三相电压电流的波形,实现数据共享和良好的人机交

互。

3.能够对电网运行数据进行存储。

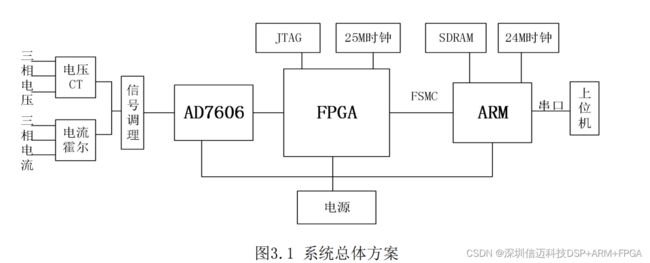

3.2系统总体方案

测量系统中控制电路的结构各式各样,有单独的 FPGA 、 ARM 、 DSP 芯片的控制电

路,还有基于 FPGA+ARM 、 DSP+FPGA 、 DSP+ARM+FPGA 等多架构控制电路,本设计选

用 FPGA+ARM 的双处理器模式作为控制电路, FPGA 的 I/O 口数量多,接收和处理数据的速

度快,具有较强的最短窄脉冲捕获能力,抗干扰能力强,保证了数据采集过程的准确性和

连续性, FPGA 还具有硬件乘法器,数据处理方式是并行的,为后续 FFT 算法中涉及的大量

的乘积累加和的运算提供保障。 ARM 是一款常用处理器,具有高性能、低功耗等特点,集

成库函数较多,开发方便,而且外设众多,为后面系统功能的扩展提供足够的空间。系统

硬件框图如图 3.1 所示。

由上图可知,硬件电路主要包括数据采集部分、 FPGA+ARM 控制部分、上位机部分。

数据采集板的设计包括电源电路、前端的电压电流互感电路电路、电压跟随电路、基于

AD7606 的模数转换电路; FPGA+ARM 控制部分主要包括 FPGA 和 ARM 的供电电源电路、

下载电路、串口电路、时钟电路等;上位机显示模块是用 C# 编写的上位机软件。系统的具

体工作过程为:首先将电网三相大电压、电流信号通过电压、电流互感器以及运放构成的

电压跟随电路,把信号调整至 A/D 的输入范围,再由 FPGA 控制模数转换器实现 6 通道信号

的高速同步采样,在 FPGA 内部完成三相锁相环和 FFT 计算模块的设计,并利用 SDRAM 对历

史数据进行存储, FPGA 和 ARM 通过 FSMC 进行通信;在 ARM 处理器中移植嵌入式实时操

作系统 FreeRTOS ,完成 FPGA 和 ARM 之间数据的读取和写入、 ARM 和上位机之间的串口通

信、以及经浮点运算后得出电能质量的各项参数等线程任务,最后通过在上位机软件中实

时显示和分析各项电能质量指标。

3.3 数据采集模块

3. 3 . 1采样过程

数据采集作为系统的前端电路,直接影响电参数的测量精度、实时显示速度。近年来

数字化采样在电气测量领域得到了广泛的应用,信号采集分为直流采样和交流采样两种:

(

1)直流采样是利用变压器或互感器将交流电压或电流信号的幅值降低,通过整流电

路转化成直流信号再进行采集。缺点主要有: R-C 滤波回路的时间常数很大,影响实时

性;在测量含有谐波或噪声的信号时具有较大的误差;变送器设备复杂且后期不便于维

护。

(

2)交流采样 [33] 的基本原理是利用电压、电流互感器将被测的交流电压和电流信号进

行隔离、滤波、移相、放大后,利用微处理器对其连续瞬时值进行采样得到离散的时域采

样序列,再通过一些算法对采样值序列进行数值处理以计算出被测量,交流采样省去了复

杂的整流电路,只需简单的滤波和幅值放大衰减的调理电路。由于交流采样对象是信号的

瞬时值,因此其实时性好且相位的失真较小,近年来电子技术飞速发展, DSP 和高速 A/D

转换芯片为交流采样提供了硬件支持,交流采样正在逐步替代直流采样,成为电气测量领

域的主流采样方式。

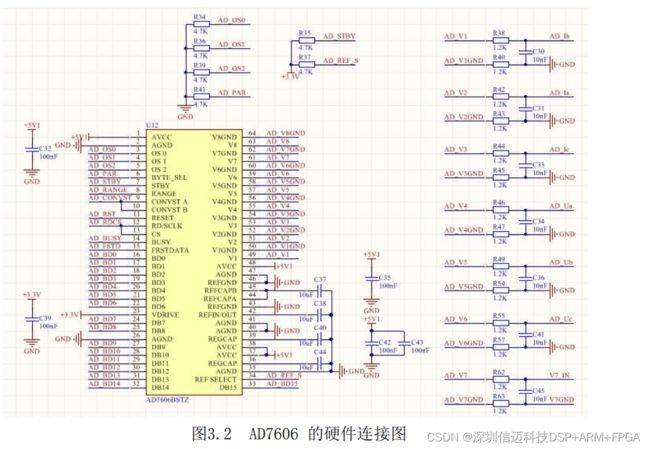

3. 3 . 2 AD7606模数转换电路

AD 转换器是整个采集板的核心,其转换速度、分辨率等性能指标的优劣直接影响

最终的测量结果 [34] 。市面上 AD 转换器的种类繁多,不同公司不同系列产品之间性能也

是千差万别。要想对数据进行高精度采集,高精度的模数转换器是必不可少的。

根据通道数量、采样率和同步采样等设计要求,本设计选用 Analog Devices (ADI) 公

司的 8 通道 16 位 AD7606 同步采样芯片,是电力线路测量系统中常用采样芯片之一,采样速

率高达 200kSPS ,支持 ±5 V 、 ±10 V 双极性信号输入,采用 5 V 单模拟电源供电,内部集成了 2.5

V 基准电压源,提供了过采样和数字滤波功能,数字输出方式根据需要设置为并行输出或串

行 输 出 。 传 统 的 逐 次 逼 近 (SAR)ADC 在 输 入 前 端 都 要 加 一 级 运 算 放 大 器 (Operation

Amplifier) ,才能驱动内置采样电容实现采样,而 AD7606 集成了低噪声、高输入阻抗的信

号调理电路,其具有 1 M 模拟输入阻抗的输入缓冲器,因此, AD7606 不需要外部驱动电路

和滤波电路,大大简化了前端设计。 AD7606 的硬件连接图如图 3.2 所示。

3.4 FPGA+ARM控制模块

3.4.1 FPGA的选型

FPGA(Field-programmable Gate Array) ,即现场可编程门阵列,是在可编程器件 PAL 、

GAL 、 CPLD 等的基础上发展而来的,它是专用集成电路( ASIC )中的一种半定制电路

[36] ,具有静态可重复编写的功能,用户可以通过软件编程重新配置内部的逻辑模块和 I/O

口,达到改变硬件功能的目的,这样就克服了定制电路不灵活性的缺点,集成度得到了很

大的提升,其特有的并行处理方式极大提高了数据运算速度。近年来微处理器发展迅速,

集成度越来越高,仅用一块 FPGA 芯片及其供电电路、配置电路和时钟电路即可组成数字电

路,外围电路大大减少。由于 FPGA 处理器丰富的可编程资源、并行的数据方式、灵活性强

等优点,使其在实时信号处理、数据传输等领域得到了广泛的应用。目前市场上 FPGA 的

主要厂商有 Xilinx 、 Altera 以及 Actel 等,选择芯片时要根据设计需要的逻辑资源、RAM、工

作频率、速度等级以及管脚数目等,逻辑单元数 (LEs) 、内部集成存储器、硬件乘法器也是

重要选型指标,逻辑单元的数量决定集成度的高低。本设计最终选用 Altera 公司的 Cyclone

Ⅳ系列 EP4CE10F17C8N ,其集成了 256 个可用引脚, 23 个乘法器, 10320 个可编程逻辑

单元,高达 105 个高性能扩展 I/O 口,高达 50M 的有源晶振,能够倍频出多种不同频率的时

钟,完全能够满足该系统的设计需求。

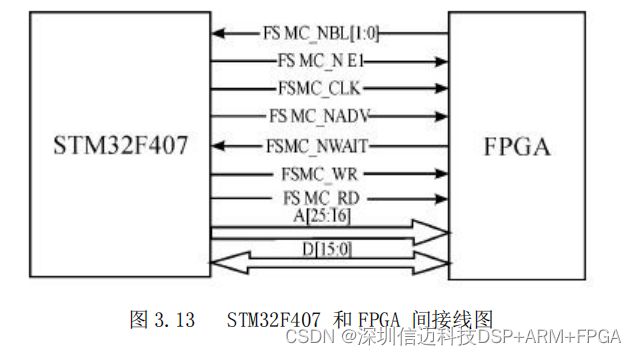

3.4.9 FSMC接口

FSMC(Flexible Static Memory Controller) 可变静态存储控制器,是 STM32 系列处理器

自带的通信总线, STM32 通过 FSMC 对外部存储器进行直接读写,能够支持多种类型静态存

储器的扩展 [44] ,本设计中将数据线 D [ 15:0 ]、地址线 A [

25:16 ]以及其他控制引脚连接

到 FPGA 的 I/O 端口,将 FPGA 看作 STM32F407 的外部 SRAM , STM32 通过存储器读

写指令对 FPGA 进行操作,通过扩展出的控制/数据/地址三种总线来完成控制操作。 FSMC

的映射地址空间被划分为 4 个组 (Bank) ,用于连接外部存储器,每个 Bank 有独立的片选信号

和独立的时序配置, FSMC_NE1 为第一组第一区的片选信号,读写信号接口分别为

FSMC_WR 和 FSMC_RD ,根据设计的数据要求,设计数据位宽 16 位,地址位宽 10

位,接线图如图 3.13 所示。