HDLBits自学笔记2:Verilog language.Vector

Vectors

建立一个电路,有一个3bit输入,输出这个向量,并将其分割为三个单独的1bit信号输出,电路图如下:

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 );

assign outv = vec;

assign {o2, o1, o0} = vec;

endmodule

Vectors in more detail

建立一个组合电路将16bit输入分为高字节和低字节

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign {out_hi, out_lo} = in;

endmodule

Vector part select

一个32bit的向量可以看做4字节,建立一个电路将32bit输入的字节顺序翻转输出,如下:

AaaaaaaaBbbbbbbbCcccccccDddddddd => DdddddddCcccccccBbbbbbbbAaaaaaaa

该操作常用于大小端转换

module top_module(

input [31:0] in,

output [31:0] out );

assign out = {in[7:0], in[15:8], in[23:16], in[31:24]};

endmodule

Bitwise operators

建立一个电路,有两个3bit输入,计算二者的位或、逻辑或、取非,将b取非后放入out_not高位,将a取非后放入out_not低位

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a | b;

assign out_or_logical = a || b;

assign out_not = ~{b, a};

endmodule

Four-input gates

建立一个组合电路,有4个输入:in[3:0],有3个输出:

out_and: 四输入与门out_or:四输入或门out_xor:四输入异或门

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = ∈

assign out_or = |in;

assign out_xor = ^in;

endmodule

Vector concatenation

输入6个5bit向量,一共30bit,将它们拼接在一起,低位补1,凑齐32bit,再输出给4个8bit向量

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );

assign {w, x, y, z} = {a, b, c, d, e, f, 2'b11};

endmodule

Vector reversal 1

输入8bit向量,将其翻转输出

module top_module(

input [7:0] in,

output [7:0] out

);

/*

// 方法1:位拼接,只适用于位宽较小情况

// assign {out[0],out[1],out[2],out[3],out[4],out[5],out[6],out[7]} = in;

// assign out = {in[0], in[1], in[2], in[3], in[4], in[5], in[6], in[7]};

// 方法2:for

integer i;

always @(*) begin

for (i=0; i<8; i++)

out[i] = in[7-i];

end

*/

// 方法3:generate-for, 要求for循环的begin-end有命名,此处为reversal

generate

genvar i;

for(i = 0; i < 8; i = i + 1) begin:reversal

assign out[i] = in[7-i];

end

endgenerate

endmodule

Replication operator

复制运算符常用于将小位宽的有符号数进行符号位扩展,建立一个电路将8bit有符号数进行符号位扩展

module top_module (

input [7:0] in,

output [31:0] out );

assign out = {{24{in[7]}},in};

endmodule

More repication

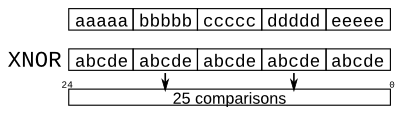

输入5个1bit信号a, b, c, d, e,根据下图计算25bit输出

module top_module (

input a, b, c, d, e,

output [24:0] out );

assign out = {{5{a}}, {5{b}}, {5{c}}, {5{d}}, {5{e}}} ~^ {5{a, b, c, d, e}};

endmodule