ICC 图文学习——LAB2:Design Planning 设计规划

这一步也可以叫floorplan(布局规划),对设计进行布局规划。floorplan的合理性直接关系到芯片的时序收敛、布线畅通、电源稳定以及良品率等。这部分内容非常重要,只有这一步做好了,后面成功率就高。

floorplan阶段主要内容包括:

· 确定芯片的尺寸,core的面积

· 确定IO单元、corner pad和filler的位置

· 宏单元的位置和blockage的规划

· 电源地网络的分布

LAB2:Design Planning 设计规划

- 1. 加载设计

- 2. 读入IO约束文件

- 3. 创建布局规划

- 4. 插入Pad filler

- 5. 电源地逻辑连线

- 6. 创建Pad电源环

- 7. 摆放宏单元

- 8. 虚拟平面布局

- 9. 创建电源地网络

- 10. 时序分析

- 11. 移除std cell,写出def文件

相关文件的准备:

orca_lib.mw/CEL:

orca_setup: 上一步 “ 数据设置 ” 后的ORCA设计,以Milkway格式保存。

design_data/ : 包含设计数据

ORCA_2.v 第二次通过的verilog网表

ORCA_2.sdc 第二次通过的sdc时序约束文件

scripts/: 包含各种布局规划脚本

2ns_pass_setup.tcl 执行第二遍数据设置的脚本

connect_pg.tcl 将所有P / G引脚逻辑连接到网络

insert_pad_filler.tcl 插入pad填充单元

keepout.tcl 对所有宏单元的位置隔离

macro_place_cons.tcl 宏位置约束

macro_pg_rings.tcl 创建宏组周的P/G ring

opt_ctrl.tcl 时序和优化控制

pad_cell_cons.tcl 定义pad单元位置

pns.tcl 电源网络约束/综合

preplace_macros.tcl 将三个宏单元连接到IO pad上

注:若遇到问题或卡住了,调用完整的脚本命令去恢复: .solution/run.tcl

1. 加载设计

- 启动ICC GUI模式

cd lab2_dp

icc_shell -gui

- 打开 orca_lib.mw 设计库中的 orca_setup 单元(该单元已经通过 " data setup " 阶段了),如下图:

由上图可以看到,Layout窗口中的所有宏单元、IO以及标准单元都叠放在坐标原点上。 - 执行时序和优化脚本文件

source scripts/opt_ctrl.tcl

2. 读入IO约束文件

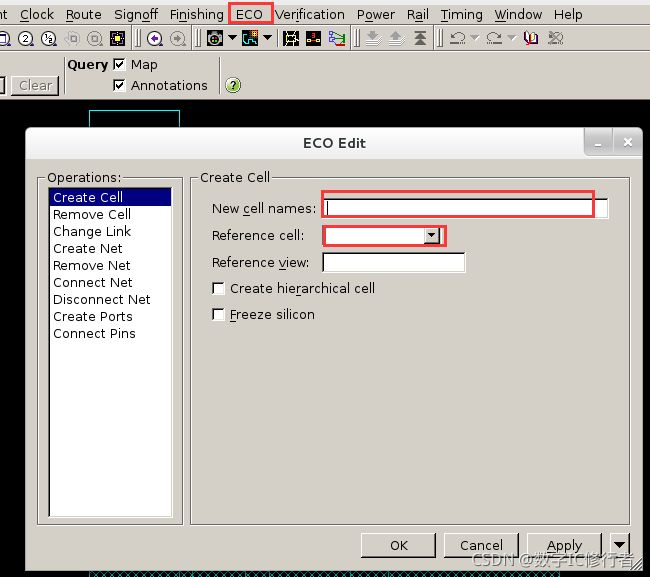

- 创建physical noly cells(该lab可以忽略)

physical noly cells是指那些在网表中没有,但在芯片中又实际需要的一些单元,如IO corner、PG IO等。

在Layout 窗口的菜单栏中依次选择 " ECO" —" Create Cell "。即在弹出窗口中依次填入名字。(此次以IO corner举例)

注: a. IO corner是连接芯片拐角处两边的IO pad,连接衬底及衬底以上各个层,使得IO apd内部的电路形成一个电源地的供电环路。

b. IO corner不是必须的,当芯片只有一边或对边有IO时,为了节省面积,不需要IO corner;对于相邻边含IO时,一般会在拐角加上IO pad。如下图:

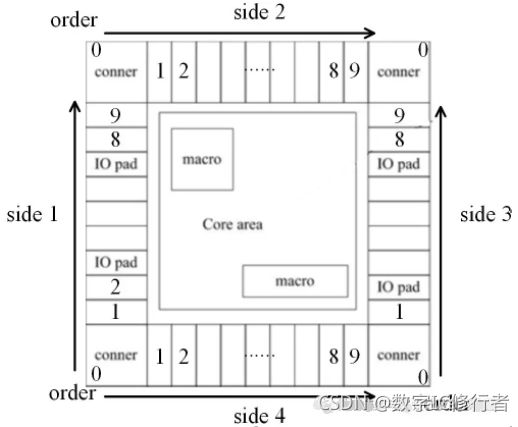

- 一般情况下,chip-level的芯片由core are和pad area两部分组成,core区域主要摆放std cells、macro。而IO约束文件指定了每个IO在整个芯片的位置和排列顺序,(如下图)。(如下图)

注: a. IO约束文件是需要自己手工编写的,所以在IO数目很多的情况下,比较容易出错。

b. 图中side指定了IO pad摆放在哪条边,其中从左边开始,顺时针方向依次为1、2、3和4;order指定IO pad的排列时序,从数字1开始,越大越往上或右摆放。 - 本lab提供的脚本文件已经完成了上面两个步骤,如下:

source -eco scripts/pad_cell_cons.tcl

查看日志文件(.log)输出为 " 1 ",表示这些单元已创建且被约束。

3. 创建布局规划

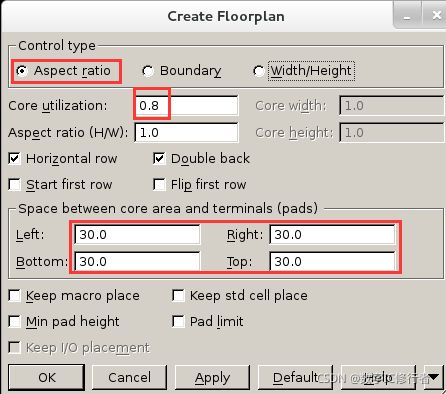

- 在Layout窗口的菜单栏中依次选择 “Floorplan”—“Create Floorplan”(2013前的ICC版本是initial_floorplan),弹出对话框如下:

- ICC工具有3种布局规划控制方案,如下:

a. Aspect ratio:指定芯片高宽比值及Core的利用率,当设计中不含macro时多用这种方案。

b. Width/Height:指定core具体的高度和宽度,一般含macro的设计,常用这种方案。

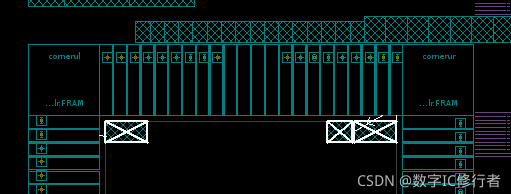

c. 指定core area和pad area之间的间隔。 - 将core utilization改为0.8,core到pad的间距均设为30,点击Ok,IO单元都已摆放在core四周,四个角落均有corner pad,每边都有4个PG pad如下图。

4. 插入Pad filler

- 加入Pad filler是为了连接两个相邻的IO pad,实现从衬底到各层金属的相连,为IO内部电路形成电源地环路。只有当IO与IO中间存在空隙,才需要插入,否则会出现DRC和LVS问题。

- GUI操作步骤:Finishing—Insert Pad Filler,打开对话框如下:

在序号1中填写Pad filler的cell名字,后面的数字一般表示该filler的宽度,一定要按从小到大的顺序填写。

序号2表示特性情况下需要重叠pad filler才能形成一个电源环,一般宽度小于1微米。 - 本lab提供了的脚本文件可完成上课的操作,source脚本命令如下:

source scripts/insert_pad_filler.tcl

5. 电源地逻辑连线

在电源地和IO pad、macro和标准单元的PG pin间建立逻辑连接(没有物理布线),通过以下脚本来实现:

source -echo scripts/connect_pg.tcl

本设计中有三种不同的电源,分别是VDD、VDDO、VDDQ,后两者用于芯片外围供电。

6. 创建Pad电源环

在插入Pad filler后,已为IO内部电路形成电源环,当不使用填充单元且并非所有pad都紧挨着时,或填充单元没有PG pin时,则需要创建一个pad ring来确保PG 的连续性。

creat_pad_rings

7. 摆放宏单元

Macro摆放相关知识:

对于floorplan来说,人们更倾向于靠自己的经验去摆放Macro,摆放它们时不仅要考虑面积、互连线长等传统问题,还需要考虑Place阶段,Macro的摆放对Place的影响。人们根据生活中的经验,提出一种边缘摆放(edgeplace)的方法。故Macro的摆放原则可以参考下图:

a. 大的Macro尽量贴近版图的边缘和角落摆放。这样有利于空间的利用,尽量留出一个连续且尽量接近圆形或方形的区域来摆放标准单元,保证处于同一高度。

b. Macro尽量摆放在靠近相应(IO pad)的位置。因为对于对于大型的Macro。它们不仅需要与芯片内部的其他Macro或者标准单元进行数据交换,还需要与芯片外部的器件进行通信。这种数据交换是靠IO pad进行的,因此摆放在离相应的数据端口附近,有利于减小互联线长度,减少线延迟,并节约布线资源。

c. Macro之间要有一定的空隙,给予布线资源。特别是在Macro的间隙有端口的时候更加如此。设计者可以根据相邻Macro边界上端口的多少来决定留有多大的空隙比较合适,这样才不至于出现Pin Access的问题。可以给Macro加上keepout margin来控制Macro之间的距离。

d. 合理设置Macro摆放的角度。要根据端口的连接关系与互联模块的位置来决定。

以上是关于macro摆放的知识总结,现在回到我们lab中进行实操,加深理解。

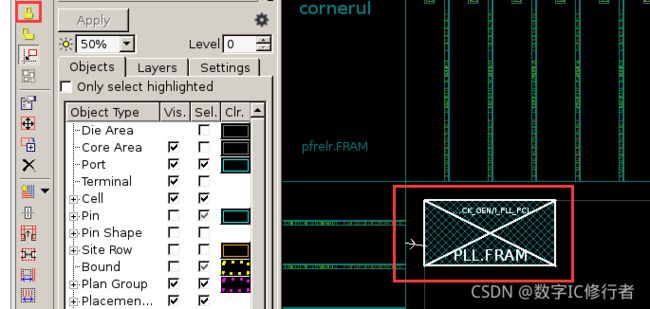

- 依次选择Layout窗口中的 "Select "— "Cells "— "by types ",然后选择对话框中的Macro,再点击左下角的 "Select All "按钮,最后点击OK,所有的Macro都高亮显示(白色),如下图。

- 从Layout窗口工具栏中选择 " Flylines " 图标,并从右侧出现的 " Show flylines " 面板中,点击倒三角形并选择 "Selected to IO " ,再点击 " apply "按钮,最后将亮度调到50%甚至更低,以便更好地看到三条飞线。

- 保持" Show flylines " 面板打开。如果需要不小心取消Macro高亮显示,飞线消失了,使用 [Ctrl] 键重新选择之前显示的三个Macro,飞线重新出现。

- 与IO pad直接相连的三个Macro的名字分别为:

a. I_CLOCK_GWN/I_PLL_PCL

b. I_CLOCK_GWN/I_PLL_SD

c. I_CLOCK_GWN/I_CLKMUL

此设计有两个PLL,应分别放在芯片的左上角和右上角,以便靠近各自的时钟pad。 - 手动将I_PLL_PCL宏单元(连接左边的pad)移动到核心区域,可以使用 工具栏上的"撤销(返回图标) "按钮来回操作。

a. 使用 "Selection Tool " (箭头)按钮选择I_PLL_PCL宏单元

b. 选择 " Move/Resize Tool(M) 图标(窗口左侧四个箭头图标)开始移动Macro到core的左上角,与边缘留一点间距。

c. 在I_PLL_PCL宏单元仍被选择的情况下,使用左下角的 "Align Tool " 图标中的 " Align Left " 和 " Align Top " 分别与core的左边缘和上边缘对齐

d. 锁定Macro(单击 " 锁形 " 图标),为了避免单元在布局阶段软件对它进行移动。此时鼠标悬停在单元上,会出现一个 " X "穿过单元,锁定单元,此时单元无法移动。命令如下:

set_dont_touch_placement

6. 重复以上步骤,将其他两个macro移动core内,并靠经各自的IO pad单元。

a. 单击I_PLL_SD,将它拖到core的右上角,且与core的上边缘和右边缘对齐,然后旋转180°,以减少走线长度,最后将其锁住。

b. 单击并拖动I_CLKMUL到I_PLL_SD的左侧,将其与上边缘对齐,然后在 " 旋转 "栏中选择Y -axis沿Y轴镜像,以减少走线长度。

c. 将I_CLKMUL与I_PLL_SD间隔10微米:按住 [Ctrl ] 键,同时选中I_CLKMUL与I_PLL_SD,指定distribute offset(分布偏移)为10,再选中 " Distribute Right " ,最后锁住I_CLKMUL宏单元,如下图:

d. 关闭 "Show flylines " 面板,当选择上面介绍的三个macro时,都会看到被 "X "穿过,剩下的macro接下来的步骤中摆放,如图:

- 为了确保上面三个macro摆放到预期的位置,可以source下面的脚本:

source -echo scripts/preplace_macros.tcl

8. 虚拟平面布局

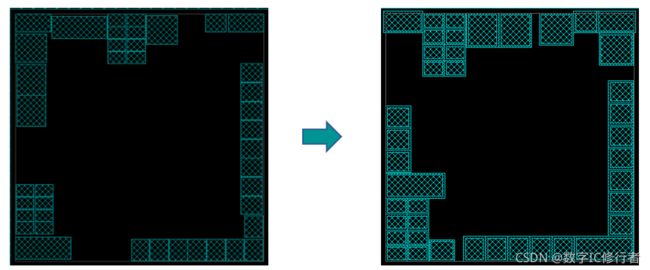

在实际项目中,当摆放好macro后需要在macro周围规划好hard blockage,它会阻止任何cell放置在该区域,同时也会阻止离它很近的地方放置太多的cell,避免产生congestion问题。其中keepout margin作用和hard blockage一样,只是其可以随着macro的移动而移动。

说明:本lab在做虚拟平面布局前,会跳过blockage的规划,查看结果;然后再加上blockage,对结果进行检查,以便观察它们之间的不同。

- 验证当前虚拟平面布局选项是否是默认设置:

report_fp_placement_strategy

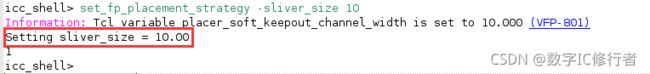

- 将 sliver size设为10微米,以防止标准单元被放置在macro之间的窄通道中:

set_fp_placement_strategy -sliver_size 10

- 使用 " no hierarchy gravity " 选项,来执行时序驱动的虚拟平面放置(以确保逻辑层次不会影响此非层次结构或平面布局的位置)。

create_fp_placement -timing_driven -no_hierarchy_gravity

- 检查全局布线拥塞图

congestion相关知识:

a. 拥塞通常指绕线阻塞,即局部或整体绕线资源不够的现象。其代表GRC(Global Routing Cell)边界上需要的布线资源与可用布线资源的比值,当需要布线资源大于可用布线资源时,就会存在拥塞。ICC再报告拥塞时,默认首先进行全局布线,用全局布线的结果来报告拥塞。

b. floorplan阶段预估的congestion是通过Global Routing来进行判断,仅仅只是虚拟的走线资源判断实际走线资源是否满足,并没有实际进行布线。

c. GRC为正方形,其每条边的尺寸通常为标准单元高度的两倍。它会计算出GRC每条边可用于布线的布线通道(track)的数目(capacity),以及布线需要的布线通道的数目(demand)。如下图,画出了一个GRC,边上的数值即为Demannd/Capacity。Demand — Capacity即为溢出(overflow)的数目,若存在overflow,则congestion map中就会将GRC的那条边高亮显示,overflow越大,则颜色越偏向于暖色调(即红色)。

d. 根据经验,一般最大的overflow如果超过10,基本上这个设计就无法布通了,最好不要超过3~5。此外,若总的overflow超过2%,也认为设计在后续很难绕通。这些说明floorplan做的不是很好,需要进行修改或重新进行floorplan。关于congestion出现在什么地方,后续将进行说明。

以上是关于congestion相关的基本知识,便于理解,现在回到lab中进行实操。

单击 " Global route congestion " 按钮,再点击面板的 " Reload " 按钮,弹出对话框,其中主要包含拥塞分析的命令:

report_congestion -grc_based -by_layer -routing_stage gloabl

点击OK,弹出 "Errors "对话框,点击OK,如下图。之所以报错,是Macro未 fix住引起的,因为我们后续将再次运行create_fp_placement来修改macro的位置,所以没有fix住macro,关闭 "Global Routing Congestion "面板。

- 若macro较多时,可以将macro转换成数组,这样电源地和macro的布线更容易实现,source下面的脚本来达到以下四个目标:

a. 将macro尽可能放置在芯片的边缘位置

b. 将macro尽可能的组合在一起

c. 打开虚拟IPO(原地优化)来模拟时序优化(并防止不必要的布局优化)

d. 限制某些RAM的合法布局方向

source -echo scripts/macro_place_cons.tcl #脚本内容如下:

- 检查设置。建议在icc_shell窗口中使用向上方向键查找并重新执行 "strategy " 命令:

report_fp_placement_strategy

report_fp_macro_options

- 设置blockage。在所有macro周围设置10微米的hard blockage,这将更容易在macro周围创建PG ring,并避免在congestion和macro周围的布线DRC问题,用下面脚本实现:

source -echo scripts/keepout.tcl

- 再次进行macro的布局,命令如下:

create_fp_placement -timing_driven -no_hierarchy_gravity

发现macro的位置发生了变化,与未添加constrain之前的不一样。

- 对新的布局图进行congestion分析。重复上一次的步骤即可

- 锁住所有的macro,并保存单元

set_dont_touch_placement [all_macro_cells]

save_mw_cel -as floorplan_placed

9. 创建电源地网络

电源地网络相关知识:

电源规划的目标时给整个芯片的供电设计出一个分别均匀、稳定的电源网络,减少IR drop,避免EM问题。其主要包括以下内容:

a. 创建core PG ring:指为了均匀供电,包围在core周围的环形供电金属

b. 创建macro PG ring:包围在macro周围,给macro供电

c. 创建power strap:将core ring连接至core内,同时减小IR drop

d. 打power rail:标准单元的供电网络

电源地网络并不是布的越多越好,过多的电源地会占用太多的布线资源。除此之外,placement阶段我们通常会设置电源地下方标准单元的摆放密度或不摆放标准单元,防止引起拥塞问题11.所以电源地不能布太多,否则会降低设计的利用率。一般在不影响congestion的情况下,可以尽量多布电源地线。

以上是关于电源地网络设计相关的基本知识,便于理解,现在回到lab中进行实操。

1) 创建macro PG ring

lab中已创建一个脚本给六组macro创建PG ring,source脚本命令如下:

source ./scripts/macro_pg_rings.tcl

创建macro PG ring的方法:

a. 创建macro PG ring的macro group所在区域

b. 定义macro PG ring的金属层、偏移量和宽度

c. 创建金属线

2)PNS创建power strap和core ring

注:a. core ring和straps可以手动创建,但这需要估计strap的数量和宽度、core ring的宽度,以达到可接受的low IR drop。相反,也可以使用ICC自带的PNS功能,它可根据IR drop自动确定strap数量和宽度及core ring的宽度。

b. 若时间不够,使用 scripts/pns.tcl脚本,可执行步骤1~5,若使用该脚本,则跳过步骤6和7。

- 对strap进行属性设置:GUI—Preroute—Power Network Constrains—Strap Layers Constraints(若没有,切换界面:File—Task—Design Planning)

a. 在Layer中选择Metal 5,方向为Horizontal

b. 选择By strap number中,Max为24,Min为2

c. Width中的Max为4,Min为2

d. PG spacing中为Microns,值为0.6

e. 点击set按钮,重复上面操作,但方向变为Vertical,Layer变成Metal4,然后关闭对话框。

上面操作对应的命令如下:

- 对core ring进行属性设置:GUII—Preroute—Power Network Constrains—Ring Constraints

a. 在Layer中选择Metal 3(Horizontal),Metal 2(Vertical)

b. 选择Ring width选项和Variable,设Max为12,Min为10

c. 点击Set按钮,关闭对话框

对应的命令如下:

- 对之前创建macro ring时,未创建的macro创建PG ring:GUII—Preroute—Power Network Constrains—Ring Constraints

a. 选择Specified cell instances选项,在Layout窗口选择左上方的PLL宏单元

b. 重新返回上一步打开的对话框,点击Specified cell instances后面的 “箭头” ,方框中会出现选中macro的名字

c. 在Power Ground nets中输入VDD VSS

d. 将垂直和水平层分别设置未Metal 4和Metal 5,并将两者的宽度都改为3,单击Set,然后关闭对话框

对应命令如下:

- 全局电源地的设置:GUII—Preroute—Power Network Constrains—Global Constraints

a. 保持对话框中现有选项不变的情况下,选择 "No routing over hard macros "

b. 单击Set ,关闭对话框

对应命令如下:

- PNS的调用方法:GUII—Preroute—Synthesize Power Network

a. 在By power network by nets空白框里输入VDD VSS,且改变Supply voltage未1.32

b . Target IR drop选择10% of supply voltage(另外两种也可以选择观察一下),Power budget改为350

c. 在Pads info选项里面选择Specified pad masters,然后输入pv0i pvdi

d. 点击Apply,将看到IR drop 图

- 单击commit按钮,或输入以下命令,生成power straps和core ring

commit_fp_rail

- 放大芯片,查看所有的PG straps和ring是怎么创建的,注意macro和周围的power ring没有连接,且还没有PG rail

- 创建好power ring和straps后,需要连接IO、macro的电源地连接到core ring上,并创建标准单元的电源地线rail,命令如下:

preroute_instances

preroute_standard_cells -fill_empty_rows -remove floating_pieces

因为某些row上可能没有放置标准单元,所以需要添加fill_empty_rows填充这些空的rows

- 使用PNA对电源规划(IR drop)进行分析:GUII—Preroute—Analyze Power Network

a. Power Ground nets输入VDD VSS;Power budget为350mW,Supply volage为1.32,Specified pad masters为pv0i pvdi,然后点击OK,将看到另一张热图

分析最大IR drop和voltage supply是否满足条件

b. 关闭右侧的PNA电压降面板,并保存单元

save_mw_cel -as floorplan_pns

10. 时序分析

电源网络完成后,需要在时序上进行检查,具体步骤如下:

- 进入Layout窗口左侧的 " Visibility " 面板,展开Cell前的 " + " ,并确保 " standard "被选中

- PNS在matal 5和 metal 4 上创建了很多straps,这些straps被放置在标准单元上。可以有利的防止标准单元放置在straps下,这降低了沿带拥塞的可能性,并减少了对电源网络的串扰影响。在strap上应用完整电源网络阻塞,然后再次运行虚拟平面布局考虑pnnet的设置。

set_pnet_options -complete "METAL4 METAL5"

create_fp_placement -timing_driven -no_hierarchy_gravity

- 由于要检查时序,所以通过下面命令进行全局布线:

route_zrt_global

- 打开Global Route congestion(无需重新加载),查看congestion问题,然后关闭

- 使用 " view " 程序生成一个最大延迟时序报告(setup)

v report_timing

使用搜索机制,或标记单词 " slack " :RE search—type in—" slack " —Tag。上下滚动。在8个时钟组路径中的每个路径末尾,可以看到slack后使用过正值,表明设计满足建立时间,点击Close Search,然后关闭窗口

- 时序修复,如果存在violation,可以调用下面命令重新进行布线优化

optimize_fp_timing -fix_design_rule

- 保存设计

save_mw_cel -as floorplan_complete

11. 移除std cell,写出def文件

- 移除所有放置的标准单元,然后写出DEF floorplan文

remove_placement -object_type standard_cel

write_def -version 5.6 -placed -all_vias -blockages -routed_nets -rows_track_gcells -specialnets -output design_data/ORCA.def

- 验证def文件已被创建在design_data目录下

- 关闭设计库,不将设计保存在内存中:File—Close Library—Design All