ICC 图文学习——LAB3:Placement 布局

floorplan完成了芯片的整体规划后,需要对标准单元进行摆放。布局阶段主要内容包括:

· 完成布局和时序优化的设置

· 完成DFT和功耗优化的设置

· 完成标准单元位置的摆放

· congestion、timing和功耗的分析

· 逻辑增量优化

LAB3:Placement 布局

- 1. 布局设置和检查

- 2. DFT Setup

- 3. Power Setup

- 4. 布局和优化

- 5. 增量优化

相关文件的准备:

orca_lib.mw/CEL:

ORCA_floorplanned ORCA设计经过设计规划后,以Milkway格式保存

scripts/:

input_toggle_rate.tcl 用于设置输入端口的统计切换速率的脚本

ndr.tcl 包含定义非默认时钟布线规则命令的脚本

opt_ctrl.tcl 时序和优化控制

design_data/:

OECA_TOP.scandef 在扫描链重组期间使用的扫描链信息

.synopsys_dc.setup scripts/:设置的变量

1. 布局设置和检查

- 启动ICC GUI模式

cd lab3_placement

icc_shell -gui

source scripts/opt_ctrl.tcl

- 进行macro的固定。一般情况下,macro在布局规划阶段已被fix住,但为了防止在更改macro位置后,忘记将其fix住,所有最好再次进行macro的固定。

set_dont_touch_placement [all_macro_cells]

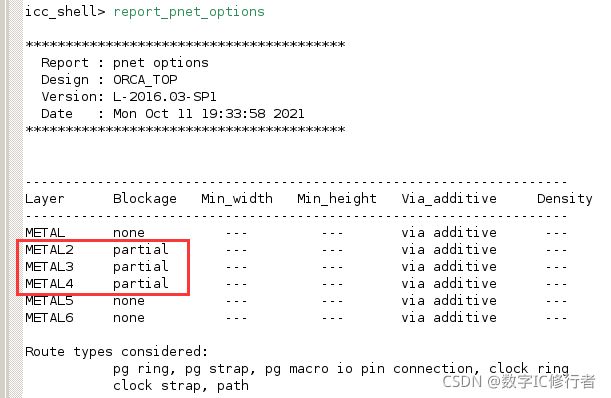

- 检查route layer是否设置正确(是否有忽略的layer),否则会影响congestion map的准确性

report_ignored_layers

- 检查标准单元摆放约束(被放置在metal2-metal4下,且没有发生DRC违反)

report_pnet_options

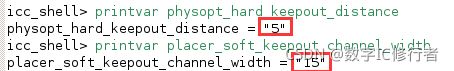

- 检查placement blockage是否正确添加,且不是默认值0

printvar physopt_hard_keepout_distance

printvar placer_soft_keepout_channel_width

- 设置NDR rule(双倍线间距)

source scripts/ndr.tcl

- 验证floorplan是否为布局做好准备

check_physical_design -stage pre_place_opt

- 执行不同的预布局检查

check_physical_constraints

2. DFT Setup

- DFT全称是Design for testing,叫可测试性设计。这一步主要是针对设计中存在scan chain(扫描链)的情况下,进行的优化。

- 扫描链的定义:将芯片中所应用的普通寄存器替换成带有扫描功能的扫描寄存器,首尾相连成串,从而实现附加的测试功能。这一步是在DC工具中实现的,在门级网表中,ICC读到设计进行了扫描链,需要读入scandef文件(由DC输出)。

- 检查扫描链的信息。

report_scan_chain

通过报告可以看到报告为空的,没有任何扫描链信息。此时我们就需要读入scandef文件了。

- 加载scandef文件(逻辑综合阶段生成)

read_def design_data/ORCA_TOP.scandef

- 生成扫描链报告(用view查看),发现设计已经读入了scan chain。

v roport_scan_chain

此时可以看到扫描链的信息了。若想在place_opt过程中执行扫描链的顺序优化,只需在place_opt命令后带上 -optimize_dft,进行扫描链重组。

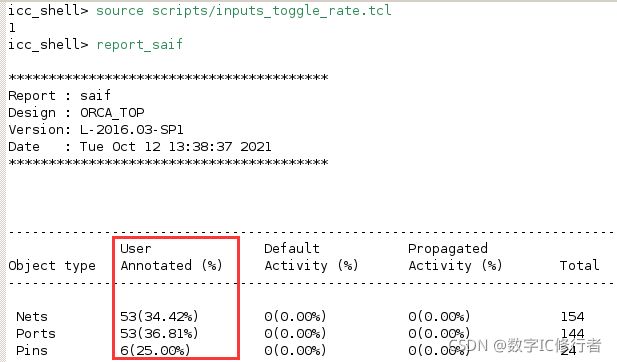

3. Power Setup

- 读取用户生成的切换速率文件

在power setup中,主要进行优化的是开关功耗。ICC通常会读入SAIF文件(ICC只能识别SAIF文件,可以将VCD文件转化为SAIF文件后使用),SAIF文件记录cell和net的翻转活跃度。

SAIF文件主要是指开关行为内部交换格式文件,用于仿真器和功耗分析之间交换信息的ASCII文件,但本lab没有SAIF文件,所以我们读取用户生成的切换速率文件。

report_saif

source scripts/inputs_toggle_rate.tcl

report_saif

- 查看默认的功耗优化功能

由于我们没有多Vth单元库(降低静态功耗),所以不做逻辑库和物理库的修改。但ICC可以通过减小cell的大小和移除buffer来降低静态功耗。系统默认开启泄露功耗优化功能。(2011版后的工具用report_power命令)

report_power_options

- 启动LPP功耗(动态)优化

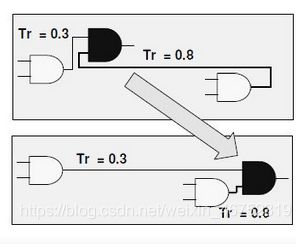

启用LPP(lower-power placement)功能,ICC再布局阶段会移动一些cells,来缩短高翻转率的net的长度,降低net上的电容,从而降低与之相连的cell的动态功耗。如下图,缩短高翻转率0.8的net长度,来降低功耗,

set_power_options -low_power_placement true #2011前的版本命令

set_optimize_pre_cts_power_options -low_power_placement true #2011后的版本命令

reoprt_power_options #2011前的版本命令

reoprt_power #2011后的版本命令

- 保存当前设计

save_mw_cel -as ORCA_preplace_setup

4. 布局和优化

place_opt

由上图可以发现,已完成了标准单元的摆放。接下来对布局进行优化,命令如下:

place_opt -area_recovery -optimize_dft -power

a. -area_recovery可以减小非关键路径的单元尺寸,帮助减少拥塞和power

b. -optimize_dft:对扫描链重组,减少扫描链的走线长度,节约布线资源,减少congestion

c. -power:对设计进行功耗优化。

- 保存当前布局后的设计

save_mw_cel -as ORCA_place_opt

由上图可以发现,拥塞情况还比较好,没有集中在某一区域。

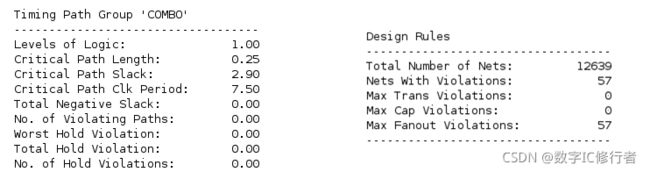

4. 关闭GR 拥塞面板,并生成物理设计报告(cell个数、利用率)

report_design -physical

- 生成质量报告(时序、设计规则等信息)

report_qor

- 查看功耗

report_power

5. 增量优化

通过前面的分析和优化,若设计还存在拥塞等问题,可以进一步做增量优化,来满足要求。同时可以使用GLPO技术进一步降低功耗。

- 启动门级功耗优化技术(GLPO)

set_power_options -dynamic true

- 使用增量逻辑优化

psynopt -area_recovery -power

- 重复上一节(布局和优化)中的步骤3~6。

- 保存设计并退出ICC

save_mw_cel -as ORCA_placed

exit