spyglass 学习笔记之cdc check

和lint check一样添加文件,goal 选择 cdc check

下面研究sdc书写

CDC setup 可以通过以下流程

建立SpyGlass CDC设置:

将时钟生成模块指定为black box

为设计指定时钟和复位

使用设置管理器 将时钟生成模块指定为black box

对时钟生成模块(比如PLL)的内部执行SpyGlass CDC分析非常复杂,而且对整体SpyGlass CDC分析几乎没有价值。将这些块标记为黑盒子,除非你有详细的SGDC约束来定义这些模块的时钟特性

标记PLL时钟生成模块为black boxes的方法是,在project file中设置如下命令: clock -name "clk_sys" reset -name "rst_n" -value 0 Timing Constrain

按照它们的用途,大致分为以下几类:

- (1)描述芯片的工作速度,即时钟的频率,包括create_clock,create_generated_clock等

- (2)描述芯片的边界约束,包括set_input_delay, set_output_delay等

- (3)描述芯片的一些设计违反rule(DRV),包括set_max_fanout,set_max_capacitance, set_max_transition等

- (4)描述设计中一些特殊的路径,包括set_false_path,set_multicycle_path等

- (5)描述设计中一些需要禁止的timing

大致常用sdc如下:

clock相关:

- create_clock 创建基本源时钟

- create_generated_clock

- set_clock_uncertaint

- set_clock_groups

- set_input_delay

- set_output_delay

系统接口相关:

- set_input_transition

- set_load set_driving_cell

时序特例相关:

- set_false_path

- set_multicycle_path

逻辑赋值相关:

- set_case_analysis

研究sdc书写转sgdc规律:

########################################################################

#Section 1: List of source clocks

#These clocks have set_false_path/set_clock_groups/set_clock_uncertainty associated with them

- eg:clock -name "A2D_SYS_CLK" -domain d0 -edge { "0.000000" "12.500000"} -period 25 -tag cc_osc_clk

########################################################################

#Section 2: List of remaining source clocks

#These clocks do not have the set_false_path/set_clock_groups/set_clock_uncertainty constraints associated with them

########################################################################

#Section 3: List of generated clocks

#These clocks satisfy either of the following conditions

#a. Generated clocks have domains different than the domains of their source clocks

#b. Generated clocks are specified on the black-boxe

########################################################################

#Section 4: List of generated clocks which have same domain as that of their source clock

########################################################################

#Section 5: List of valid set_case_analyis constraint generated from set_case_analysis command.

- eg:set_case_analysis -name "ggggggg_digital.u_inf_clk.esd_sram_recover_clken" -value 0

########################################################################

#Section 6: List of valid abstract_port/input constraint generated from set_input_delay command.

- eg:abstract_port -ports "P2D_DB[0]" -clock "P2D_WRX"

- sdc:set_input_delay -max [expr $clk_period_wr * 0.6] -clock cc_mcu_wr {P2D_DCX}

########################################################################

#Section 7: List of valid output constraint generated from set_output_delay command.

- eg:output -name "D2SRAM_SC_COL_R[2]" -clock "A2D_SYS_CLK"

########################################################################

#Section 8: List of valid clock_sense constraint generated from set_clock_sense command.

#These constraint are generated only for -stop_propagtion in set_clock_sense.

########################################################################

#Section 9: List of valid cdc false path constraint generated from sdc command.

#These constraint are generated only for real clocks.

- sdc:set_clock_groups \ -logically_exclusive \-group {cc_mcu_wr mcu_spi_otp_clk} \ -group {cc_mcu_rd} \ -group {cc_osc_clk} \ -group {cc_clk_sys}

- set_false_path -from [get_ports A2D_LVD_VCI]

- set_false_path -to [get_ports D2P_TESTO[3]]

三种类型set group 和set_false_path form**to**/set_false_

-----------------------------------------------------------------------------------------------------------------------------------

- skip_sgdc_sanity_start

- cdc_false_path -from cc_mcu_wr -from_type clock -to cc_mcu_rd -to_type clock

- cdc_false_path -from cc_mcu_rd -from_type clock -to cc_mcu_wr -to_type clock

- cdc_false_path -from cc_mcu_wr -from_type clock -to cc_osc_clk -to_type clock

- cdc_false_path -from cc_osc_clk -from_type clock -to cc_mcu_wr -to_type clock

- cdc_false_path -from cc_mcu_rd -from_type clock -to cc_osc_clk -to_type clock

- cdc_false_path -from cc_osc_clk -from_type clock -to cc_mcu_rd -to_type clock

- skip_sgdc_sanity_end

########################################################################

#Section 10: List of disable_timing constraint generated from set_disable_timing sdc command.

#These constraint are generated only for those sdc command which have object list as lib cells only.

########################################################################

#Section 11: List of valid false path constraint generated from sdc command.

#These constraint are generated only for real clocks.

#The type for constraint false_path is specified as below:

# - scg_logically_exclusive: When it is translated from set_clock_group -logically_exclusive

# - scg_physically_exclusive: When it is translated from set_clock_group -physically_exclusive

# - scg_asynchronous: When it is translated from set_clock_group -asynchronous

# - sfp: When it is translated from set_false_path

########################################################################

#Section 12: List of valid sg_multi_cycle constraint generated from sdc command.

########################################################################

#Section 13: List of valid set_lib_timing_mode constraint generated from set_mode sdc command.

Spyglass 使用笔记

- Spyglass lint check

软件load命令:module load spyglass/2017

设置阶段:

设置阶段的主要工作是:

添加设计文件、SGDC文件、预编译文件和技术文件。

指定影响SpyGlass运行的各种设计读取选项。例如,你可以在设计中指定顶层模块、更改语言、指定宏等等。

运行design-read流程来执行第一级的HDL分析。在进入下一阶段之前,必须解决此阶段报告的致命错误(FATAL)。

- 需要读入的文件

- rtl hdl files

- sgdc

- hdl libraries

- technology librares

- source list files

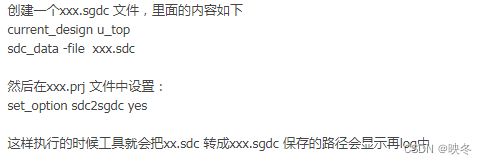

约束文件(SGDC)

需要设置选项 set_option sdc2sgdc yes

这样就可以直接加入sdc文件即可自动转化成sgdc文件

转化的sgdc所在目录

spyglass-1/your_design_top/Design_Read/spyglass_reports/sdc2sgdc

具体操作如下:

设置步骤不对会造成fatal 错误,

如下:若是只设定set_option sdc2sgdc 并没有创建加入sdc 以及相应sgdc 就会报fatal

必须给按顺序添加完毕,另外file add 不支持添加sdc文件,需要用shell去关联

目标(Goal)设定和运行(Run)阶段

在此阶段将选择并运行目标。目标是规则的集合。可以选择规则,也可以指定规则执行的顺序

spyglass 类似pt,是静态验证工具。特点就是不需要编写testbench,就可以验证。

步骤如下:

点击Design setup进入读入设计界面

点击Goal Setup进入目标选择界面

点击Analysis results查看检查结果

一定要将每个结果都检查一遍。如有报错,先在最左边的help viewer中查看报错原因。如果是RTL代码问题,则优化代码,如果确定没有问题,则修改约束脚本,增加约束,直到每一项结果都是绿色

Goal : lint/lint_rtl

检查设计的基本连接问题

检查设计的基本模拟问题

检查设计建议的设计实践和结构问题

检查设计的基本合成问题

- 下面是检查目标:

- lint检查

- 多驱动

- 组合逻辑产生的latch

- 输入悬空

- 跨时钟域的处理和同步

- 高扇入mux,同步/异步重置的使用

模块端口信号没有read,即无使用

信号多余没连

没有定义timescale,却使用#

移位寄存器过度移位导致数据丢失

数据位宽不匹配

组合逻辑和时序逻辑混写

注意:操作时目录不要乱跳,会导致fatal

- Spyglass cdc check

Timing Constraint按照它们的用途,大致分为以下几类:

(1)描述芯片的工作速度,即时钟的频率,包括create_clock,create_generated_clock等

(2)描述芯片的边界约束,包括set_input_delay, set_output_delay等

(3)描述芯片的一些设计违反rule(DRV),包括set_max_fanout,set_max_capacitance, set_max_transition等

(4)描述设计中一些特殊的路径,包括set_false_path,set_multicycle_path等

(5)描述设计中一些需要禁止的timing arc,例如set_disable_timing

需要注意的是,设计的不同阶段我们使用的sdc都有所不同(当然,有的公司比较强大,会有一套golden sdc)。比如说,综合时由于模型的粗糙,我们会选择过约sdc,将时钟频率设得更高一些;CTS之前,由于skew的不确定性,通常我们也会加大uncertainty;还有signoff tool与PR工具correlation问题,margin的设置也会不一样。

那我们如何去合理定义一个设计的sdc呢?

这是一项非常有难度的工作,其实常用的sdc命令就以下几条,但要准确运用他们可不容易。

clock相关:

create_clock

create_generated_clock

set_clock_uncertainty

set_clock_groups

set_input_delay

set_output_delay

系统接口相关:

set_input_transition

set_load

set_driving_cell

时序特例相关:

set_false_path

set_multicycle_path

逻辑赋值相关:

set_case_analysis

- Cdc check setup

必须有constraint

- 时钟和重置的健全检查

- 时钟域交叉检验

- 块block跨时钟域检查

- 更高层次检查

可以理解成cdc检查是深层次对sdc的完善,在spyglass操作递进的流程中也有constraint的检查和check,如下:

Sdc_check:

检测时钟规格中的不一致,生成的时钟,并对覆盖的和冲突的约束执行基本检查。如果没有清晰的时钟定义,约束验证和异常验证的其余部分将是无效的。覆盖的和冲突的约束可能不能正确地捕获设计意图。

还检测输入/输出延迟、时钟延迟和时钟不确定性规范中的不一致性

阅读spyglass user guider 系统如下操作:

记操作相同端口对不同时钟的delay设定时,其delay时间参数不能写成一样的,否则会报错,或者添加-add_delay 参数亦可

约束规则:

先创建基本base时钟,交个系统完善时钟,关于set input delay 和 output delay的设定规则,即所有输入输出信号,只要是关于寄存器的输入输出逻辑都要进行约束,各自信号只需要约束与其相应的操作时钟即可。基本格式如下:

单比特信号直接大括号信号名即可,

多比特信号需要使用get_ports

#---------------------------------------------------------------

set_input_delay -max 6 -clock sscg_clk {one_line_len}

set_input_delay -min 3 -clock sscg_clk {one_line_len}

#---------------------------------------------------------------

set_input_delay -max 6 -clock sscg_clk {get_ports act_hcycle}

set_input_delay -min 3 -clock sscg_clk {get_ports act_hcycle}