【计算机模型机设计】单周期MIPS CPU设计报告

2022年结束了,过去一年确实发生了很多事情,开心的、伤心的、激动的、平凡的…这些都已经成为过去了,只希望在新的一年里,能够多一些开心,少一些emo,做一些自己喜欢的事情。

其实说实话,感觉我的2022年挺不尽人意的,很多事情明明可以坚持下去,最后都以放弃结束了;明明可以努力争取,却还是以摆烂结束…这些不尽人意就随着2022一起走吧!这些在2023年会改变的。

啊哈哈哈哈,大家一起加油哇!!!

单周期MIPS CPU设计报告

-

- 一、计算机模型设计概述

-

- 1.1设计目的

- 1.2设计任务

- 1.3设计要求

- 1.4技术指标

- 二、单周期MIPS CPU方案设计

-

- 2.1主要功能部件

- 2.2数据通路的设计

- 2.3控制器的设计

- 三、单周期MIPS CPU的详细设计与实现

-

- 3.1主要功能部件实现

- 3.2详细的数据通路的实现

- 3.3详细控制器的实现

- 四、主要故障与调试

-

- 4.1故障现象一以及解决方法

- 4.2故障现象二以及解决方法

- 五、体会心得

- 结束语

一、计算机模型设计概述

1.1设计目的

- 《数字逻辑与计算机组成》是计算机科学与技术专业的核心基础课。该课程力图以“培养学生现代计算机系统设计能力”为目标,贯彻“强调软/硬件关联与协同、以 CPU 设计为核心/层次化系统设计的组织思路,有效地增强对学生的计算机系统设计与实现能力的培养”。

- 本课程设计是完成该课程并进行了多个单元实验后,综合利用所学的理论知识,并结合在单元实验中所积累的计算机部件设计和调试方法,设计简单计算机系统。所设计的系统能在 LOGISIM 仿真平台上正确运行,通过检查程序结果的正确性来判断所设计计算机系统正确性。

- 本课程设计属于设计型实验,不仅锻炼学生简单计算机系统的设计能力,而且通过进行中央处理器底层电路的实现、故障分析与定位、系统调试等环节的综合锻炼,进一步提高学生分析和解决问题的能力。

1.2设计任务

- 本课程设计的总体目标是利用 LOGISIM 仿真平台,设计MIPS CPU,要求所设计的CPU 系统能支持自动和单步运行方式,能正确地执行存放在主存中的程序的功能,对主要的数据流和控制流通过 LED、数码管等适时的进行显示,方便监控和调试。利用仿真软件对模型机系统中各部件进行仿真分析和功能验证。具体设计任务如下:

- 在logisim平台利用已给出的组件构建一个32位MIPS单周期CPU,该CPU支持如表1. 1列出的核心指令集中的8条指令。要求绘制单周期MIPS CPU数据通路、实现单周期硬布线控制器,并最终能在完成的CPU上运行冒泡排序的测试程序sort.hex且获得正确的输出结果。

- 表1.1 8条核心指令集

| MIPS指令 | 格式 |

|---|---|

| add r d , rd, rd,rs,$rt | R[ r d ] ← R [ rd]←R[ rd]←R[rs]+R[ r t ] 溢出时产生异常,且不修改 R [ rt] 溢出时产生异常,且不修改R[ rt]溢出时产生异常,且不修改R[rd] |

| slt r d , rd, rd,rs,$rt | R[ r d ] ← R [ rd]←R[ rd]←R[rs] |

| addi r t , rt, rt,rs,imm | R[ r t ] ← R [ rt]←R[ rt]←R[rs]+SignExt16b(imm) 溢出产生异常 |

| lw r t , i m m ( rt,imm( rt,imm(rs) | R[ r t ] ← M e m 4 B ( R [ rt]←Mem4B(R[ rt]←Mem4B(R[rs]+SignExt16b(imm)) |

| sw r t , i m m ( rt,imm( rt,imm(rs) | Mem4B(R[ r s ] + S i g n E x t 16 b ( i m m ) ) ← R [ rs]+SignExt16b(imm))←R[ rs]+SignExt16b(imm))←R[rt] |

| beq r s , rs, rs,rt,imm | if(R[ r s ] = R [ rs] = R[ rs]=R[rt]) PC ← PC + SignExt18b({imm, 00}) |

| bne r s , rs, rs,rt,imm | if(R[ r s ] ! = R [ rs] != R[ rs]!=R[rt]) PC ← PC + SignExt18b({imm, 00}) |

| syscall | 系统调用,这里用于停机 |

1.3设计要求

(1)根据课程设计指导书的要求,制定出设计方案;

(2)分析指令系统格式,指令系统功能;

(3)根据指令系统构建基本功能部件,主要数据通路;

- 表 1.2 24条核心指令集

| 指令 | 格式 |

|---|---|

| Add | add $rd, $rs, $rt |

| Add Immediate | addi $rt, $rs, immediate |

| Add Immediate Unsigned | addiu $rt, $rs, immediate |

| Add Unsigned | addu $rd, $rs, $rt |

| And | and $rd, $rs, $rt |

| And Immediate | andi $rt, $rs, immediate |

| Shift Right Arithmetic | sra $rd, $rt, shamt |

| Shift Right Logical | srl $rd, $rt, shamt |

| Sub | sub $rd, $rs, $rt |

| Or | or $rd, $rs, $rt |

| Or Immediate | ori $rt, $rs, immediate |

| Nor | nor $rd, $rs, $rt |

| Load Word | lw r t , o f f s e t ( rt, offset( rt,offset(rs) |

| Store Word | sw r t , o f f s e t ( rt, offset( rt,offset(rs) |

| Branch on Equal | beq $rs, $rt, label |

| Branch on Not Equal | bne $rs, $rt, label |

| Set Less Than | slt $rd, $rs, $rt |

- 备注:指令功能及指令格式参考 MIPS32 指令集

| 指令 | 格式 |

|---|---|

| Set Less Than Immediate | slti $rt, $rs, immediate |

| Set Less Than Unsigned | sltu $rd, $rs, $rt |

| Jump | j label |

| Jump and Link | jal label |

| Jump Register | jr $rs |

- 备注:指令功能及指令格式参考 MIPS32 指令集

| 指令 | 格式 |

|---|---|

| syscall(display or exit) | Syscall |

- 备注:If v 0 = = 34 数码管显示 v0==34 数码管显示 v0==34数码管显示a0值 else halt(停机指令)

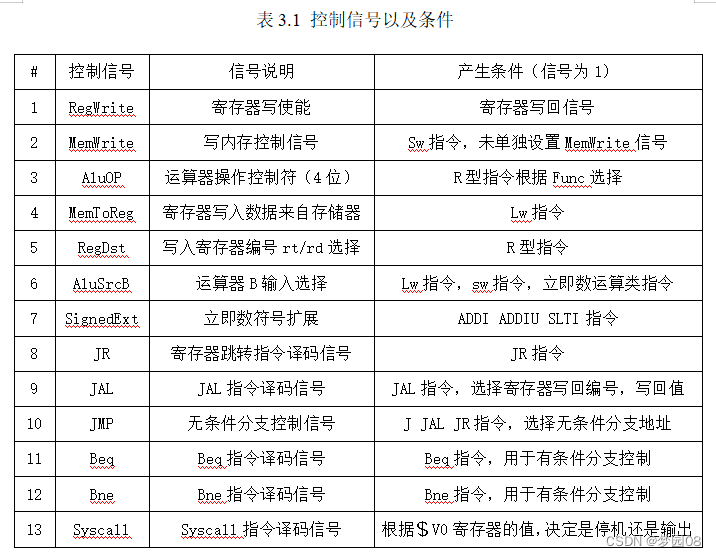

(4)根据功能部件及数据通路连接,分析所需要的控制信号以及这些控制信号的有效形式;

(5)设计出实现指令功能的硬布线控制器和微程序控制器;

(6)调试、数据分析、验收检查;

(7)课程设计报告和总结。

1.4技术指标

(1)支持表 1.1 中8 条基本 32 位 MIPS 指令;

(2)能运行由自己所设计的指令系统构成的一段测试程序,测试程序应能涵盖;

(3)所有指令,程序执行功能正确;

(4)能运行教师提供的标准测试程序,并自动统计执行周期数。

二、单周期MIPS CPU方案设计

2.1主要功能部件

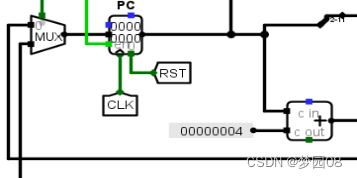

1、程序计数器:在时钟沿到来时,用NPC的值更新PC。

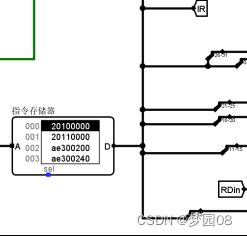

2、指令存储器:将PC输入的地址对应的指令输出。

3、ALU:将A,B,C输入的操作数按照ALUOp信号进行相应的算术运算、逻辑运算或移位操作,输出为D。

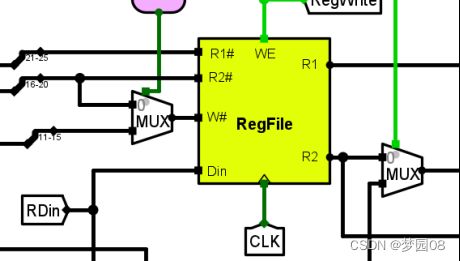

4、寄存器组:本系统的寄存器组,可以读出指令中指定rs,rt对应的寄存器的数据,也能在时钟沿到来时将WDSel指定数据源的数据写入WRSel指定的寄存器之一。

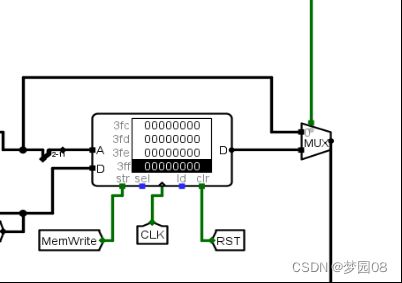

5、数据存储器:按照ALUOUT给出的地址,将从RF读出的数据在时钟沿到来时写入存储器;或从存储器中读出对应地址的数据。

6、单周期硬布线控制器:按照OP和Func的值输出对应的控制信号。

2.2数据通路的设计

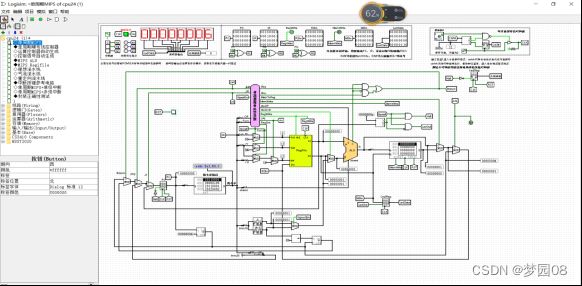

单周期MIPS CPU数据通路要将运算和功能部件进行连接,组成一个能个执行取值、译码、执行、进一步可能包含中断的数据连接,能够让指令从PC开始,流向各运算和功能部件,并成功指令相应的功能,给出相应的返回,并且数据通路要具备基本的CPU要求,能够形成相应的数据流和状态转移。

因为是单周期CPU,所有指令均在一个时钟周期内完成操作,所以指令与数据分别采用ROM及RAM存储。一个指令周期包含取指周期和执行周期,因此实验的数据通路架构应该分为两块,即取指和执行。

RAM是一种可读/可写存储器,其特点是存储器的任何一个存储单元的内容都可以随机存储。ROM是只能对其存储的内容读出,而不能对其重新写入的存储器。

取址阶段完成取指令和分析指令的操作,称为取指周期。执行阶段完成指令的操作,成为执行周期。取指(包含跳转和分支指令,跳转和分支指令可改变程序的控制流)和PC相对寻址指令(地址计算依赖于PC值)称为“分支”,绝对地址指令(地址计算不依赖于PC值)成为“跳转”。具有跳转功能的指令有JR、J、JAL以及分支指令BEQ、BNE。

PC默认输入为PC+4(无跳转时下一条指令地址),跳转发生时根据不同的指令会指向不一样的地址,所以使用了三个二路选择器来实现跳转。一般情况下指令是顺序执行,控制信号为PC+4,我们用加法器来实现。输入端为当前指令地址和32位整数00000004,输出即为PC+4。

BEQ和BNE是根据比较的结果改变控制流,ifequal或者ifnotequal,所以可以合并为一条指令Branch。Branch、JMP、JR均为低电平时输入PC+4,否则就输入高电平的信号对应的那一地址。如果Branch为高电平而JR、JMP为低电平时输入PC+4+(SignExtImm<<2),即图中的PC+imm16<<2。

根据地址从指令寄存器中读出指令,再通过分线器读出指令的各个部分,硬布线控制器通过opcode和funct分析出指令将要执行的操作并产生控制信号。取指部分结束。

执行部分分为以下6个部分:

1.首先需要从数据寄存器进行输入。

2.再到运算器输入。

3.将数值存入存储器中。

4.当JAL信号为高电平时,把PC+4的值写回数据寄存器。(存放返回的地址)

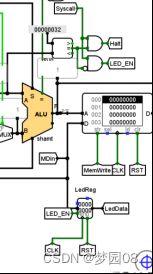

5.Syscall指令与Led显示屏的输出:

6.总周期数的计算:为了方便平台测评,实验还要提供计算总周期数的功能,未停机时即为一个周期。执行部分到此结束。

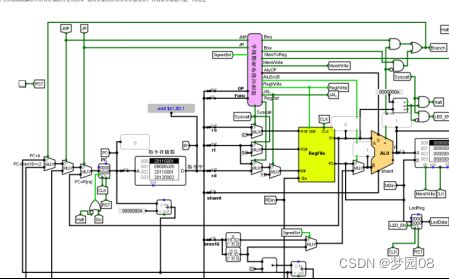

CPU数据通路图如下:

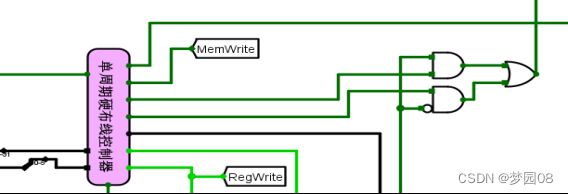

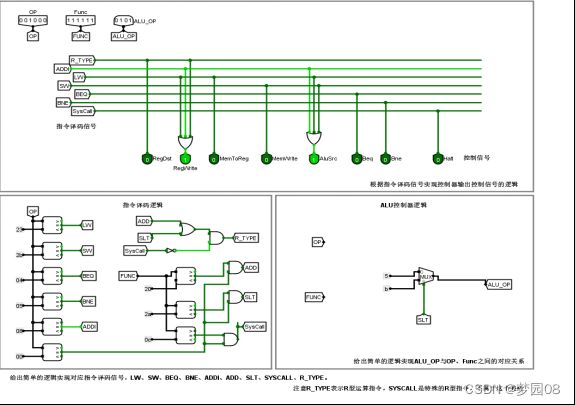

2.3控制器的设计

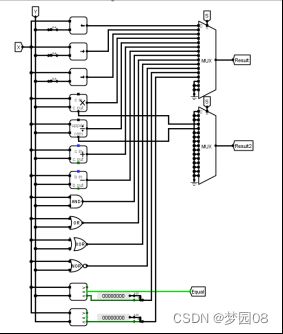

根据给出的单周期硬布线控制器的线路,实现其中的运算器控制器和控制信号生成。使用logisim的组合逻辑电路分析功能,获取了相应量的表达式就可以自动生成对应的电路。

1.运算器控制器

运算器控制器设计的基本思想是通过24条MIPS指令的运算指令,进行组合逻辑分析,将运算指令送入到ALU_OP中。首先要对24条MIPS指令具体的执行过程进行分析,然后对每条MIPS指令,结合运算器ALU单元的运算规格,给出每条MIPS指令的运算类型,填入到自动生成表格中,进行ALU_OP值的生成,然后利用分析电路功能,自动生成电路。

2.控制信号生成器

控制信号生成器的基本思想与运算器部分类似,但这次不是对于24条MIPS指令的运算执行部分进行分析,而是对于24条MIPS指令具体所需要的控制信号进行分析,对每一条MIPS所需的控制信号分析,通过组合逻辑分析,得到控制信号的组合逻辑。

三、单周期MIPS CPU的详细设计与实现

3.1主要功能部件实现

- 程序计数器:在不接收到跳转指令时,依次取指令,因每条指令长度都为4个字节,所以每次取完指令PC+4读取下一条指令。

- 指令存储器:使用一个随机存储器作为指令存储器。

- 寄存器组:根据从指令存储器中读取的指令辨别指令类型,以R型为例,将指令的Rs和Rt存入寄存器组中,在R1R2端输出传入运算器,计算完毕后传入WD写入Rd中。

- 数据存储器:接收一个地址并在地址位置写入WD传入的值。

- ALU:根据ALUOP来选择运算器,并将计算结果输出。

- 单周期硬布线控制器:根据输入的OP和Func来控制电路的整体工作状态。

3.2详细的数据通路的实现

保存当前运行的指令的地址的寄存器数据通路合并的,把各种功能的数据路径合并,使得每个时钟周期执行一条指令基本方法:使用多路选择器与控制信号。通过一条指令来说明:(clk上升)使用当前PC寄存器的值取出一条指令。(clk高电平)指令送到IR寄存器,分段直接送往译码单元和寄存器堆,获得ALU_OP和Write_Reg信号。ALU接收到ALU_OP对两个读出的数据进行运算,同时计算标志寄存器的值。(clk下降沿)同时激活PC自增、目标寄存器的写入、标志寄存器的更新,根据高电平生成的控制信号来确定是否写入。

最左侧多路选择器,当执行有条件跳转指令时,选择跳转地址,跳转地址由15位的立即数运算得到;下一层为无条件跳转指令选择,当执行JAL(函数调用指令)或J(无条件跳转指令)选择由26位立即数运算得到的地址;第三层选择为JR指令(跳转到寄存器记录地址,一般用于在JAL调用退出时使用),一般选择寄存器保存JAL执行时PC的值,函数调用后,再读取寄存器的值进行返回。

3.3详细控制器的实现

指令控制逻辑,通过OP判断指令,根据指令输出对应的控制信号。ALU控制逻辑通过判断是加法还是比较指令并输出为ALUOP。

四、主要故障与调试

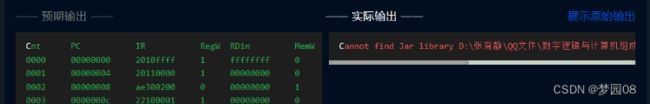

4.1故障现象一以及解决方法

- 原因分析:出现以上故障,是因为本地 cs3410.jar 和测试平台中的 cs3410.jar 路径不一样导致的。

- 解决方案: 将本地的 jar 文件和 cpu.circ 文件在同一目录下,如果出现这个问题,可以调整将本地 cs3410.jar 先移动到 cpu.circ 同目录下后,打开 cpu.circ,logisim 会提示找不到 cs3410.jar,重新指向同目录 cs3410.jar,存盘退出,再重新上传电路文本内容。

4.2故障现象二以及解决方法

- 故障现象:

- 原因分析: PC,IR,RegW 等信号全是xxxxx,悬浮态,表明工作文件 CPU.circ 中没有输出对应信号。

- 解决方案: 解决办法复制最新的 cpu.circ 工作文件中的引脚区到测试电路中,并按要求输出对应引脚。

五、体会心得

“纸上得来终觉浅,绝知此事要躬行”,通过指导书的帮助、自己的不断摸索以及与同学老师的探讨,我一步一个脚印,从单周期到多周期,从数据通路与控制信号表格,到模块的逐个编写,从模块单独测试到系统整体测试,我不断努力,最终取得实践的成功。当然,由于时间所限,设计的 CPU 并非完美无缺,还有一些地方可以进一步优化。例如:①可以改变 PC 更新的时机,调整 debug 信号逻辑;②可以尝试不使用双符号位而使用更简易的方法实现 SLTU 指令;③可以从原理上进一步分析,尝试继续优化指令实现的周期安排,尝试更合理地划分数据通路等等。

结束语

希望这篇文章会对大家有帮助,也希望大家在编程的道路上越走越远,早日成为IT届大佬!!!

后续将持续更新,大家的支持就是我创作的动力!!!