CPU工作流程(寄存器、缓存cache、内存)

1、Linux系统硬件模块之CPU - 知乎

2、CPU的基本工作流程_Bo0o2的博客-CSDN博客_cpu工作流程

3、【硬件设备】CPU系列之工作流程_Night_ZW的博客-CSDN博客_cpu工作流程

4、CPU基本工作流程_学习java的张三的博客-CSDN博客_cpu工作流程

5、操作系统中cpu如何工作_qq_42533216的博客-CSDN博客_cpu如何工作

1、计算机启动的大概流程:

- 通电

- 读取ROM里面的BIOS,用来检查硬件

- 硬件检查通过

- BIOS根据指定的顺序,检查引导设备的第一个扇区(即主引导记录),加载在内存地址 0x7C00

- 主引导记录把操作权交给操作系统

2、CPU工作流程:

A.取指单元(从内存中取得指令);

B.解码单元(完成解码[讲内存中取到的数据转换成CPU真正能运行的指令]);

C.执行单元(开始执行指令,根据指令的需求去调用不同的硬件去干活。);

我们通过上面知道了MMU是CPU的一部分,但是CPU有还要其他的部件吗?当然是有的啦,比如指令寄存器芯片,指令计数器芯片,堆栈指针。

指令寄存器芯片:就是CPU用于将内存中的数据取出来存放的地方;

指令计数器芯片:就是CPU为了记录上一次在内存中取数据的位置,方便下一次取值;

堆栈指针:CPU每次取完指令后,就会把堆栈指针指向下一个指令在内存中的位置。

他们的工作周期和CPU是一样快的速度,跟CPU的工作频率是在同一个时钟周期下,因此他的性能是非常好的,在CPU内部总线上完成数据通信。指令寄存器芯片,指令计数器芯片,堆栈指针。这些设备通常都被叫做CPU的寄存器。

寄存器其实就是用于保存现场的。尤其是在时间多路复用尤为明显。比如说CPU要被多个程序共享使用的时候,CPU经常会终止或挂起一个进程,操作系统必须要把它当时的运行状态给保存起来(方便CPU一会回来处理它的时候可以继续接着上次的状态干活。)然后继续运行其他进程(这叫计算机的上下文切换)。

————————————————

版权声明:本文为CSDN博主「qq_42533216」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_42533216/article/details/122580341

3、CPU的内部结构

1、算数逻辑单元ALU

ALU是运算器的核心,它是以全加器为基础,铺之以以为寄存器及相应控制逻辑组合而成的电路,在控制信号的作用下可以完成加、减、乘、除四则运算和各种逻辑运算,就像刚才提到的。这里就相当于工厂中的生产线,负责运算数据。

2、寄存器组Rs

Rs实质上是CPU中暂时存放数据的地方,里面保存着那些等待处理的数据,或已经处理过的数据,CPU访问寄存器所用的时间要比访问内存的时间短,采用寄存器可以减少CPU的访问内存次数,从而提高了CPU的工作速度,但是因为受到芯片面积和集成度所限制,寄存器组的容量不可能很大,寄存器组可分为专用寄存器和通用寄存器,专用寄存器的作用是固定的,分别寄存相应的数据,而通过寄存器通途广泛并可以由程序员规定其用途,通用寄存器的数目因微处理器而异。

3、控制单元

正如工厂的物流分配部门,控制单元是整个CPU的指挥控制中心,由指令寄存器、指令译码器、和操作控制器三个部件组成,对协调整个电脑有序工作极为重要,它根据用户预先编好的程序,以此从存储器中取出各条指令,放在指令存储器中通过指令译码器分析确定应该进行什么操作,最后通过操作控制器按时序,向相应的部件发出微操作控制信号,操作控制器,主要包括 节拍脉冲发生器 控制矩阵 时钟脉冲发生器,复位电路和启停电路等控制逻辑。

4、总线

就像工厂中各个部位之间的联系渠道,总线实际上是一组导线,是各种公共信号线的集合,用于作为电脑中所有各组成部分传输信息公共使用的公路,直接和CPU相连的总线,其中包括 数据总线 地址总线 控制总线 其中书库总线用来传输数据信息 地址总线用于传送CPU发出的地址信息,控制总线用来传送控制信号,时序信号和状态信息等。

结构

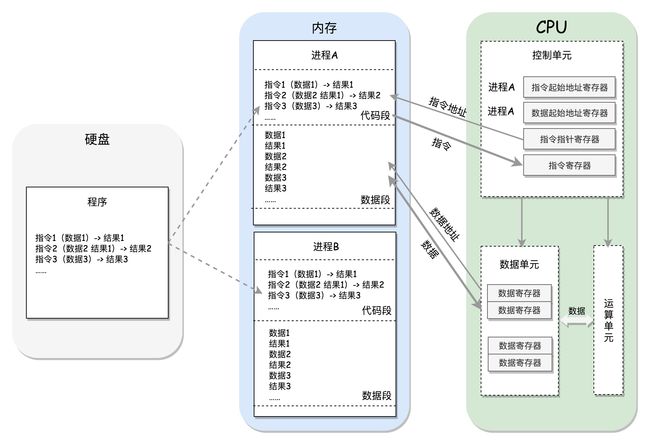

CPU 和内存是完成计算任务的核心组件,所以这里我们重点介绍一下 CPU 和内存是如何配合工作的。CPU 其实也不是单纯的一块,它包括三个部分,运算单元、数据单元和控制单元。

- 运算单元只管算,例如做加法、做位移等等。但是,它不知道应该算哪些数据,运算结果应该放在哪里。

- 运算单元计算的数据如果每次都要经过总线,到内存里面现拿,这样就太慢了,所以就有了数据单元(存储单元)。数据单元(存储单元)包括 CPU 内部的缓存和寄存器组,空间很小,但是速度飞快,可以暂时存放数据和运算结果。

- 有了放数据的地方,也有了算的地方,还需要有个指挥到底做什么运算的地方,这就是控制单元。控制单元是一个统一的指挥中心,它可以获得下一条指令,然后执行这条指令。这个指令会指导运算单元取出数据单元中的某几个数据,计算出个结果,然后放在数据单元的某个地方。

CPU逻辑上分为3个模块,分别是"控制单元","运算单元","存储单元",三个模块的功能通过名字也大概能猜出来。

控制单元

控制单元,由指令寄存器IR(InstrucTIon Register)、指令译码器ID(InstrucTIon Decoder)、操作控制器OC和程序计数器PC组成。

顾名思义,它是整个CPU的指挥控制中心,控制单元根据用户预先编好的程序,依次从存储器中取出各条指令,放在指令寄存器IR中,通过指令译码(分析)确定应该进行什么操作,然后通过操作控制器OC,按确定的时序,向相应的部件发出微操作控制信号

运算单元

顾名思义,它就是实现执行各种算术运算的功能,在控制信号的作用下可完成加、减、乘、除四则运算和各种逻辑运算。

存储单元

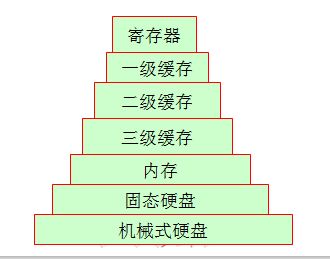

顾名思义,负责存储数据,包括缓存和寄存器组,是CPU中暂时存放数据的地方。但是有三个存储数据需要区分,按与CPU远近来分,离得最近的是寄存器,然后缓存 ,最后内存

寄存器:是有限存贮容量的高速存贮部件,可用来临时放指令、数据和位址的空间

缓存器:由于CPU直接从内存读取速度太慢了,所以在寄存器与内存之间设置缓存cache

然后寄存器组可分为专用寄存器和通用寄存器。专用寄存器(IR、PC)的作用是固定的,分别寄存相应的数据。而通用寄存器用途广泛并可由程序员规定其用途,通用寄存器的数目因微处理器而异

CPU的缓存(一级缓存、二级缓存、三级缓存)属于集成在CPU内部的RAM。

内存则属于安装在主板上的RAM,不属于CPU。

CPU片内的ROM

嵌入式学习系统里的ROM和RAM(转载)_lyndtao_Chen的博客-CSDN博客_bss段是rom还是ram

大部分的资料都宣称程序分为RO、DATA、BSS等段,RO段应该放在ROM里,DATA段放在RAM里云云。对于DATA、BSS,这些段因为有频繁的写操作,所肯定要放到RAM里,但是只读数据(包括代码段)必须放在ROM里吗?答案是不一定。RAM和ROM等存储单元的物理地址映射是由做硬件的数字工程师确定,他们在划分时主要会考虑电路的延迟,将这些储存单元按照一定的方式挂在同一条AHB总线上。而嵌入式平台软件工程师可以通过修改链接脚本来设置哪些数据、代码在程序运行时放在ROM里,哪些放在RAM里。(这里多说一句,RAM在系统刚上电的时候,其内容是随机的。所谓的数据、代码放在RAM里,是指在初始化时,CPU从flash里读下载的bin文件,也有的平台下载的是hex文件,找出其中的ram段,以类似于memcpy的方式将数据从bin文件里的对应位置拷贝到RAM映射到的物理地址里,这才是所谓的放在RAM里)

RAM分为很多种,关于SRAM、DDR、SDRAM、PSRAM等等的概念请自行百度,本文从软件的角度笼统一点,分为片内和片外ram。对于软件工程师的来说,它们的区别就是访问速度,

片内ram一般用TCM(Tightly Coupled Memory)的方式集成在CPU芯片内部,有单独的数据通道,它的访问速度可以和cache相媲美,而片外ram的访问要麻烦一些,CPU发出想访问的地址给AHB总线控制器,它会知道对应的地址是在片外RAM里,将访问请求递给RAM控制器,再由RAM控制器访问RAM后将数据返回。大体上片内的访问速度是片外RAM的1.5~2倍。片内ram集成在CPU芯片内部,它是在CPU设计时就加上的,它使用和CPU几乎一样的制作工艺和材料,而且增加了芯片的大小,所以成本比较高,一般也就只有几十K字节,好钢当然要用在刀刃上,片内ram用来存放中断处理handler、RTOS调度器、任务上下文切换、内存分配释放等使用频率最高的代码和

中断堆栈这种读写频率极高的内存区,如果有多余的部分也可以放一些经常被引用到的全局变量。

片外RAM一般就是采购的市面上的成品,如Samsung,Hynix,Apmemory等,价格相对便宜,其容量的可选范围也较为宽松,从几M到几G的都有,它可以用来存储全局变量,bss,以及我们常用到的malloc所分配的堆空间等。 还有一点不同的是:片内Ram上电就可以直接使用,而片外的RAM都需要一个硬件控制器完成对其时序的控制,软件人员则需要对该控制器编写专用的控制驱动

ROM一般是有两种:

一种是指集成在CPU片内ROM只读存储区域,一般是几K到几十K字节大小,用来存储系统刚上电时对cpu和一些核心外设(如时钟,串口,MMU、DRAM、Flash等)进行初始化的代码,它在程序运行中也是不可写的,要对它执行写操作只能使用硬件烧写器进行,也就是一般所说的下载程序,这部分的代码在芯片测试阶段可以进行编程器下载更新,量产后一般就会固化,不能做任何修改的;

另一种指的就是flash。首先需要说明的是,很多做嵌入式应用开发的同学一直把flash比作PC上的硬盘,其实它们指的是Nand flash,而对于很多小型的嵌入式系统,就只有一个2M或者4M的Nor Flash,它和硬盘有一个显著的区别:flash里存放的代码是可以由CPU直接取指并执行的,而PC上硬盘里的程序都需要加载到内存里才能运行。flash并不是绝对的运行时不可写,有时候应用程序需要保存一些配置信息到flash里,类似于PC程序的配置文件,以保证掉电了之后它的内容不会丢失,下次开机时可以直接从flash读取到。不过,flash的写操作要比RAM麻烦的多了,flash在写之前需要发送多个命令字来握手,还要先对即将要写的地址所在的扇区进行整体擦除,就是把该扇区里的内容全设为1,所谓写flash就是把其中的一些bit设为0;更要命的是,flash的每个独立bit位的写次数是有上限的,市面上大部分的产品都只能写10~100万次。多说一句,每个bit位的寿命是独立的,如果一个bit位在擦除和写的动作中,它的值始终为1,则不会有影响;例如反复对一个地址写0xF0,则不会影响高4bit的寿命,而低4bit每次都要先擦成1,再写入0,这样就会降低其寿命。

现在我们讨论一下RO、DATA、BSS到底应该放在RAM里还是ROM里?

首先考虑一下,有没有什么东西必须放在ROM里? 当然有,引导程序(系统的初始化代码)就必须放到ROM里。在CPU刚上电时,只能去一个默认的地址去取第一条指令,开始干活,这个地址都是映射到片内的ROM里,原因很简单,此时,作为外设的flash和DDR等都还没有初始化,CPU根本无法从它们那里读写数据,片内ROM里的这些代码就需要完成这些模块的初始化。另外,一个项目的处理器和主要外设确定了以后,这部分初始化代码在很长的时间里,都不需要做任何修改的。

那有没有什么东西必须放RAM里?当然也有,应用程序经常读写的全局变量,堆、栈等等,都需要放在RAM里,根据访问的频率,将频率最高的少量数据放到片内ram。

只读数据(代码段、程序里的const、字符串等)应该放在哪?一般来说,这些数据应该放在Flash里,因为它们不需要被修改,而且前面提到过,rom要比ram便宜的多。可能有人会有疑问,放在flash里,会不会读取的速度很慢?读ROM的速度是比读RAM的数据要慢一点,但是不要忘了,现代CPU都有强大的cache,而且数据Dcache和指令Icache都是分开的,在系统运行中,cache的命中率可以高达80~90%,所以大部分时候CPU都可以在第一时间就拿到想要的指令和数据。

最后分享两个楼主遇到的案例:

1 前面提到片内Ram是一块非常宝贵的空间,它的优点就是CPU可以在第一时间取到里面的数据。但是处于成本考虑,它的空间往往都非常有限。如果用户有两种比较耗时的业务,需要频繁的大量取指,但重点是它们

不会同时运行。这种情况下,就可以在链接脚本里开辟的片内Ram空间,将该段的链接选项加上NOCROSSREFS,再将这片空间的大小定义为这两个耗时业务代码占空间较大的那个(例,业务一有1K代码,业务二有2K代码,这片空间就定义为2K),在业务一开始时,将其代码拷贝到这块片内ram里(一般是用DMA的方式),运行业务一的代码;当业务二开始时,也是拷贝其代码到片内ram里。这样,两种业务的耗时操作在运行中都可以在第一时间里取到指令,对耗时业务做了很好的优化。

2 楼主曾经遇到过这样一个运行时死机,查看CPU寄存器可以看到是报一个取指了令异常,可是查看PC寄存器对应的地址,发现CPU正在取的一条指令是正常的,起初十分费解。后来通过仔细分析其死机前的运行情况才定位出原因,死机前一个task正在写flash,这时候来了一个中断,中断里调用了一个函数,其地址就在flash里,而此时flash处于一个不可读的状态,CPU在执行中断里的函数就拿不到指令,只能死机。

解决问题的办法有2种:一是在写flash的过程中屏蔽所有中断,这是一种很裸的方法,对于响应时间很敏感的嵌入式系统,一般都不允许随便关中断。二是将这个在flash里存储的函数放到RAM里,避免访问flash的冲突。

————————————————

版权声明:本文为CSDN博主「亦大乐谍」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

MCU按其存储器类型可分为无片内ROM型和带片内ROM型两种。

对于无片内ROM型的芯片,必须外接EPROM才能应用(典型芯片为8031)。

带片内ROM型的芯片又分为片内EPROM型(典型芯片为87C51)、MASK片内掩模ROM型(典型芯片为8051)、片内FLASH型(典型芯片为89C51)等类型CPU是中央处理单元(CentralProcessingUnit)的缩写,它可以被简称做微处理器(Microprocessor),不过经常被人们直接称为处理器(processor)。

MCU和CPU关系区别?

区别:CPU是数据处理的单元,MCU中一般包含CPU,但除了数据处理单元外还有其他的外围的模块,如、RAM、ROM、定时计数器和多种I/O接口等,也就是说,MCU是集成了CPU和其他外围模块的微型控制单元

数据从内存里拿出来先放到寄存器,然后CPU再从寄存器里读取数据来进行处理,处理完后同样把数据通过寄存器存放到内存里,CPU不直接和内存打交道。

为啥要这么麻烦呢,速度!就是因为速度。寄存器其实就是一块一块小的存储空间,只不过其存储速度要比内存快得多。近水楼台先得月嘛,它离CPU很近,CPU一伸手就拿到数据了,比在那么大的内存里去寻找某个地址上的数据是不是快多了?那有人问既然它速度那么快,那我们的内存硬盘都改成寄存器得了,我要说的是:你真有钱。

片内有ROM与RAM;

片外也有扩展的ROM与RAM。

芯片内部有片内,也有片外;

芯片外部,即独立的外接芯片,一般只有片外。

片内,片外,操作指令有差异。

特殊功能寄存器SFR一定要在片内,不能扩展,不在片外。

寄存器是ram还是rom 寄存器和存储器的区别是什么?-酷米网

寄存器与存储器的区别是什么?

从根本上讲,寄存器和ram的物理结构是不同的。通用寄存器是由基本RS触发器结构派生的D触发器,它是由一些与非门组成的结构。我们已经在数字电子领域看到了这一点。Ram有自己的过程,通常1bit由六个MOS晶体管组成。因此,二者的不同物理结构导致了不同的性能。寄存器存取速度快,但占用面积大。相反,ram面积小,功耗低。它可以制成大容量存储器,但存取速度相对较慢。1CPU中存在寄存器,速度很快,数量有限;内存是内存,速度有点慢,但数量很大;计算机做操作时,必须把数据读入寄存器进行计算。2存储器包括寄存器。内存有ROM和ram。寄存器仅用于临时存储,并且是临时分配的。关机后,内容就不见了`````

寄存器和CPU在一起,只能存储少量的信息,但存取速度很快;内存指的是硬盘、U盘、软盘、CD-ROM等存储工具,速度最慢;内存指的是内存模块,因为硬盘读取速度只有一半速度很慢,所以先把硬盘读入内存模块,然后再交给CPU进行处理,这很重要的主要区别是硬件电路的实现。寄存器为静态存储器SRAM,存储单元由6个晶体管组成,读写速度最快。CPU中的cache和寄存器采用SRAM电路,读写速度快,但成本昂贵,一般容量不大。与SRAM相比,SDRAM是一种由晶体管和电容组成的存储单元,由于它使用了电容充放电的高低电平来表示0和1,因此需要不断刷新,因此成本低廉。后来,随着SDRAM技术的不断发展,工作电平从2.5V降低到目前的1.2V,并且是双通道的。有数字电路基础的人都知道每个时钟周期都可以读取数据,而双数据速率SDRAM可以在每个时钟周期的上升沿和下降沿读取数据,因此理论上速度提高了两倍。这是我们经常看到的DDR内存模块,包括随后的DDR2、DDR3和DDR4。实际上,它们都属于SDRAM。通常,存储器中使用SRAM或SDRAM。存储器一般称为外部存储器、磁盘、NAND闪存等,属于ROM范畴。与上述ram不同的是,ram断电后数据会消失。ROM存储器的特点是断电后数据不会消失,因此主要用于存储已安装的软件、数据文件、电影、图片等;SRAM存储器主要用于存储正在运行的程序。

寄存器、RAM、ROM、Flash相关概念区别整理

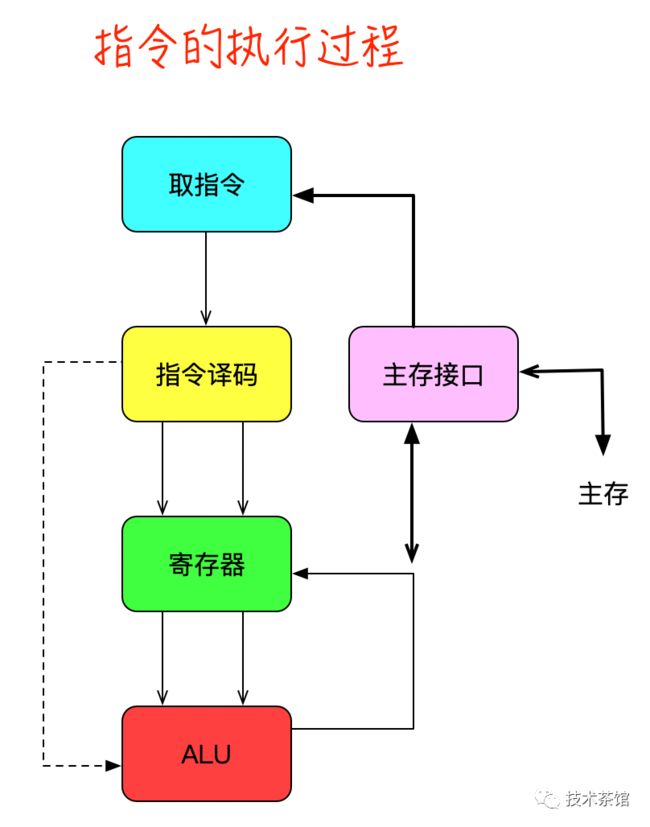

执行指令过程

几乎所有的冯·诺伊曼型计算机的CPU,其工作原理就像一个工厂对产品的加工过程,其工作都可以分为5个阶段:取指令、指令译码、执行指令、访存取数、结果写回。

指令---->内存---->控制单元(IR)---->控制单元(ID)---->运算单元---->存储单元---->内存

- 取指令(Instruction Fetch ):从内存读取指令字节,放到指令寄存器;

程序计数器PC中的数值,用来指示当前指令在主存中的位置。当一条指令被取出后,PC中的数值将根据指令字长度而自动递增:若为单字长指令,则(PC)+1PC;若为双字长指令,则(PC)+2PC,依此类推。 - 指令译码(Instruction Decode):从指令寄存器IR中拿来指令,翻译成CPU可以执行的形式(拆分和解释)

- 执行指令(Execute):完成指令所规定的各种操作,例如告诉算术逻辑单元(ALU)什么时候计算,告诉指令译码器什么时候翻译指令等等

- 访存(Memory):根据指令地址码,得到操作数在主存中的地址,并从主存中读取该操作数用于运算

- 结果写回(Writeback):把执行指令阶段的运行结果数据“写回”到某种存储形式

总线

各组成部分传输信息共同使用的“公路”,即总线。

直接和CPU相连的总线可称为局部总线。其中包括:

数据总线DB(Data Bus),数据总线用来传输数据信息;

地址总线AB(Address Bus) ,地址总线用于传送CPU发出的地址信息

控制总线CB(Control Bus),控制总线用来传送控制信号、时序信号和状态信息等

地址总线的位数,决定了能访问的地址范围到底有多广。

例如只有两位,那 CPU 就只能认 00,01,10,11 四个位置,超过四个位置,就区分不出来了。位数越多,能够访问的位置就越多,能管理的内存的范围也就越广。

而数据总线的位数,决定了一次能拿多少个数据进来。

例如只有两位,那 CPU 一次只能从内存拿两位数。要想拿八位,就要拿四次。位数越多,一次拿的数据就越多,访问速度也就越快。

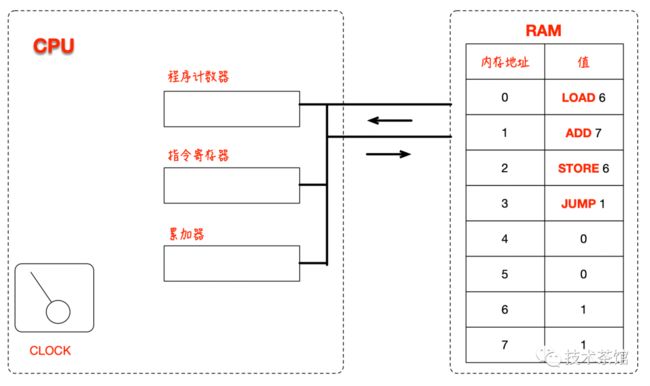

4、CPU的工作流流程

程序=指令+数据

工作原理:

总的来说,cpu从内存中一条一条的取出来指令和相应的是数据,按照指令操作码的规定,对数据与进行运算处理,直到程序执行完毕为止,具体的过程可以分为以下四步。

1取指令

cpu控制器从内存读取一条指令并放在寄存器

2指令编译

指令寄存器中的指令经过译码,觉得应进行那种操作,操作数在哪里

3执行指令

执行指令分为两步:取操作数和进行运算。

取操作数:CPU通过寻址操作从内存中读取操作数到寄存器中,暂时保存起来

进行运算:运算单元通过指令中的操作码,对寄存器中的数进行操作

4指令计数

修改指令计数器,决定下一条指令的地址。cpu重复以上三个步骤,处于内存代码段的指令被逐个的执行,直到程序结束为止。

在每个时钟滴答声中,CPU都会执行以下三种操作之一:

- 从内存地址中获取一条指令。

- 解码该指令。

- 执行指令。

我们运行一个简单的程序。它要做的就是数数。处理器分为三个步骤:提取,解码,执行。它只会循环重复这些。所以我们需要一些指令,实际上指令是放在内存中,因此,让我们将程序加载到RAM中。RAM还用于存储我们的答案和输出。这些都将以二进制形式存储,但现在不要让事情变得过于复杂,让它们易于阅读。

指令分为:两部分。第一部分是指令本身。第二部分通常是一个内存地址。

————————————————

版权声明:本文为CSDN博主「Bo0o2」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_57958234/article/details/124298120