基于STM32 ARM+FPGA伺服控制系统(二)软件及FPGA设计

完整的伺服系统所包含的模块比较多,因此无法逐一详细介绍,所以本章着重介绍

设计难度较高的 FPGA 部分并简单介绍 ARM 端的工作流程。 FPGA 部分主要有 FOC

算法、电流采样算法及编码器采样算法,是整个控制系统的基础,直接决定电机控制

效果的好坏。因为 FPGA 工作的特殊性,需要考虑设计时序的合理性及合理统筹多种

任务的执行顺序,导致了其设计难度大大提高。下面将对 FPGA 重要部分程序进行设

计说明,主要分为 SVPWM 算法模块、编码器反馈模块和电流采样模块。

4.1SVPWM 算法程序设计

根据第二章第四小节可以知道, SVPWM 算法的工作流程如图 4-1 所示。首先对 ܷ ߙ

和 ܷ ߚ 解码判断当前扇区,接着计算当前扇区的基本矢量所需的作用时间,下一步得出

PWM 比较值时间点,最后进行脉宽调制且加上死区时间形成互补 PWM 波驱控制逆变

4.1.1 软件模块设计

SVPWM 模块功能结构图如图 4-2 所示。模块的信号解释如下:

( 1 ) sys_clk

:系统时钟,工作频率为 50MHz 。

(2) sys_rst

:系统复位,低电平有效。

(3) svpwm_en

:模块使能信号。

(4) ualpha 、 ubeta :逆 Park 转换模块输出信号。

(5)其他

:六路互补 PWM 波。

该模块的工作原理及运算公式在第二章已经详细阐述,因此在这里不再过多赘述。

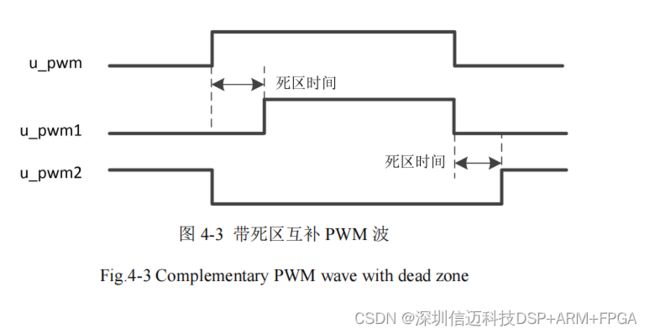

但需要注意的是由于逆变器的开关存在机械延迟,因此需要生成带死区时间的互补

PWM 波,这样可以避免因同时打开上下桥臂而导致短路致人受伤的情况。

生成带死区的互补 PWM 波原理是以计算得出的 PWM 波作为参考对象,然后根据

实际情况设定合理的死区时间。假设逆变器输入信号为高电平有效,当参考对象从低

电平跳变为高电平时,首先关闭下桥臂,再延时死区时间,最后打开上桥臂;当参考

对象从高电平跳变为低电平时,先关闭上桥臂,再延时死区时间,最后打开下桥臂。

其效果如图 4-3 所示。以 U 相为例,图中 u_pwm 为计算得到的参考 PWM 波, u_pwm1

4.1.2 仿真测试

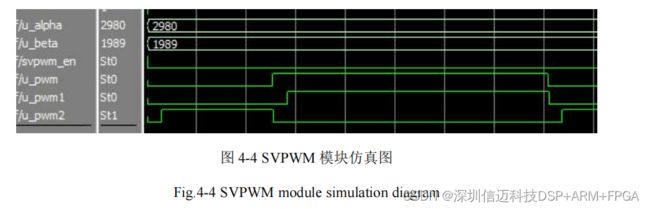

对 SVPWM 模块进行仿真验证,所得结果如图 4-4 所示。从图中可以看到,取任意

值赋值给 u_alpha 和 u_beta ,然后系统生成一个时钟周期 svpwm_en 信号,经过运算后

得出 u_pwm 作为参考 PWM 波。根据 u_pwm 信号生成互补 PWM 波 u_pwm1 和 u_pwm2 ,

4.2BISS-C 协议程序设计

4.2.1BISS-C 协议数据结构

BISS 协议来自 iC-Haus 公司,它适用于传感器的双向串行接口,而且带 CRC 校

验功能确保传输数据正确。与其他同类通信协议相比, BISS 协议在兼容性和网络结构

方面更具有优势,在高速性和时延与 SSI 相当,通信速率最高可达 10Mbps 。同时, BISS

协议的数据长度可以根据实际情况做出修改,具有良好的扩展性。

BISS 协议有两种工作模式 [43] ,本文中所设计的工作模式为传感器模式, FPGA 向

编码器发送位置请求指令,编码器则返回相关信息。在传感器模式下, BISS-C 的数据

格式如下图 4-5 所示。主机发送 MA 时钟信号给光栅尺,编码器通过 SLO 数据线串行

BISS-C 数据帧共由八部分组成,分别是“Ack”响应阶段、“Start”位、一位的“0”位、

若干位的位置数据、一位错误位、一位警告位、六位的 CRC 校验码和 “Timeout” 超时结

束阶段。具体的通信请求循环如下所述 [44] :

( 1 )在非位置请求时,时钟信号为高电平,主机读取编码器的 SLO 数据线为高电

平时,则表示编码器已准备就绪。

(

2 )当编码器准备就绪时,主机开始传输固定频率的 MA 时钟信号给光栅尺。

(

3 )编码器在检测到主机发送的 MA 时钟的第二个上升沿时,会将 SLO 线设为低

电平作为响应。

(

4 )编码器通过拉低 SLO 信号线提示主机,当前编码器处于 Ack 应答状态,主

机应及时切换到接收状态。

(

5 )主机将同步于 MA 时钟信号接收编码器传回传数据,其数据帧格式为高位在

前低位在后。

(

6 )当接收完全部数据后,主机将 MA 时钟线拉高。当编码器准备好下一次位置

请求时,编码器则将 SLO 线设为高电平来提示主机,否则保持低电平。

4.2.2 软件模块设计

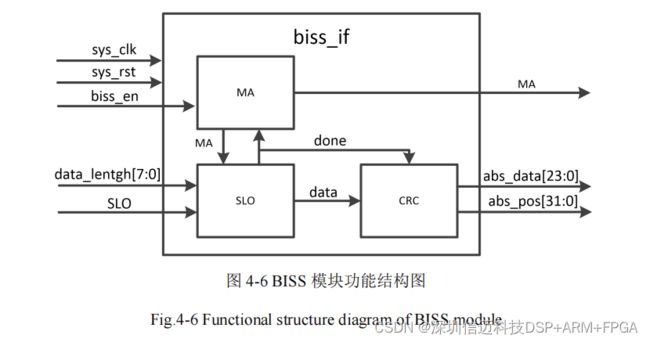

BISS 模块功能结构图如图 4-6 所示,主要由 MA 模块、 SLO 模块和 CRC 模块构成。

模块的信号解释如下:

( 1 ) biss_en

:模块使能信号,用于获取编码器位置信息。

(2) data_length

:编码器数据位宽设置。

(3) SLO

: BISS 协议数据线。

(4) MA

: BISS 协议时钟线。

(5) abs_data

:单圈绝对值,用于圆编码器多圈计数和电角度计算。

(6) abs_pos

:编码器实际总位置数据。

该模块具体工作原理为:首先 FPGA 根据实际光栅尺型号设置位置数据位宽

data_lentgh 数值,该模块满足位置数据位宽长度为 32bit 内的设计需求。通过主控模块

发送使能信号 biss_en 到 MA 模块中, MA 时钟模块开始工作,向光栅尺发送固定频率

的 MA 时钟信号请求获取当前位置值。 FPGA 接收完光栅尺返回的数据后将所其输入

到 CRC 校验模块中进行数据校验,最后将正确的位置数据输出至下一级模块。

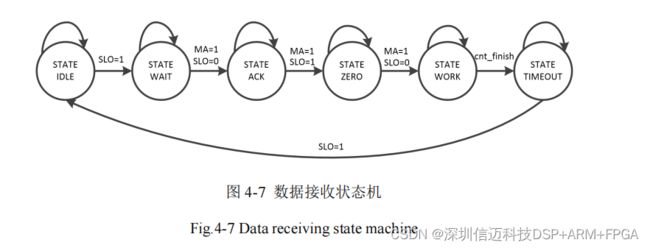

根据 BISS 协议的时序图特点,本文将 SLO 模块接收数据的过程划分为六个状态,

该状态机工作方式如图 4-7 所示。一开始功能模块为空闲状态并且进入等待状态;当

光栅尺拉低 SLO 信号线时进入 Ack 应答状态;当 SLO 从低电平变换成高电平时,状

态机进入 STATE_ZERO 状态;当监测到 SLO 数据线拉低时,模块进入工作状态开始

在实际工程中,数据电平存在毛刺或者亚稳态现象,假如根据 MA 时钟的上升沿

读取当前 SLO 数据线的电平状态,所得到的信号并不可靠。通常情况下,在传输过程

中数据中间位置的电平状态是比较稳定可靠的。因此本文采取的方法为:在中间部分

对 SLO 数据线进行多次采样,并判断哪种电平的数量多,最后将数量多的电平信号值

判赋值给寄存器。具体实施原理如图 4-8 所示,其中 sys_clk 为系统时钟, bps_cnt 为一

个 MA 时钟周期对 SLO 数据线电平的采样数。实际中 MA 时钟频率相比于 FPGA 内部

工作频率来说属于低速时钟,因此可以在一个 MA 时钟周期内进行多次采样。在每一

个 MA 时钟周期中,当检测到 MA 时钟的上升沿时,

bps_cnt 寄存器开始从零计数采样,

然后判断高电平的数量多还是低电平的数量多,最后将累加后电平数量多的一方的值

当 SLO 模块接收完数据后向 MA 模块和 CRC 校验模块返回接收完成信号。 MA 模

块接收到完成信号后 FPGA 将 MA 时钟线拉高, CRC 模块接收到完成信号后将 SLO 模

块传输的数据帧进行 CRC 校验运算。 BISS-C 协议的 CRC 多项式为 G ( x ) x 6 x 1 ,

即校验字段为 1000011 。为了充分发挥 FPGA 并行处理的工作特点,进一步提升工作效

率,本文采用了并行 CRC 校验算法,在一个时钟周期内得出 CRC 校验码,主要代码

其中 d[33:0] 是需要校验的数据, crc_out[5:0] 是 CRC 模块对需要校验的数据进行运

算后得出的结果,而 c[5:0] 的初始值为零,最后将计算结果与所接收的 CRC 校验码进

行匹配。如果二者一致,则表示 SLO 模块正确接收数据,并将正确的位置数据更新至

下一级模块中,否则更新上一次保留的正确数据,并准备发起下一次光栅位置请求。

4.2.3 仿真测试

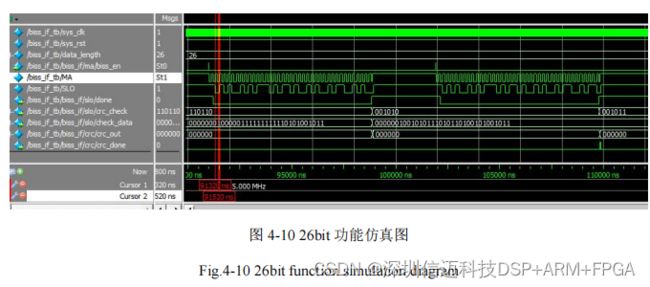

最后编写测试文件对 BISS 模块在 ModelSim 软件进行仿真验证,在实际工程应用

中稳定性占据着重要位置。因此在通信速率方面选用最高 5Mbps ,所以测试文件中模

拟编码器以 5Mbps 的通讯速率向 FPGA 传输数据。本文针对常用的 26bit 和 32bit 位置

数据位宽编码器型号进行测试。

首先对 26bit 位宽型号设置了两组数据如表 4-1 所示,其中第一组和第二组数据仅

仅在 CRC 检验码最后一位不同,而第二组数据则是完全正确的情况。通过这种人为设

置的数据可以测试 BISS 模块接收的两组数据信息是否一致,同时也检测 CRC 校验模

块能否正常工作。需要特别说明的是, BISS-C 协议的 CRC 校验值在编码器内部是先

通过取反再输出给主机的,所以表格中的 CRC 校验值是已经做了取反处理。因此做匹

配校对时, FPGA 应当将计算得出的 CRC 校验值取反再与接收到的值进行比较。其整

图中左侧的时序图时第一组数据,而右侧的是第二组数据。图中 crc_check 为接收

的 CRC 值、 check_data 是需要校验的数据、 done 是数据接收完成信号、 crc_out 是校验

计算得出的 CRC 值、 crc_done 代表校验完成,即接收的数据正确无误。从图中可以看

出,在 data_length 为 26bit 的数据模式下模块接收到 biss_en 使能信号后, FPGA 向编

码器发送频率为 5MHz 的 MA 时钟信号。编码器检测到 MA 时钟信号后通过 SLO 数据

线向主机返回数据,当 FPGA 接收完数据后向 CRC 模块传输接收到的 CRC 校验值和

需求校验的数据,并且发出 done 信号来提示 CRC 模块工作。然后 CRC 模块对需要校

验的数据进行处理,处理完之后跟接收到的 CRC 校验值进行比对,假如两者匹配成功

进一步查看 CRC 校验的细节如图 4-11 所示。图中接收到的 CRC 校验值 crc_check

为 001011 ,而对需要校验的数据经过 CRC 校验后,得到 crc_out 为 110100 。上一节也

说到,编码器的 CRC 校验值是先取反在发送到主机,而校验运算后得到的数据

crc_check 并未取反,因此取反后可知与所接收的 CRC 校验值一致。同时从图中也能看

从上述的两张仿真结果图可知 BISS 模块能够以 5Mbps 的通信速率正常发送 MA 时

钟信号,并且完整接收编码器数据,最后以一个时钟周期完成 CRC 校验运算。因此所

设计的 BISS 模块通过 26bit 模式功能仿真测试。

同理,设置了 32bit 位宽型号的仿真测试,设置的仿真数据如表 4-2 所示,功能仿

真图和 CRC 校验细节图如图 4-12 、 4-13 所示。从图中可以看出所设计的 BISS 模块也

因此,可以得出本文设计的 BISS 模块可以通过更改 data_lentgh 寄存器,能够以

5Mbps 的通信来完整接收 32bit 以内数据位宽的编码器的数据。

4.3 多摩川协议程序设计

4.3.1 多摩川协议数据结构

多摩川协议来自日本的多摩川公司,该多摩川协议采用的是“一问一答”的通信方

式,主机向编码器发送不同的请求指令来获取不同的数据信息 [45] 。它的通信方式与串

口通信一致,并且发送一个字节数据时以固定的 2.5Mbps 传输速率从低位开始传输。

本文只着重介绍多摩川协议读取编码器信息的工作模式。

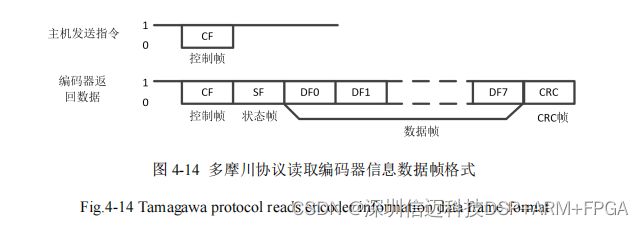

读取编码器信息模式的数据帧格式如图 4-14 所示。其工作原理为:主机通过发送

不同的控制帧指令给编码器来获取相应的信息,然后编码器返回一组数据作为回应,

该组数据由控制帧、状态帧、若干数据帧和 CRC 帧组成。其中根据编码器型号的不同,

控制帧的数据格式如图 4-15 所示,该帧数据主题部分由同步码、控制指令和控制

指令校验位三部分组成。其中同步码是固定不变的,而控制指令及其校验位则有具体

的指令码,如表 4-3 所示。不同的指令码代表不同的功能,编码器返回的数据类型也

不同。例如,用户想获取编码器的单圈值和多圈值,查表 4-4 可知编号为 ID 3 的指令

码对应编码器返回单圈值和多圈值,因此主机可以向编码器发送编码为: 01011000 ,

当编码器接收该编码信息则返回当前编码器单圈值、多圈值和其余附加信息数据。

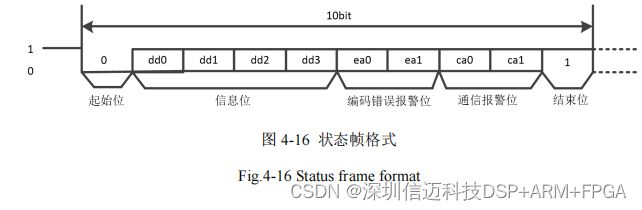

状态帧的数据格式如图 4-16 所示,由信息位、编码错误报警位和通信报警位组成。

不同的编码器型号所对应的信息位信息各有不同,具体含义可查看对应的编码器手册

介绍。如果编码器编码错误或者编码器外部供电出现问题,则编码器错误报警位 ea0

为 1 ,表示当前编码信息错误,而 ea1 为 1 时则编码器多圈值数据错误。通信报警位

ca0 为 1 时,表示所接收的控制帧中的控制指令校验位发生错误,而 ca1 为 1 则表示所

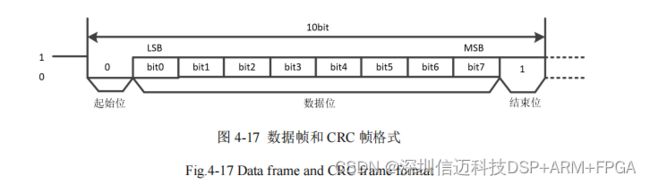

多摩川绝对式编码器最高能够实现 39bit 位宽的高分辨率位置编码数据,其中包括

23bit 的单圈值和 16bit 的多圈值。但是多摩川协议通信一次只发送 8bit 数据,所以发

送完整的位置信息必须将其拆开,再按照一定的排列顺序发送。具体一个字节的数据

由于主机向编码器发送不同的指令码,编码器返回的数据类型也不同。根据编码器

不同的分辨率和指令码,编码器返回的有效数据帧数量也不一样,如只需获取单圈值

或多圈值则返回 3 个字节的有效数据帧,如果需要同时获取单圈值和多圈值则返回 8

表中 ABS 代表单圈绝对码值, ABS0 是单圈位置数据的低八位, ABS1 是单圈位置

数据的中八位位, ABS2 是单圈位置数据的高八位,假如编码器单圈码值位数少于 24bit

时,高位用 0 补齐。同理, ABM 代表多圈绝对码值, ABM0 是圈值数据的低八位, ABM1

是圈值数据的中八位位, ABM2 是圈值数据的高八位,假如编码器多圈码值位数少于

24bit 时,高位用 0 补齐。所以对于高精度的编码器,编码器会将多位的单圈值和多圈

值各拆分为 3 各字节的数据,再从低八位依次发送直至发送完成。