1.Exams/review2015 count1k

module top_module (

input clk,

input reset,

output [9:0] q

);

always @(posedge clk) begin

if (reset) begin

q <= 'd0;

end

else if (q=='d999) begin

q <= 'd0;

end

else begin

q <= q + 'd1;

end

end

endmodule

2.Exams/review2015 shiftcount

module top_module (

input clk,

input shift_ena,

input count_ena,

input data,

output [3:0] q

);

always @(posedge clk) begin

if (shift_ena) begin

q <= {q[2:0],data};

end

else if (count_ena) begin

q <= q - 'd1;

end

else begin

q <= q;

end

end

endmodule

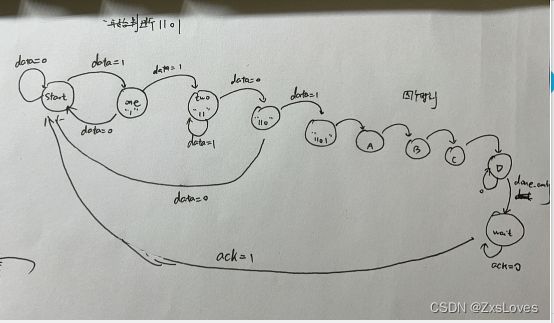

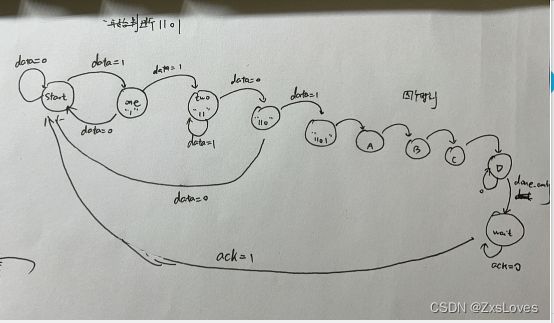

3.Exams/review2015 fsmseq

module top_module (

input clk,

input reset, // Synchronous reset

input data,

output start_shifting);

reg[2:0] state, next_state;

parameter start=0,one=1,two=2,three=3,four=4;

always@(posedge clk) begin

if(reset)

state<=start;

else

state<=next_state;

end

always@(*) begin

case(state)

start:

begin

if(data)

next_state<=one;

else

next_state<=start;

end

one:

begin

if(data)

next_state<=two;

else

next_state<=start;

end

two:

begin

if(data)

next_state<=two;

else

next_state<=three;

end

three:

begin

if(data)

next_state<=four;

else

next_state<=start;

end

four:

begin

next_state<=four;

end

endcase

end

assign start_shifting=(state==four);

endmodule

4.exams/review2015_fsmshift

module top_module (

input clk,

input reset, // Synchronous reset

output shift_ena);

reg[1:0] count;

always@(posedge clk) begin

if(reset)

count<=0;

else

count<=count+1;

end

always@(posedge clk) begin

if(reset)

shift_ena<=1;

else

if(count==3)

shift_ena<=0;

else

shift_ena<=shift_ena;

end

endmodule

5.Exams/review2015 fsm

module top_module (

input clk,

input reset, // Synchronous reset

input data,

output shift_ena,

output counting,

input done_counting,

output done,

input ack );

parameter s=0,

s1=1,

s11=2,

s110=3,

b0=4,

b1=5,

b2=6,

b3=7,

count=8,

wait1=9;

reg[3:0] state,next_state;

always@(posedge clk) begin

if(reset)

state<=s;

else

state<=next_state;

end

always@(*) begin

case(state)

s:

begin

if(data)

next_state<=s1;

else

next_state<=s;

end

s1:

begin

if(data)

next_state<=s11;

else

next_state<=s;

end

s11:

begin

if(data)

next_state<=s11;

else

next_state<=s110;

end

s110:

begin

if(data)

next_state<=b0;

else

next_state<=s;

end

b0:

begin

next_state<=b1;

end

b1:

begin

next_state<=b2;

end

b2:

begin

next_state<=b3;

end

b3:

begin

next_state<=count;

end

count:

begin

if(done_counting)

next_state<=wait1;

else

next_state<=count;

end

wait1:

begin

if(ack)

next_state<=s;

else

next_state<=wait1;

end

endcase

end

assign shift_ena=((state==b0)||(state==b1)||(state==b2)||(state==b3));

assign counting=(state==count);

assign done=(state==wait1);

endmodule

6.Exams/review2015 fancytimer

module top_module (

input clk,

input reset, // Synchronous reset

input data,

output [3:0] count,

output counting,

output done,

input ack );

parameter s=4'd0,s1=4'd1,s11=4'd2,s110=4'd3,b0=4'd4,b1=4'd5,b2=4'd6,b3=4'd7,Count=4'd8,WAIT=4'd9;

reg [3:0] state,next_state;

reg [3:0] temp_in;

reg [15:0] counter;

reg [3:0] a;

wire done_counting;

always @(posedge clk)

begin

if(reset)

state <= s;

else

state <= next_state;

end

always @(posedge clk)

begin

if(reset)

counter <= 16'd0;

else if(next_state == WAIT)

counter <= 16'd0;

else if(next_state == Count)

counter <= counter + 1'b1;

end

always @(*)

begin

if(counter <= 16'd1000)

a = 4'd0;

else if(counter <= 16'd2000)

a = 4'd1;

else if(counter <= 16'd3000)

a = 4'd2;

else if(counter <= 16'd4000)

a = 4'd3;

else if(counter <= 16'd5000)

a = 4'd4;

else if(counter <= 16'd6000)

a = 4'd5;

else if(counter <= 16'd7000)

a = 4'd6;

else if(counter <= 16'd8000)

a = 4'd7;

else if(counter <= 16'd9000)

a = 4'd8;

else if(counter <= 16'd10000)

a = 4'd9;

else if(counter <= 16'd11000)

a = 4'd10;

else if(counter <= 16'd12000)

a = 4'd11;

else if(counter <= 16'd13000)

a = 4'd12;

else if(counter <= 16'd14000)

a = 4'd13;

else if(counter <= 16'd15000)

a = 4'd14;

else

a = 4'd15;

end

assign done_counting = ((state == Count)&(counter == (temp_in + 1)*1000))?1'b1:1'b0;

always @(*)

begin

case(state)

s:next_state = data?s1:s;

s1:next_state = data?s11:s;

s11:next_state = data?s11:s110;

s110:next_state = data?b0:s;

b0:begin next_state = b1;temp_in[3] = data; end

b1:begin next_state = b2;temp_in[2] = data; end

b2:begin next_state = b3;temp_in[1] = data; end

b3:begin next_state = Count;temp_in[0] = data; end

Count:next_state = done_counting?WAIT:Count;

WAIT:next_state = ack?s:WAIT;

endcase

end

assign count = (state == Count)?(temp_in - a):4'd0;

assign counting = (state == Count);

assign done = (state == WAIT);

endmodule

7.Exams/review2015 fsmonehot

module top_module(

input d,

input done_counting,

input ack,

input [9:0] state, // 10-bit one-hot current state

output B3_next,

output S_next,

output S1_next,

output Count_next,

output Wait_next,

output done,

output counting,

output shift_ena

);

parameter S=0, S1=1, S11=2, S110=3, B0=4, B1=5, B2=6, B3=7, Count=8, Wait=9;

assign B3_next = (state[B2]);

assign S_next = (state[S] && ~d) | (state[S1] && ~d) | (state[S110] && ~d) | (state[Wait] && ack);

assign S1_next = (state[S] && d);

assign Count_next = (state[B3] | (state[Count] && ~done_counting));

assign Wait_next = (state[Count] && done_counting) | (state[Wait] && ~ack);

assign done = state[Wait];

assign counting = state[Count];

assign shift_ena = (state[B0] | state[B1] | state[B2] | state[B3]);

endmodule