第五章内存系统(Cortex-M7 Processor)

目录

第五章内存系统

5.1关于内存系统

5.2(Speculative)推测性访问

5.2.1系统设计注意事项

5.3故障处理

5.3.1故障

5.3.2使用模型

5.4内存类型和内存系统行为

5.5AXIM接口

5.5.1AXI属性和事务

5.5.2用于AXIM接口访问的标识符

5.5.3AXI特权信息

5.5.5AXI扩展

5.5.6内存系统对AXI访问的影响

5.5.7AXIM接口传输

LDRB

LDR or LDM that transfers one register

LDM that transfers two registers

STRB

STRH

STR or STM of one register

STM of five registers

Linefills

Cache line write-back (eviction)

Non-cacheable reads

Non-cacheable,Write-Back no Write-Allocate or Write-Through writes

AXI transaction splitting

Normal write merging

第五章内存系统

介绍Cortex-M7处理器内存系统。它包含以下部分:

- 关于内存系统。

- 推测性访问。

- 故障处理。

- 内存类型和内存系统行为。

- AXIM接口。

- AHB外设接口。

- TCM接口。

- AHB从接口。

- L1缓存。

5.1关于内存系统

介绍Cortex-M7处理器内存系统的概况。

Cortex-M7处理器存储系统可以在实现和集成过程中配置。它包括

- 单独的可选指令和数据缓存。

- 可选指令和数据紧密耦合内存(TCM)区域。

- AHB从(AHBS)接口。

- 选配MPU (Memory Protection Unit)。参见第6章内存保护单元。

- MBIST .界面

缓存架构为哈佛,即指令缓存中只能取指令,数据缓存中只能读写数据。

与每个缓存并行的是指令端和数据端都可以访问的专用RAM的两个区域。这些都是TCM的寄存器。

指令TCM (Instruction TCM)使用ITCM接口,数据TCM (Data TCM)使用DOTCM和DITCM两个接口。第1-7页的Cortex-M7功能图显示了这一点。

ITCM接口是64位宽的。DTCM分为两个32位宽接口:DOTCM和DITCM。数据的上32位在DITCM接口上,下32位在DOTCM接口上。

如果该地址位于已启用的TCM区域,则需要对ITCM进行内存访问,以获取指令和传输数据指令。如果可以缓存,则在适当的L1缓存中查找不在外设接口区域中的剩余指令访问和剩余数据访问。内存系统不提供服务的访问通过AXI主(AXIM)接口或AHBP接口传递到连接到处理器的外部内存系统。

Cortex-M7处理器只在内存传输由同一主接口发起的情况下遵守Armv7-M架构参考手册中描述的内存排序限制。如果不使用屏障指令,就不能保证不同接口之间的排序。

处理器支持通过AHBS接口直接访问TCM。该接口为DMA流量到内存提供高带宽,并且可以在处理器的其余部分处于低功耗待机模式时使用,并且内部时钟被禁用。

可选的MPU处理指令和数据存储器访问。MPU负责保护检查、地址访问权限和所有访问的内存属性。其中一些属性可以通过AXIM接口或AHBP接口传递到外部内存系统。

该存储器系统包括用于独占访问的监视器。独占加载和存储指令,例如LDREX和STREX,可以与适当的内存监控一起使用,以提供进程间或处理器间的同步和信号量。有关更多信息,请参阅Arm v7-M架构参考手册。

该处理器专为使用AMBA 4 AXI和amba3的芯片设计而设计AHB-Lite协议。

5.2(Speculative)推测性访问

Cortex-M7处理器执行推测访问以提高性能。Armv7-M架构允许推测访问,系统设计人员不应该假设推测的范围是固定的或明确指定的。

下面的列表描述了可能发生推测访问的几个示例:

请注意

这并不是投机性访问可能发生的情况的全面列表。

- 推测指令提取可以启动到任何正常的、可执行的内存地址。无论获取的指令是否被执行,或者在极少数情况下,内存地址是否包含任何有效的程序指令,都可能发生这种情况。

- 推测数据读取可以被初始化到任何普通、读写或只读内存地址。在一些罕见的情况下,不管是否有任何指令导致数据读取,都会发生这种情况。

- 推测的缓存线路填充可以启动到任何可缓存的内存地址,并且在极少数情况下,无论是否有任何指令导致缓存线路填充。

- 在极少数情况下,针对TCM区域的推测读可以在三个TCM接口中的任何一个上发起,而不管该内存区域映射到哪个TCM接口。

以下列表描述了不发生推测访问的情况:

- 推测指令永远不会对“永不执行”区域中的内存地址进行读取。

- 推测性数据读取永远不会对MPU中标记为不可访问的内存地址进行读取。

- 永远不会对不可缓存的内存地址进行推测式缓存行填充。

- 永远不会对设备或强顺序内存地址进行推测性数据读取和推测性缓存行填充。

- 揣测读取永远不会在AHBP接口上进行。

- 从不进行推测性写入。

请注意

映射到TCM的内存区域总是被视为正常内存,因此总是受到猜测的影响。

5.2.1系统设计注意事项

系统设计者必须确保系统足够健壮,能够处理推测性访问,并确保所有可执行和普通类型的内存区域都可以安全访问。

防止投机访问

推测性访问不会导致任何处理器故障。处理器知道访问是否是推测性的,并且忽略由于推测性访问而由系统发出的任何错误响应。然而,集成处理器的系统无法区分在推测访问和非推测访问之间。因此,系统设计人员需要确保系统足够健壮,能够处理推测性访问,而不管它们是否被发起到意外的内存地址。

或者,如果存在不应该启动投机访问的内存区域,Arm建议您将这些区域设置为具有MPU的所有以下属性:

- 设备或强排序。

- 从未执行。

请注意

映射到TCM的内存区域总是被视为正常内存,因此总是受到猜测的影响。

阻止访问

系统必须确保所有可执行和普通类型的内存区域都可以安全访问。这意味着所有的访问最终都应该完成。

请注意

- 处理器不取消非推测性访问,因此等待访问完成。

- 处理器不能保证投机访问将被取消,因此可能会等待访问完成。

对于任何被认为不安全的地址,Arm建议您要么确保系统返回一个中止,要么通过将这些区域设置为MPU具有以下所有属性来阻止访问:

- 设备或强排序。

- Non-accessible。

- 从未执行。

5.3故障处理

指令获取时可能出现错误,原因如下:

- MPU MemManage。

- 外部轴从机错误(SLVERR)。

- 外部AXI解码错误(DECERR)。

- TCM外部错误。

- 断点和矢量捕获事件。

数据访问出现故障可能有以下原因:

- MPU MemManage。

- 对齐UsageFault。

- 外部轴从机错误(SLVERR)。

- 外部AXI解码错误(DECERR)。

- 来自AHBP端口的外部AHB错误。

- 检查点。

- TCM外部错误。

故障处理的描述见:

- 故障。

- 5-6页的使用模型。

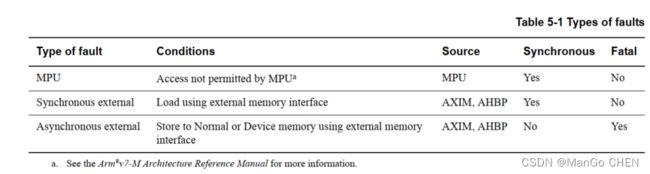

5.3.1故障

可能发生的故障有以下几种:

MPU faults。

外部故障。

调试5-6页上的事件。

5-6页的同步和异步故障。

MPU faults

主控板产生故障的原因多种多样。主控板故障总是同步的,优先于外部故障。如果在TCM之外的访问中出现MPU故障,则不会执行该访问的AXI或AHB事务。

外部故障

通过AXIM接口执行的内存访问或指令获取可以生成两种不同类型的错误响应,从错误(SLVERR)或解码错误(DECERR)。这些错误被称为外部AXI错误,因为它们是由处理器外部的AXI系统生成的。

通过AHBP接口执行的内存访问可以生成单个错误响应。处理器以与来自AXI接口的SLVERR响应相同的方式管理此操作。

在TCM接口上执行内存或指令获取访问可能会产生单个错误响应。处理器以与来自AXI接口的SLVERR响应相同的方式管理此操作。

指令获取和数据加载会产生同步错误。所有存储都会产生异步故障。

请注意

系统中不能处理排他事务的从设备返回OKAY作为对排他读的响应。这也被视为外部错误,处理器的行为就像响应是SLVERR一样。

调试事件

处理器中的调试逻辑可以配置为在指令获取时生成断点或矢量捕获事件,以及在数据访问时生成观察点。如果处理器被软件配置为监视器模式调试,那么当发生这些事件之一或执行BKPT指令时,就会发生故障。有关更多信息,请参见第9章调试。

同步和异步故障

同步故障与异步故障的区别请参见5-5页的“外部故障”。

5.3.2使用模型

介绍处理系统错误的一些方法。如何编程处理器来处理故障取决于处理器和系统的配置,以及您想要实现的目标。

如果发生故障异常,故障处理程序将读取链路寄存器、堆栈中的程序状态寄存器(PSR)和故障状态寄存器中的信息,以确定故障的类型。有些类型的故障对系统是致命的,而其他类型的故障可以修复,并恢复程序执行。例如,MPU后台MemManage可能表示堆栈溢出,并通过分配更多的堆栈和重新编程MPU来纠正这一点。或者,异步外部故障可能表明软件错误意味着对未映射的内存地址发生了存储指令。这种故障对系统或进程来说是致命的,因为没有记录发生错误的地址或引起故障的指令。

表5-1所示的故障类型通常是致命的,因为错误的位置没有记录或错误是不可恢复的。一些被标记为不致命的错误在某些系统中可能是致命的,因为错误的原因已经确定。例如,MPU后台MemManage故障可能表明堆栈溢出,这是可以纠正的,或者它可能表明,由于错误,软件访问了不存在的内存位置,这可能是致命的。可以通过确定错误发生的位置来区分这些情况。

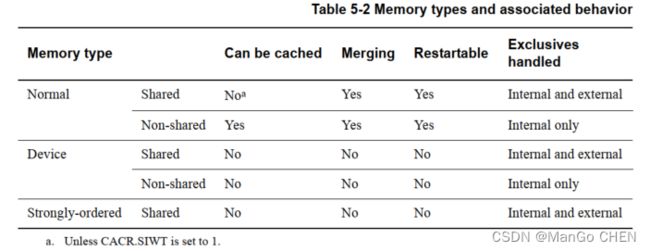

5.4内存类型和内存系统行为

内存系统的行为取决于正在访问的内存的类型属性:

默认情况下,ram中只能缓存普通、非共享内存区域。只有在启用了适当的缓存并且内存类型是可缓存的情况下,才会进行缓存。如果CACR,可以缓存共享可缓存内存区域。SIWT设置为1。

存储缓冲区可以将任何存储合并到普通内存,如果它们不是来自访问标记为共享的内存区域的存储独占指令。更多信息请参见第5-42页的存储缓冲区。

只有非缓存的共享独占事务在外部接口上被标记为独占。如果CACR,加载和存储共享可缓存内存区域的独占指令不会导致在外部接口上标记为独占的任何访问。SIWT设置为1。

只有普通内存被认为是可重新启动的,也就是说,一个多字传输可以因为中断而中途放弃,在中断被处理后重新启动。有关中断行为的更多信息,请参见第2-10页的异常处理。

对于非共享内存的独占访问,只更新和检查内部独占监视器。使用内部监视器检查对共享内存的独占访问,必要时还使用使用外部内存接口AXIM或AHBP的外部监视器检查。

表5-2总结了处理器内存类型和相关行为。

5.5AXIM接口

本节描述AXIM接口。AXIM接口是连接到外部内存系统的单个64位宽接口。它用于:

- 指令获取。

- 数据缓存行填充和退出。

- Non-cacheable普通类型的内存数据访问。

- 设备和强顺序类型的数据访问,通常是对外设的访问。

AXIM接口符合Arm AMBA AXI和ACE协议规范中描述的AXI4标准。在AXI标准中,AXIM接口使用许多扩展信号来指示内部内存属性和请求源。请参阅第5-12页的AXI扩展。

AXIM接口可以与处理器相同的频率运行,也可以以较低的同步频率运行。

请注意

本节中对AXI从站的引用是指连接到处理器AXIM接口的外部系统中的AXI从站。

以下部分描述了AXIM接口的属性,并提供了有关生成的突发类型的信息:

- 第5-9页的AXI属性和事务。

- 第5-11页中介绍的AXIM接口访问的标识符。

- AXI扩展在第5-12页。

- 内存系统对AXI访问的影响见第5-13页。

请注意

有关推测访问的更多信息,请参见第5-3页的推测访问。

5.5.1AXI属性和事务

表5-3显示了处理器配置L1数据缓存时AXIM接口的AXI属性和事务。这用于具有高内存带宽并支持多个未完成事务的本机AXI系统,也称为高性能AXIM接口。

只能生成所有可能的AXI事务的一个子集。这些都是:

- 对于Normal,可缓存内存:

- WRAP4 64位读取,用于加载和回写-分配存储行填充和指令行填充。

- INCR4 64位写,用于驱逐。

- INCR N (N:1-4) 64位,用于写传输,用于合并的单个write - through或write - back,没有write - allocate存储。

- INCR N (N:1-4) 64位,用于读传输、禁用数据缓存时的加载或禁用指令缓存时的指令读取。

- 对于普通、不可缓存内存:

- INCR N (N:1-4) 64位读传输,单独加载和多次加载。

- INCR N (N:1-4) 64位,用于写传输,用于合并的单个存储和存储倍数。

- INCR N (N:1-4) 64位用于读传输,用于指令读取。

- INCR 1 8位、16位和32位的独占读写,用于共享独占。

- 对于强顺序存储器或设备存储器:

- INCR 1 8位,16位和32位读写,用于单独的加载和存储。

- INCR 1 32位用于读传输,加载倍数。

- INCR N (N:1-2) 32位,用于写传输,用于存储倍数。

- INCR 1 8位、16位和32位的独占读写,用于共享独占。

- 不使用固定爆发。

- 写入突发到普通内存可以使用以下优化:

- 整个节拍没有设置闪光灯。

- 每拍不连续频闪。

这些在AXI上是允许的,但对桥接AHB有影响。

有关用于不同事务的id的更多信息,请参见第5-11页的AXIM接口访问标识符。

表5-4显示了处理器未配置为包含L1数据缓存时的AXI属性和事务。也就是说,如果您想在低成本的AXI系统中使用它,或者桥接到具有低带宽内存系统的AHB,就像在片外内存系统上一样。

只能生成所有可能的AXI事务的一个子集。这些都是:

- 对于正常记忆:

- WRAP4 64位读传输,用于包含指令缓存的指令行填充。

- INCR N (N:1-4) 64位读传输,单个负载和负载倍数。

- INCRN (N:1-4) 64位,用于写传输,用于合并的单个存储和存储倍数。

- INCR N (N:1-4) 64位读传输,用于不可缓存指令读取或所有指令读取没有指令缓存。

- INCR 1 8位、16位和32位的独占读写,用于共享独占。

- 对于强顺序存储器或设备存储器:

- INCR 1 8位,16位和32位读写,用于单独的加载和存储。

- INCR 1 32位用于读传输,加载倍数。

- INCR N (N:1-2) 32位,用于写传输,用于存储倍数。

- INCR 1 8位、16位和32位的独占读写,用于共享独占。

- 不使用固定爆发。

- 写入突发到普通内存可以使用以下优化:

- 整个节拍没有设置闪光灯。

- 每拍不连续频闪。

这在AXIM接口上是允许的,但对桥接到AHB有影响。

有关用于不同事务的id的更多信息,请参阅AXIM接口访问的标识符。

5.5.2用于AXIM接口访问的标识符

下面的ID值用于读写通道,以及在AXIM接口上的write - allocate内存访问:

- 读取通道,ARID[2:0], RID[2:0]:

0 b000普通不可缓存读、设备读和强顺序读。

0 b011 0 b010数据缓存行填充。

0 b100指令获取。

- 写通道,AWID[1:0], WID[1:0], BID[1:0]:

0 b00普通的,不可缓存的写,所有共享的独占写,例如来自STREX。

0 b01普通可缓存写,Write-Through和Write-Back, Non Write-Allocate内存。

b10 0设备和强顺序写。

0 b11清除到普通可缓存回写内存。

WID不是amba4axi所需的信号。它包括与amba3axi系统的兼容性。

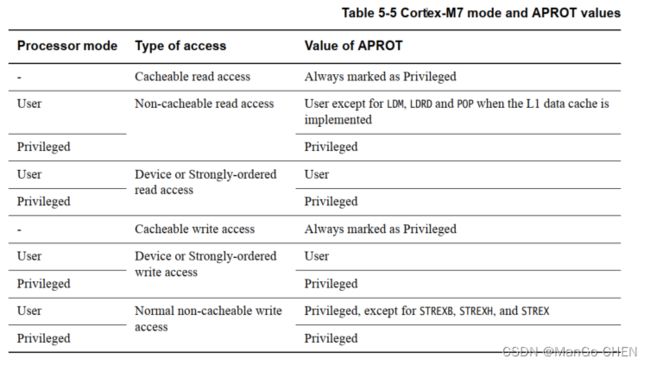

5.5.3AXI特权信息

AXI提供了关于ARPROT和AWPROT信号访问权限级别的信息。但是,当访问可能被缓存或合并在一起时,生成的事务可以同时包含特权数据和用户数据。如果发生这种情况,Cortex-M7处理器将事务标记为特权事务,即使它是由用户进程发起的。

Cortex-M7模式和APROT值如表5-5所示。

5.5.5AXI扩展

AXIM接口使用ARCACHE和AWCACHE AXI信号和ARSHARE, AWSHARE, ARINNER和AWINNER扩展信号来指示传输的内存属性,由MPU返回:

- 主接口的ARCACHE和AWCACHE由内存类型和外部区域属性生成。

- ARINNER和AWINNER由内存类型和内部区域属性生成。

- 对于共享内存区域的事务,断言ARSHARE和AWSHARE。

除了这些属性扩展信号之外,AXIM接口还包括以下信号:

AWMASTER和ARMASTER

显示内存请求的来源。设置为时:

0 该请求是由运行在处理器上的软件生成的。

1 该请求是由AHB debug (AHBD)接口上的调试请求生成的。

AWSPARSE AWSPARSE是写地址通道信号组的一部分,表明突发使用稀疏字节写频闪,也就是说,写突发的一些节拍不包含数据。您可以使用此信号来优化桥接amba4axi协议到AHB协议的系统。

请参阅Arm AMBA AXI和ACE协议规范,了解所有协议的有效编码AxCACHE和AxINNER 信号。

5.5.6内存系统对AXI访问的影响

被访问的内存的属性可以影响AXI访问。内存系统可以缓存任何被标记为:

- 可缓存,回写,读分配,写分配,不可共享。

- 可缓存,回写,只读分配,不可共享。

- 可缓存,透写,只读分配,不可共享。

然而,设备和强顺序内存总是不可缓存的。此外,对Device或强排序内存的任何未对齐访问都会生成对齐UsageFault,因此不会导致任何AXI传输。这意味着本章给出的访问示例永远不会显示对设备或强顺序内存的非对齐访问。

请注意

标记为非可缓存正常的内存区域不能用于访问系统中的读敏感外设。这是因为如果原始加载指令被中断,那么从处理器读取到这些区域的事务可以重复多次。

5.5.7AXIM接口传输

处理器符合Arm* AMBA* AXI和ACE协议规范,但它不生成规范允许的所有AXI事务类型。本节描述AXIM接口不生成的AXI事务的类型。

如果您正在设计一个仅与Cortex-M7处理器一起工作的AXI从站,并且在您的系统中没有其他AXI主站,那么您可以利用这些限制和接口属性来简化从站,如第5-9页的表5-3所示。

本节还包含一些表,这些表显示了处理器生成的AXI突发类型的一些示例。但是,这里没有显示特定类型的事务并不意味着处理器不生成这样的事务。

请注意

连接到AXIM接口的AXI从设备必须能够处理Arm* AMBA* AXI和ACE协议规范允许的各种事务,除非在本章中有明确声明不生成此类事务。您不能从给出的示例表中推断出任何额外的限制。

将指令加载和存储到不可缓存内存可能不会导致AXI传输,因为数据可能从内部存储数据缓冲区检索或合并到内部存储数据缓冲区中。例外情况是加载或存储到强排序或设备内存。这些总是导致AXI传输。请参阅第5-15页的强排序和设备事务。

对AXI传输的限制在第5-15页描述了对AXIM接口生成的传输类型的限制。如果处理器上电,缓冲的写响应和读数据通道就绪信号(BREADY和RREADY)总是被断言。当处理器进入休眠或关闭模式时,它们被解除断言。您不能对AXI握手信号做出任何其他假设,除非它们符合Arm AMBA°AXI和ACE协议规范。

以下部分给出了由AXIM接口生成的传输的示例:

- 对AXI传输的限制见第5-15页。

- 第5-15页的强订单和设备交易。

- 在第5-20页填写。

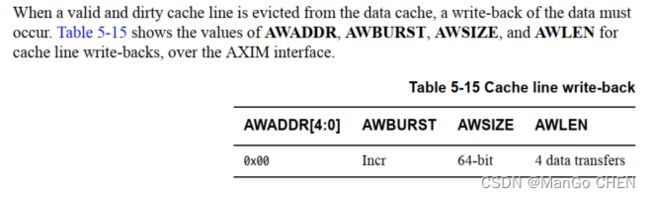

- 第5-20页的缓存线回写(退出)。

- 5-20页上的不可缓存读取。

- 不可缓存,回写,无写- allocate或write - through写。

- AXI事务分割在第5-21页。

- 5-22页的正常写合并。

AXI传输的寄存器

AXIM接口对它生成的AXI事务应用以下限制:

- 突发传输的数据不会超过32字节。

- 突发长度不超过4次传输。

- 强顺序或设备写突发的最大长度是两次传输。

- 强顺序或设备读取总是一次传输。

- 任何事务都不会越过内存中的32字节边界。

- 参见第5-21页的AXI事务拆分。

- 固定爆发从不使用。

- 写地址通道总是发出INCR类型的突发,而不会发出WRAP或FIXED。

- WRAP类型的读突发,参见第5-20页的Linefills:

- 仅用于行填充(读取)可缓存的普通内存。

- 总大小为64位,长度为4次传输。

- 总是有一个64位对齐的起始地址。

- 如果传输大小是8位或16位,那么突发长度总是一次传输。

- 传输大小永远不会超过64位,因为它是64位的AXI总线。

- 指令读取,由ARPROT[2]识别,总是64位传输大小,并且从不锁定或排他。

- 到设备和强排序内存的事务总是到与传输大小对齐的地址。请参阅强排序事务和设备事务。

- 排他访问总是指向与传输大小对齐的地址。

- 只有对共享内存的独占访问才会导致对AXIM(由ARLOCK和AWLOCK标识)的独占访问。对非共享内存的独占访问在总线上被标记为非独占访问。

强排序和设备事务

从强顺序存储器或设备存储器加载或存储指令总是生成与该指令所暗示的大小相同的AXI事务。所有使用LDM、STM、LDRD或STRD指令对强排序或设备内存的访问都以32位传输的方式进行。

LDRB

表5-6所示为存储在强顺序存储器或设备存储器中0 ~ 7字节的LDRB的ARADDR、ARBURST、ARSIZE和ARLEN的值。

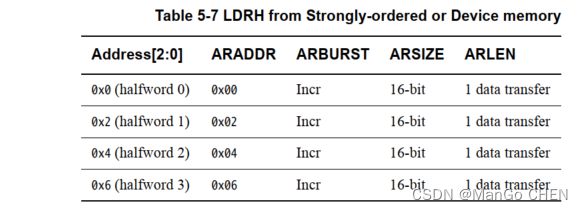

LDRH

表5-7显示了半字0-3的LDRH的ARADDR、ARBURST、ARSIZE和ARLEN的值。

请注意

从强排序或设备内存地址0x1、0x3、0x5或0x7加载半字会生成对齐UsageFault。

LDR or LDM that transfers one register

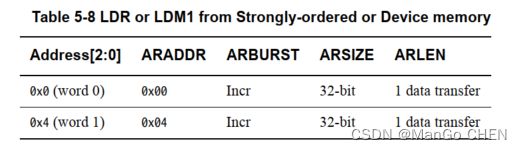

表5-8给出了在强顺序内存或设备内存中传输一个寄存器(LDMI)的LDR或LDM的ARADDR、ARBURST、ARSIZE和ARLEN的值。

请注意

从强排序或设备内存地址0x1、0x2、0x3、Ox5、0x6或0x7加载一个字会产生对齐UsageFault。

LDM that transfers two registers

LDM的ARADDR、ARBURST、ARSIZE和ARLEN的取值如表5-9所示在强顺序或设备内存中传输两个寄存器(一个LDM2)。

请注意

来自地址0x1、0x2、0x3、0x5、0x6、0x7、0x9、0xA、0xB、0xD、0xE或0xF的加载倍数会产生对齐UsageFault。

STRB

表5-10显示了通过AXIM接口的STRB到strong -ordered或Device memory的AWADDR、AWBURST、AWSIZE、AWLEN和WSTRB的值。

STRH

AWADDR、AWBURST、AWSIZE、AWLEN、WSTRB的取值如表5-11所示通过AXIM接口到强顺序存储器或设备存储器的STRH。

STR or STM of one register

STM of five registers

Linefills

Cache line write-back (eviction)

Non-cacheable reads

访问不可缓存普通内存的加载指令生成的AXI突发不一定与指令所暗示的大小或长度相同。此外,如果要读取的数据包含在存储缓冲区中,则该指令可能根本不会生成AXI读事务。

Non-cacheable,Write-Back no Write-Allocate or Write-Through writes

将指令存储到Non-cacheable, Write-Back no - Write-Allocate Cacheable和Write-Through可缓存内存生成不一定相同大小的AXI突发或者是指令所暗示的长度。AXIM接口断言字节通道频闪,WSTRB[7:0],以确保只更新由指令写入的字节。

本节中的表给出了可能导致的AXI事务类型的示例各种存储指令,访问普通内存中的各种地址。它们是提供的仅作为示例,并不是对AXI事务的详尽描述。根据处理器的状态,访问的时间,实际产生的突发可能有即使对于相同的指令,其大小和长度也与所示示例不同。

此外,对普通内存的写操作可以合并以创建更复杂的AXI事务。参见第5-22页的正常写合并示例。

AXI transaction splitting

处理器在访问跨缓存线边界(即32字节边界)的地址时拆分AXI爆发。跨越一个或两个32字节边界访问内存的指令分别生成两个或三个AXI爆发。下面的例子展示了这种行为。它们仅作为示例提供,并不是对AXI事务的详尽描述。根据处理器的状态和访问的时间,即使对于相同的指令,实际生成的突发也可能具有与所示示例不同的大小和长度。

例如,LDMIA R10, {R0-R5}从非可缓存的普通内存中加载6个单词。这条指令生成的AXI事务的数量取决于基址R10:

- 如果所有六个字都在同一缓存行中,则存在一个AXI事务。例如,对于LDMIA R10, {R0-R5},其中R10=0x1008,接口可能会产生三个64位读传输的突发,如表5-18所示。

- 如果数据来自两个缓存行,那么就有两个AXI事务。例如,对于LDMIA R10, {R0-R5] with R10=0x1010,接口可能产生两个64位读的突发事件,也可能产生单个64位读的突发事件,如表5-19所示。

- ARADDR可能的取值如表5-20所示。ARBURST。ARSIZE。和ARLEN用于LDR到不可缓存的普通内存,它跨越缓存线边界。

表5-21显示了从STRH到非缓存的普通内存跨越缓存线边界的AWADDR、AWBURST、AWSIZE、AWLEN和WSTRB的可能值。

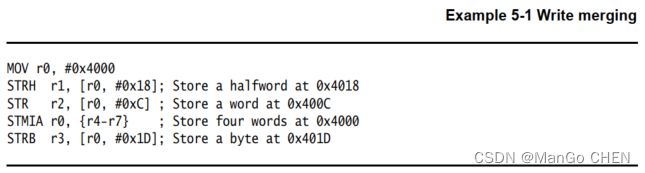

Normal write merging

对不可缓存、回写、不分配缓存或透写缓存的存储指令可能不会导致AXI传输,因为存储数据合并在内部缓冲区中。

存储缓冲区可以检测到,对于可透写可缓存或不可缓存的普通内存,当它包含多个对同一缓存行的写请求时。这意味着它可以将来自多个指令的数据合并到单个写突发中,以提高AXI接口的效率。如果AXIM接收到几个不形成单个连续突发的写请求,它可以选择输出单个突发,对于没有任何数据的字节,WSTRB信号为低电平。对于普通内存的写访问,如果没有地址依赖关系,存储区可以乱序执行写操作。它可以这样做,以最好地利用其合并访问的能力。例5-1中的指令顺序显示了写操作的归并。

表5-22显示了地址0x4000的内存被标记为强顺序内存或设备类型内存时产生的AWADDR、AWBURST、AWSIZE、AWLEN和WSTRB的值。

在例5-1中,每个存储指令产生一个与该指令写入的数据大小相同的AXI突发。表5-23显示了将同一内存标记为Non-cacheable Normal或Write-Through Cacheable时可能产生的事务。

在这个例子中:

- 存储缓冲区将STRB和STRH写入合并到一个缓冲区项中,因此是一个AXI传输,即突发中的第四个。

- 占用三个缓冲区条目的写操作被合并到一个包含四个传输的单个AXI突发中。

- STR指令生成的写操作没有发生,因为它被STM指令覆盖了。

- 写传输发生了与原始程序顺序不一致的情况。

第5-23页表5-23所示的事务显示了这种行为。它们仅作为示例提供,并不是对AXI事务的详尽描述。根据处理器的状态和访问的时间,即使对于相同的指令,实际生成的突发也可能具有与所示示例不同的大小和长度。

如果将相同的内存标记为回写可缓存,并且将地址分配到缓存行中,则在退出缓存行并执行回写事务之前不会发生AXI写事务。参见第5-20页的缓存线回写(退出)。