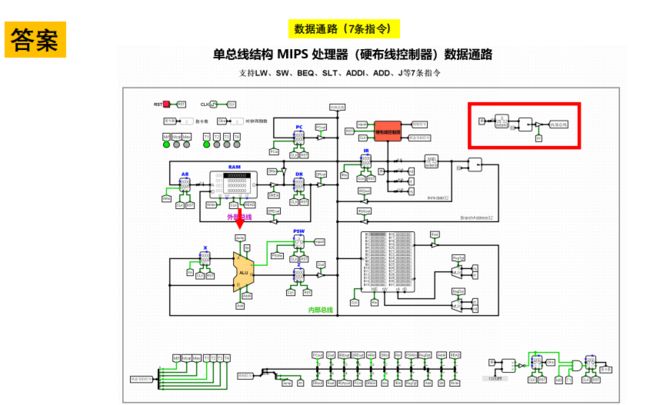

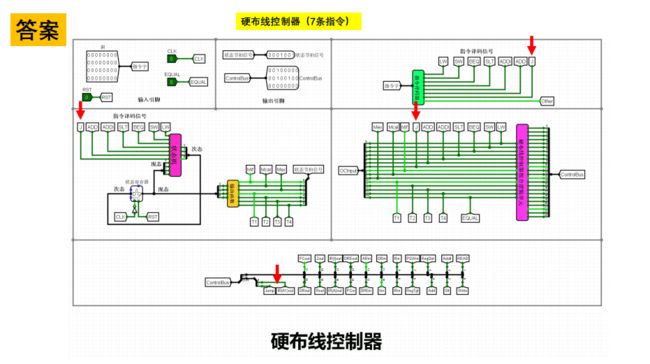

新增ADD指令+J指令,单总线结构 MIPS 处理器:微程序控制器+硬布线控制器

【如果需要circ文件,可以点赞+收藏,私信我~】

一、新增ADD指令:

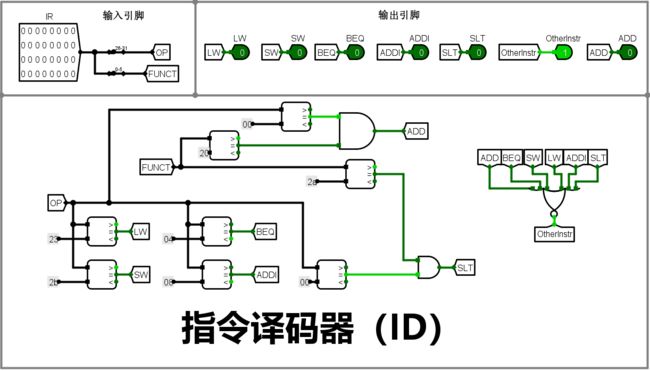

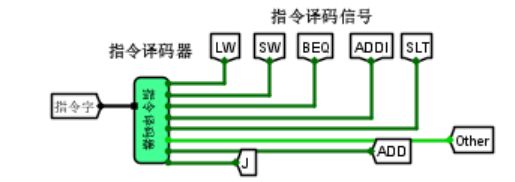

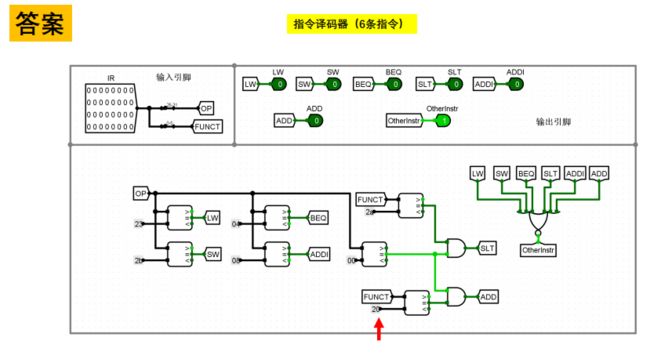

1、如下图是新增ADD后的指令译码器:

相信很多童鞋会在这步卡住,认为ADD的OP码为000000,便只更改了这一处。

殊不知对于R型指令(ADD),还需要更改FUNCT码,而ADD的FUNCT码为100000。

只有当OP码和FUNCT码同时成立时才执行ADD指令。

因此修改方式是:将OP码与000000相比较,将FUNCT码与200000相比较,因为同时成立在执行ADD,因此将这两道信号进行“与”操作,因此用与门进行连接。

2、如下图是微程序自动生成add指令(空表):

控制信号根据课本上填写,需要注意的是下址字段需要填写。

对应的下址字段是第二列微地址+1,第27条微地址,下址字段为0(原因是下址字段指示了下一条指令的微地址,例如:第25条指令的下一条指令是第26条,因此下址字段填写的是26,而27条指令是最后一条指令,要返回第一条0号指令,因此下址字段填写0)。

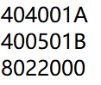

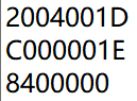

所获得的3条指令如下图:

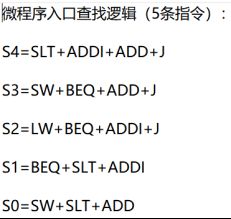

3、最后修改微程序的入口查找逻辑,这个比较简单,不过多赘述:

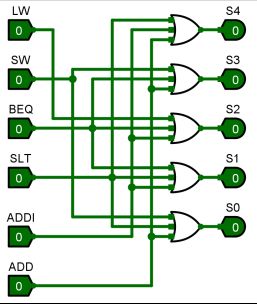

最终的微程序入口查找逻辑如下图所示:

二、新增J指令:

先稍微解释一下J指令要实现的功能:第一步:取出(PC+4)的高4位,第二步:取出26位的立即数,然后将立即数左移2位,获得28位的二进制数。第三步:将第一、二步获得的结果拼接,得到一个32位的地址(至于为什么要是32位的地址,是因为单总线MIPS处理器采用的是32位的地址)。

如下图就是J指令的功能描述:

个人感觉新增J指令比较难的部分是在微指令自动生成逻辑上,课本上并没有直接给出J指令的微指令,因此需要稍加思考和分析。

首先J指令的执行分为三个周期:

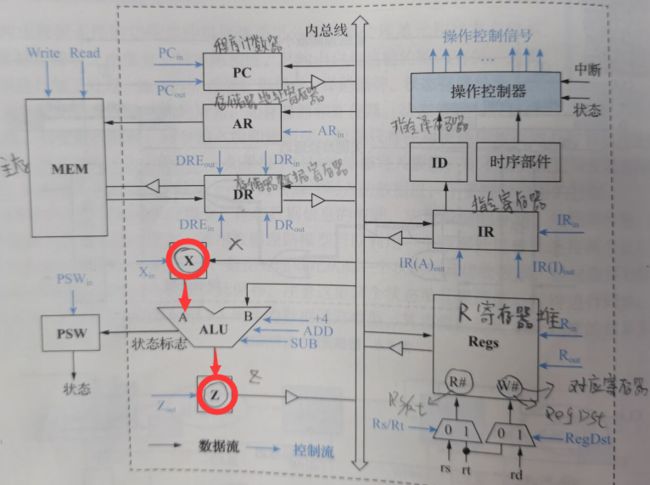

第1个周期:从PC(程序计数器)中取出指令的PC值(PCout),然后将取出的PC值存入X寄存器(Xin)。(至于为什么存入X寄存器,因为X寄存器是作为ALU运算的一个数据来源,简而言之就是方便后续计算)。

第二个周期:将立即数imm26从指令寄存器IR中引出,因为已要求需要新增一个控制信号,所以用Imm来表示。同时完成拼接运算,注意到拼接运算包含了左移2位,题目要求只增加一个控制信号,所以用Alu来表示。

![]()

![]()

第三个周期:将拼接的结果,输出到内总线上(Zout)(至于这里为什么用Z寄存器,因为如上图所示,Z寄存器存储了ALU运算的结果,需要注意的是Z寄存器没有输入控制,因此每个时钟都会自动锁存新值。同时需要理解Zout,是由寄存器向内总线输出数据,这个out是相对寄存器自身而言的!)。然后PC接收新的地址,作为将要执行指令的字节地址。

可能有童鞋会有疑惑,为什么没有用到寄存器AR和IR,因为AR通常用来保存CPU访问主存的单元地址,IR则是用于保存从主存中取出的指令字,而在这里并没有访问主存,如果访问AR和IR反而拖慢了程序的执行。

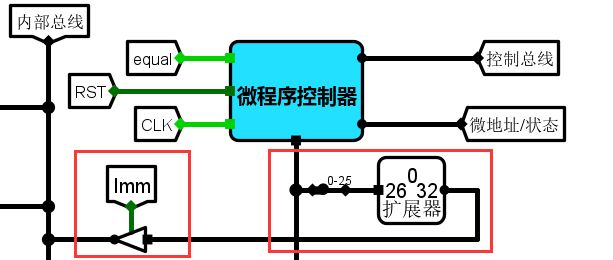

新增2个控制信号Imm和J

获取指令字的低26位,如果Imm为1,三态门打开,则将26位立即数传入总线。

也可以用如下修改方法:

修改Alu:增加J的输入引脚和隧道,优先编码器中新增的J隧道控制MUX的第4路,第4路用于拼接运算:具体原理是:获取Y的整体数据左移2位后得到的低28位(立即数),获取X(存储PC值)的数据的高4位,再利用分线器将低28位和高4位进行拼接,成为32位的地址。

如下图,在数据通路要修改ALU运算器,新增A端口的J指令:

分别填入J指令三个周期的控制信号,将指令十六进制填入微指令集合,装入控制存储器

J型指令OP码为000010,十六进制02,在指令译码器(ID)的输出引脚增加J指令

修改微程序控制器,新增J型指令的指令译码信号,如下图:

接下来修改入口查找逻辑:按照指导填写表格,注意ADD指令占3个周期(25~27),J指令同样占3个周期(28~30),将表达式输入组合电路逻辑分析:

如下图是自动生成的入口查找逻辑,支持7条指令:

修改微程序控制器,在微程序入口查找逻辑输入端增加J型指令,如下图

修改控制存储器中的指令长度为32位,修改分线器位宽和端口数为32位,新增了2位控制信号,控制信号共计24个。

下图是程序运行的结果:

Test3:

sort_sum_mips_bus.hex:

兄弟们,以上就是我计算机组成原理必做实验的答案,看完是不是应该点个赞收藏一下呢!

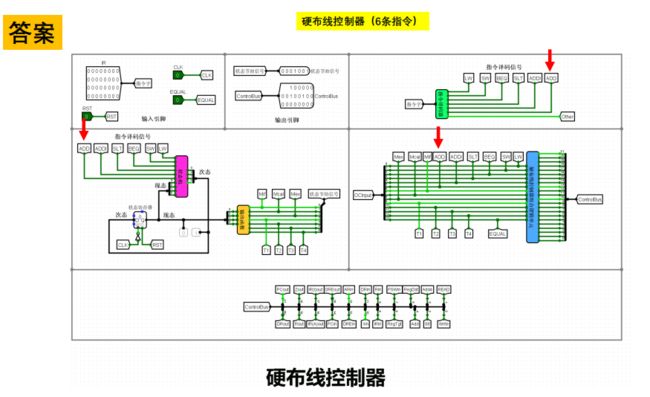

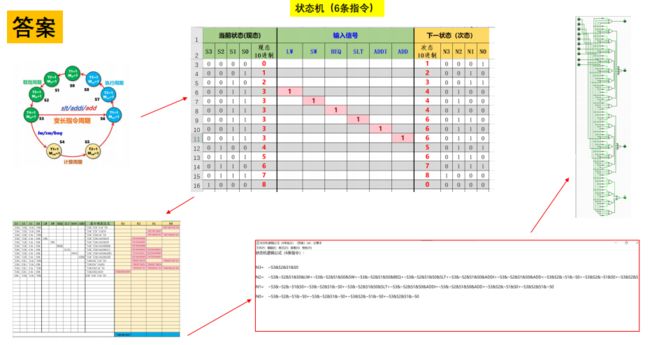

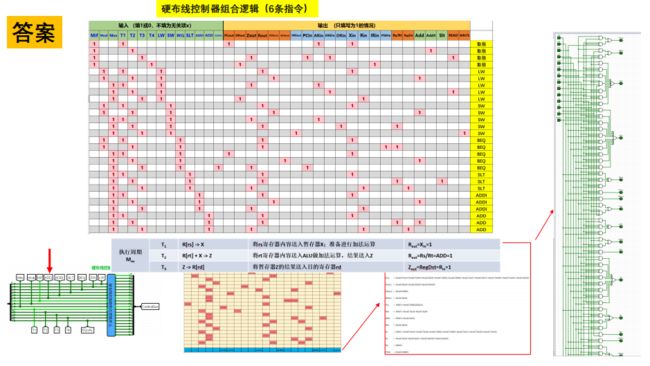

三、单总线结构MIPS处理器(硬布线控制器)(新增ADD指令)

四、单总线结构MIPS处理器(硬布线控制器)(新增J指令)

【如果需要circ文件,点赞+收藏,私信我~】