PCIE系统标准体系结构解读(九):PCIe配置

1.12 PCIe配置

1.12.1 配置概述

系统首次启动时,配置软件还没有扫描过PCIe结构,因而不知道机器的拓扑结构。配置软件唯一知道的是在根联合体内存在着主机/PCI桥,总线0直连到该桥的下游。由于还没有扫描过总线0,因此系统不知道在根联合体上存在着多少个PCIe端口。扫描PCIe结构以找出其拓扑的进程称为枚举(enumeration)。

1.12.2 每种功能实现一组配置寄存器

当处理器执行软件命令时,根联合体会发起配置事务来读或写某种功能的配置寄存器。通过访问这些寄存器可以发现某种功能是否存在,以及对它进行配置,以便进行正常的操作。处了内存、IO和消息空间外,PCIe还定义了一块专用的配置空间,该配置空间要分配给每一种功能,以便实现它的配置寄存器。

PCI兼容空间占据4KB功能配置空间的前256个字节(即64个双字),它包含着该功能的PCI兼容配置寄存器。该区域可用如下两种机制访问:PCI配置访问机制;PCIe增强配置机制。

PCI兼容空间的前16个双字构成了它的头,而后48个双字保留给具有专用功能的配置寄存器及PCI新功能(PCI New Capability)寄存器。强制要求每个PCIe功能都必须在该区域内实现PCIe功能结构。

功能配置空间中的后3840个字节(960个双字)是PCIe扩展配置空间,它用于实现可选的PCIe扩展功能(PCIe Extended Capability)寄存器。包括高级错误报告功能(Advanced Error Reporting Capability)寄存器组;虚拟信道功能(Virtual Channel Capability)寄存器组;设备序列号功能(Device Serial Number Capability)寄存器组;功率预算功能(Power Budgeting Capability)寄存器组。

1.12.3 PCIe枚举

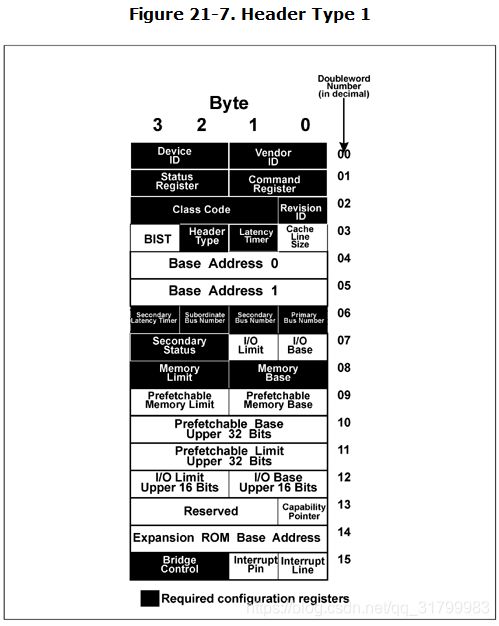

枚举软件依次读取每台设备中功能0的厂商ID,当返回一个不为全F的值时表明设备存在,然后读取头(Header)寄存器中的头类型(Head Type)字段,确定是桥或端点设备或其它类型,以及单功能/多功能设备。

1.12.4 PCI兼容配置寄存器

以下只针对Type0的非桥设备进行说明。

1.12.4.1 概述

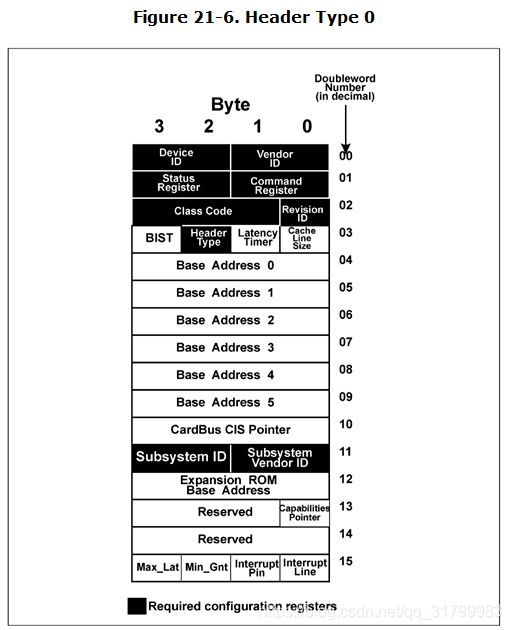

下图展示了功能头区域的格式,标位黑色的寄存器必须实现,这种格式被定义为头类型0。头中的这些寄存器常用于以某种通用的方式识别设备、控制其功能和判断其状况等。在该空间中,余下的48个双字专门用作设备专用寄存器。

1.12.4.2 兼容PCI的头类型0寄存器

在PCI和PCIe中,实现和用法完全相同的头类型0 PCI配置寄存器有:

厂商ID寄存器(Vecdor ID register);

设备ID寄存器(Device ID register);

修订版ID寄存器(Revision ID register);

类代码寄存器(Class Code register);

子系统厂商ID寄存器(Subsystem Vendor ID register);

子系统ID寄存器(Subsystem ID register);

头类型寄存器(Header Type register);

BIST寄存器;

功能指针寄存器(Capabilities Pointer register);

CardBus CIS指针寄存器(CardBus CIS Pointer register);

扩展ROM机制寄存器(Expansion ROM Base Address register)。

1.12.4.3 与PCI不兼容的头类型0寄存器

非桥PCIe功能中,定义在该功能的PCI兼容配置空间之中的下述配置寄存器,不同于PCI规范所定义的相应寄存器:

命令寄存器(Command Register);

状况寄存器(Status Register);

缓存行大小寄存器(Cache Line Size Register);

主延迟定时器寄存器(Master Latency Timer Register);

中断线寄存器(Interrupt Line Register);

中断引脚寄存器(Interrupt Pin Register);

基址寄存器(Base Address Register);

Min_Gnt/Max_Lat寄存器。

1.12.4.4 用于识别设备驱动程序的寄存器

操作系统综合利用下列强制寄存器来确定为设备加载何种驱动:

厂商ID;

设备ID;

修订版ID;

类代码;

系统厂商ID;

子系统ID。

① 厂商ID寄存器

这个寄存器属于PCI兼容寄存器,必须强制实现。16bit的寄存器用于识别该功能的制造商是谁。硬连线在这个只读寄存器中的值由一个控制号码发行的中心机构(PCI-SIG)授予。值FFFFh被保留,当试图从一个不存在功能的配置寄存器中执行配置读操作时,主机/PCI桥必须返回该值。在PCI和PCI-X中,这种读取尝试会导致主异常中断(Master Abort),而在PCIe中会返回UR(不受支持的请求)完成状况。不论哪种情况,桥都必须返回一个值为FFFFh的厂商ID。

②设备ID寄存器

这个寄存器属于PCI兼容寄存器,要求强制实现。它的值(16bits)由功能制造商指定,用于确定功能的类型。在与厂商ID或者修订版ID联合使用时,设备ID用于确定该功能的功能专用驱动程序。

③修订版ID寄存器

这个寄存器属于PCI兼容寄存器,要求强制实现。它的值(8bits)由功能制造商指定,用于确定该功能的修订版本号。如果制造商提供了修订版专用驱动程序,就很容易保证操作系统加载正确的驱动程序。

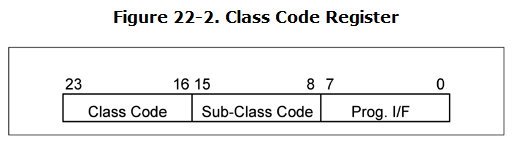

④类代码寄存器

这个寄存器属于PCI兼容寄存器,要求强制实现。如下图,它是个24bits的只读存储器,分为3个区域:基类、子类和编程接口。用于确定该功能的基本功能和功能更为明确的子类,以及在某些情况下的寄存器专用编程接口。

高字节用于定义该功能的基类;

中间字节用于定义基类中的子类;

低字节用于定义编程接口。

下表列出了当前新定义的基类代码,对虚度基类/子类而言,编程解扣子解被硬连线成返回0(无意义)。但对某些类而言是有意义的。

| 类 |

说明 |

| 00h |

在定义类代码前建立的功能(PCI2.0前) |

| 01h |

海量存储控制器 |

| 02h |

网络控制器 |

| 03h |

显示控制器 |

| 04h |

多媒体设备 |

| 05h |

存储器控制器 |

| 06h |

桥设备 |

| 07h |

简单的通信控制器 |

| 08h |

基本的系统外围设备 |

| 09h |

输入设备 |

| 0ah |

坞站 |

| 0bh |

处理器 |

| 0ch |

串行总线控制器 |

| 0dh |

无限控制器 |

| 0eh |

智能IO控制器 |

| 0fh |

卫星通信控制器 |

| 10h |

加密/解密控制器 |

| 11h |

数据获取和信号处理控制器 |

| 12h~feh |

保留 |

| ffh |

不舍和任何定义类代码的设备 |

当操作系统试图与类驱动程序一起工作的功能时,类代码寄存器很有用。操作系统能找出一个具有基类代码和子类代码的功能,驱动程序就能与该功能一起工作。类驱动程序比制造商提供的仅与某个特定功能一起工作的驱动程序更具灵活性。

编程接口字节:为准确识别寄存器组的布局提供了最终的尺度。

⑤子系统厂商ID寄存器和子系统ID寄存器

这个寄存器属于PCI兼容寄存器,要求强制实现。除带子类00h~04h的基类06h(桥),或者带子类00h~03h的基类08h之外,这两个寄存器都是强制实现的。

子系统厂商ID由SIG授予,子系统ID由厂商自己提供。如果两个寄存器中的值为0,则说明没有与该功能相关的子系统厂商ID和子系统ID。

该寄存器解决的问题:一种功能极可能停驻在一个卡里,也可能停驻在一个嵌入式设备里。围绕相同的PCI/PCI-X或PCIe核心逻辑设计的功能可能有相同的厂商ID和设备ID。这样的情况下,操作系统在识别功能的驱动程序并将其载入存储器时,就存在着问题。这两个强制性的寄存器专用来识别该功能所在的附加卡或子系统,使用这两个寄存器,对由不同厂商制造、但又围绕相同的核心逻辑设计的卡或子系统,操作系统完全可以区分出。这就使得具有即插即用功能的操作系统能将正确的驱动程序装载到存储器中。

⑥头类型寄存器

这个寄存器属于PCI兼容寄存器,要求强制实现。下图展示了头类型寄存器的故事。这个寄存器的比特[6:0]定义该功能配置头中双字4~15的格式。比特7定义该设备是单功能设备(bit7=0),还是多功能设备(bit7=1)。在配置期间,通过检测bit7的状态,就能确定在需要配置的这个设备中是否有其他任何功能。

⑦BIST寄存器

PCI兼容寄存器,可选。既可以铜鼓请求者功能也可以通过完成者功能实现。如果某功能实现了内部自检(Built-In Self-Test, BIST)机制,必须实现下图的寄存器。下表描述了每个比特的作用。如果该功能不支持BIST,在读取时者个寄存器必须返回0。比特6设置为1,则会调用该功能的BIST机制。BIST完成后,该功能将复位bit6。如果该功能未能在2s的事件内复位bit6,配置软件必须放弃执行该功能。在BIST结束后,测试结果会立即反映在该寄存器的低端4比特中。如果结果值为0,则表示已成功完成BIST;若为非零值,则表示这是一个功能专用错误代码。

| 比特 |

功能 |

| 3:0 |

完成代码,为0表示成功完成;非0表示发生了与特定功能有关的错误 |

| 5:4 |

保留 |

| 6 |

开始BIST(Start BIST),向该比特写入1,表示开始该功能的BIST。完成后,该功能将自动复位该比特。如果BIST不能在2s内完成,软件将不能执行该功能。 |

| 7 |

具有BIST功能,如果功能有BIST,将返回1,否则返回0。 |

⑧功能指针寄存器

PCI兼容寄存器,对PCI功能而言是可选的,对PCI-X或PCIe是强制的。

PCI规范2.1版将功能的PCI兼容配置空间的前16个双字定义为其配置头空间。初衷时将该功能所有的配置寄存器都配置在这个区域,并且将所有的功能专用配置寄存器都配置在PCI兼容配置空间的后48个双字中。PCI规范2.2版定义新的配置寄存器时,空间已经不够用了。因此允许将其定义的部分寄存器配置在功能的PCI兼容配置空间的后48个双字中。

如果状况寄存器中的功能列表(Capabilities List)比特设置为1,该功能就会在PCI兼容配置空间双字13的0字节实现一个功能指针寄存器。该指针包含PCI兼容配置空间后48个双字之中功能列表的起始地址。规则是:最低的两个有效比特必须硬连线为0,且在读这个寄存器时,软件必须忽略它们;高端的6比特表示在PCI兼容配置空间后48个双字中新增寄存器8比特起始地址的高6比特,两个最低有效比特假设为0。

功能指针寄存器所指的配置位置是配置寄存器组链表的第一个条目,其中每一个寄存器组都支持某一项特征。每个条目都具有下图所示的一般格式,其中第一个字节成为功能ID(Capability ID,由PCI-SIG分配),用于识别与这个寄存器组相关的特征,而第二个字节或者指向具有另一特征的寄存器组,或者用于表示再也没有其它的寄存器组与这个功能相关(指针值为0)。各自特征的寄存器组总是紧跟在该条目前两个字节的后面,并且其长度和格式由特征本身的类型决定。

PCI规范2.3定义的功能ID如下表:

| ID |

说明 |

| 00h |

保留 |

| 01h |

PCI电源管理接口 |

| 02h |

AGP |

| 03h |

VPD |

| 04h |

插槽识别 |

| 05h |

消息传送中断 |

| 06h |

紧凑型PCI热交换 |

| 07h |

PCI-X设备 |

| 08h |

保留给AMD |

| 09h |

厂商专用功能寄存器组 |

| 0ah |

调试端口 |

| 0bh |

紧凑型PCI中央资源控制 |

| 0ch |

PCi热插拔 |

| 0dh~0fh |

保留 |

| 10h |

PCIe功能寄存器组 |

| 11h~ffh |

保留 |

⑨CardBus CSI指针寄存器

属于PCI兼容寄存器,是可选的。它由共享CardBus和PCI或PCIe功能间芯片的功能实现,并指向Cardbus卡上的卡信息结构。这个寄存器是只读的,用以表明可从下述地址空间中所指明的偏移地址来访问CIS:

从该功能所属的功能专用PCI兼容配置空间之中的偏移地址来访问;

从该功能在其中一个存储器机制寄存器所指明的、相对于起始地址的偏移地址来访问;

从扩展ROM之中的某个代码映像的偏移地址来访问。

⑩扩展ROM基址寄存器

PCI兼容寄存器,如果功能中嵌入了设备ROM,它就是必须的。许多PCI功能都潜入了设备ROM,而这个设备ROM包含了该功能的设备驱动程序。扩展ROM的起始存储器地址及其大小均在扩展ROM基址寄存器中定义,而扩展ROM基址寄存器位于配置头区域的双字12之中。

扩展ROM基址寄存器的格式如下图所示:

扩展ROM基址寄存器的格式如下:

比特0为1,表示启用该功能的ROM地址解码器;

比特[10:1]保留;

比特[31:11]用于指定ROM的起始地址。

⑪命令寄存器

属于强制性寄存器,格式如下图。下表描述了非桥功能所属命令寄存器的每个比特。

| 比特 |

属性 |

说明 |

| 0 |

RW |

IO地址空间解码器允许: 0-禁用IO解码器,不认识针对这个设备的IO事务; 1-启动IO解码器,接受针对这个设备的IO事务 |

| 1 |

RW |

存储器地址空间解码器允许: 0-禁用存储器解码器,不认识针对这个设备的存储器事务; 1-启动存储器解码器,接受针对本设备的存储器事务 |

| 2 |

RW |

总线主控器允许: 0-禁用端点功能发布存储器或IO请求,同时也禁止生成MSI消息;

|

| 3 |

RO |

专用循环允许,PCIe为0 |

| 4 |

RO |

存储器写和无效,PCIe为0 |

| 5 |

RO |

VGA调色板,PCIe为0 |

| 6 |

RW |

奇偶错误响应,在状况寄存器中,如果设置了奇偶错误响应比特,且有下列条件之一发生,请求者将设置主控器数据奇偶比特: 如果请求者受到一个有错误的完成; 如果请求者写请求中毒。 如果清除了奇偶错误比特,则不会设置主控器数据奇偶错误比特。 默认值为0 |

| 7 |

RO |

IDSEL步长/等待循环控制,PCIe必须是0 |

| 8 |

RW |

SERR允许,设置该比特时,允许功能将它所发现的非致命错误和致命性错误报告给根联合体。通过设置该比特或者设备控寄存器中的PCIe的专用比特,允许功能将这类错误报告给根联合体。 默认值为0 |

| 9 |

RO |

快速背靠背功能允许,PCIe必须为0 |

| 10 |

RW |

中断禁用,控制PCIe功能产生INTx中断消息的能力: 0-允许功能产生INTx中断消息; 1-禁止功能产生INTx中断消息。 如果该功能已经传送了Assert_INTx仿真中断消息,并在随后的操作中又设置了该比特,它必须为先前传送的每一个确定消息发送一个相应的Deassert_INTx消息。 |

⑫状况寄存器

属于强制性寄存器。下表描述了状况寄存器的每个比特。具有RWIC属性的比特字段具有如下特征:

读取时返回寄存器相应比特的状况,并可以通过向它写入1清除状况比特。向RWIC比特写0,则不起作用。

| 比特 |

属性 |

说明 |

| 3 |

RO |

中断状况:表示该功能有一个未完成的中断请求(该功能以前发送了一个中短消息,正在等待服务),默认值为0,仅与INTx消息有关 |

| 4 |

RO |

功能列表,表示在功能的PCI兼容配置空间前48个双字中存在一个或多个扩展功能寄存器组。PCIe功能都要求实现PCie功能结构,所以该比特必须设置为1 |

| 5 |

RO |

支持66MHz,PCIe为0 |

| 7 |

RO |

支持快速背靠背,PCIe为0 |

| 8 |

RW1C |

主控器数据奇偶错误,如果在命令寄存器设置了奇偶错误允许比特,且满足如下条件之一,请求者就设置主控器数据奇偶错误比特: 如果请求者收到一个有错误的完成; 如果请求者写请求中毒。 如果清除了奇偶错误比特,则不会设置主控器数据奇偶错误比特。默认值为0 |

| 10:9 |

RO |

DEVSEL计时,PCIe为0 |

| 11 |

RW1C |

已发送目标异常中断,当充当完成者的功能通过发送完成者异常中断完成状况到请求者要求终止请求时,设置该比特。默认值为0 |

| 12 |

RW1C |

已接收目标异常中断,当请求者收到一个待完成者异常中断完成状况的完成时,设置该比特,默认值为0 |

| 13 |

RW1C |

已接收主控器异常中断,当请求者收到一个带未受支持的请求完成状况的完成时,设置该比特,默认值为0 |

| 14 |

RW1C |

已发信号系统错误,当功能发送ERR_FATAL或ERR_NONFATAL消息,并且命令寄存器中的SERR允许比特设为1时,设置该比特,默认值为0 |

| 15 |

RW1C |

已发现奇偶错误,不论功能的命令寄存器中奇偶错误启动比特状态如何,只要收到一个中毒的TLP,就设置该比特。默认值为0 |

⑬缓存行大小寄存器

可选寄存器。该字段由PCIe设备作为读写来实现,目的是为了兼容传统的功能,但对PCIe设备的功能无影响。

⑭主控器延时定时器寄存器

可选寄存器。不能用于PCIe,必须硬连线位0。

⑮中断线寄存器

可选寄存器。

在PCI功能中,如果PCI功能通过INTx引脚生成中断请求,则是必须的。PCI规范允许功能利用中断引脚或MSI功能(MSI-capability)生成中断。这个可读/可写中断寄存器可用于识别PCI中断请求引脚需要路由到中断请求控制器的哪些输入上。在PC环境中,这个寄存器从00h到0fh的值对应中断控制器从IRQ0到IRQ15的输入。值ffh表示不知道或无连接,10h~feh保留。OS或设备驱动程序通过检查设备的中断线寄存器,可以确定该设备要使用哪些系统中断请求线来发布服务请求。

在PCIe功能中,PCIe功能可以用传统的PCI/PCI-X方式生成中断。

⑯中断引脚寄存器

可选寄存器。

如果PCI功能通过INTx引脚生成中断请求,则是必须的。这个只读寄存器定义了INTA#到INTD#这4个中断请求引脚中PCI功能所要连接的那个引脚。01h到04h值对应着PCI中断请求引脚INTA#到INTD#。返回值若是0,则表明该设备没有生成中断。所有其他值保留。

在PCIe功能中,这个只读寄存器用于识别由功能发送到上有生成中断的传统INTx中断消息,值01h到04h分别对应传统中断消息INTA#到INTD#。若返回值为0,表明该设备不会利用老方法生成中断。其他所有值保留。

⑰基址寄存器

位于功能配置头空间的基址寄存器,常用于实现功能可编程的存储器和/或IO解码器。每个寄存器32bits宽(如果存储器解码器及其有关存储器块所在的地址边界超过4GB,则寄存器宽为64bits)。下图给出了3种可能的基址寄存器格式,其中bit0是只读的,用于表明是一个存储器或IO解码器:

bit0=0,该寄存器为一个存储器地址解码器;

bit0=1,该寄存器为一个IO地址解码器。

在存储器基址寄存器中,bit[2:1]定义解码器是32bits还是64bits的:

00b=32bits寄存器。配置软件写一个32bits的起始存储器地址到该寄存器中,在第一个4GB存储器地址空间中指定一个起始地址。

10b=64bits寄存器。配置软件写一个64bits的起始存储器地址到该寄存器中,在264存储器地址空间中指定一个起始地址。这个基址寄存器占据配置头空间两个连续的双字。第一个双字用于设定起始地址的低端32bits,第二个双字用于指定起始地址的高端32bits。

可预取属性比特:bit3定义存储器块是否是可预取的。配置软件通过检查存储器目标基址寄存器中的可预取比特,可确定存储器目标是否是可预取的。在PCIe端点功能中,可预取比特设置为1的所有存储器BAR必须作为64bits存储器BAR实现,而可预取比特未设置为1的存储器BAR可作为32bits的BAR实现。

基址字段:对32bits的存储器解码器,该字段位于bit[31:7];对于64bits的存储器解码器,则位于[63:7],用于:

确定与这个解码器有关的存储器大小;

分配起始地址给解码器。

存储器示例:向位于配置双字04d的基址寄存器写FFFFFFFFh,返回值为FFF00000h。

bit0=0:说明这是一个存储器地址解码器;

bit[1:1]=00b:说明是一个32bits存储器地址的解码器;

bit3=0:存储器不可预取;

bit20时基址字段中第一个值为1的比特,二进制权值为1048576,说明这是一个存储器为1MB的地址解码器。

⑱Min_Gnt/Max_Lat寄存器

可选寄存器,PCIe不适用,硬连线为0。

1.12.5 PCIe专用配置寄存器

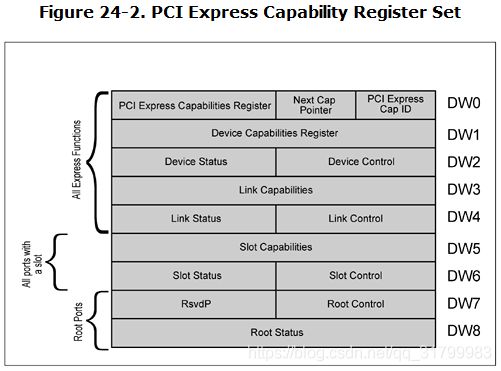

每个PCIe功能都有一块大小为4KB的专用存储器地址区,其配置寄存器就在该地址中实现。每种PCIe功能必须在PCI兼容寄存器空间前64个中的后48个双字的某处有一组PCIe功能寄存器。该功能该可以有选择地实现任何PCIe扩展功能寄存器组。

除PCIe功能结构外,其他PCIe功能寄存器组对每种功能而言都是强制实现的,作为PCI兼容寄存器区域低端48个双字中功能寄存器组链表的一部分。这个寄存器组中有一部分是可选的。

寄存器实现要求:

每种Express功能必须在双字0到双字4中实现寄存器;

与每个根端口有关的桥必须在双字7和双字8中实现寄存器;

与连接到插槽的根端口或下游交换器端口有关的每个桥必须在双字5和双字6中实现寄存器。

以下为PCIe功能寄存器组中必须实现的每个寄存器:

PCIe功能ID寄存器(PCI Express Capability ID Register);

下一个功能指针寄存器(Next Capability Pointer Register);

PCIe功能寄存器(PCI Express Capabilities Register);

设备功能寄存器(Device Capabilities Register);

设备控制寄存器(Device Control Register);

设备状况寄存器(Device Status Register);

链路功能寄存器(Link Capabilities Register);

链路控制寄存器(Link Control Register);

链路状况寄存器(Link Status Register)。

1.12.5.1 PCIe功能ID寄存器

只读存储器,包含的值为10h,表示这是PCIe功能寄存器组的起始位置。

1.12.5.2下一个功能指针寄存器

这是一个只读寄存器,其值可为下述二者之一:

指向PCI兼容配置空间低端48个双字中下一组功能寄存器的非零偏移地址;

如果PCIe功能寄存器组是PCI兼容配置空间中功能寄存器链表的最后一组寄存器,其值为00h。

1.12.5.3 PCIe功能寄存器

| 比特 |

类型 |

说明 |

| 3:0 |

RO |

功能版本,由SIG定义的PCIe功能结构的版本号(必须是1h) |

| 7:4 |

RO |

设备/端口类型,Express逻辑设备的类型: 0000b:PCIe端点; 0001b:传统PCIe端点。即运行期间要求通过BAR分配IO空间的功能。如果是在传统PCIe端点设备上实现,软件可能忽略扩展配置空间功能; 0100b:根联合体的根端口; 0101b:交换器上游端口; 0110b:交换器下游端口; 0111b:Express到PCI/PCI-X桥; 1000b:PCI/PCI-X到Express桥。 其它保留 |

| 8 |

HwInit |

插槽实现,设置时表示该根端口或交换器下游端口将连接到附加卡插槽上。 |

| 13:9 |

RO |

中断消息数目,如果该功能被分配了多个MSI中断消息值,当设置了该功能的插槽状况寄存器或根状况寄存器的任何状况比特时,该寄存器将包含写到MSI目标地址的MSI数据值。如果系统软件改变了分配给该功能的消息数据值的数目,则该功能的硬件也必须更新该字段,以反映这种变化。 |

1.12.5.4 设备功能寄存器

下图和下表描述了该寄存器的每一比特字段,这个寄存器定义了全局范围内都适用该设备的运行特征。

| 比特 |

说明 |

| 2:0 |

最大有效载荷支持(Max Payload Size Supported),该功能所支持的TLP最大有效载荷为: 000b=最大128字节; 001b=最大256字节; 010b=最大512字节; 011b=最大1KB字节; 100b=最大2KB字节; 101b=最大4KB字节; 110b=保留;111b=保留。 |

| 4:3 |

仿真功能支持 |

| 5 |

扩展标记字段支持,表示该功能作为请求者时标记字段所支持的最大数目。 0=所支持的标记字段为5bits(每个请求者最多有32个未完成请求); 1=所支持的标记字段为8bits(每个请求者最多有256个未完成请求)。 如果支持和使用8bits的标记,只要设定了设备控制寄存器中的扩展标记字段允许比特为1,就可以启用该特征。 |

| 8:6 |

端点L0可接受延迟,表明一个端点从L0s状态转换到L0状态所能接受的总延迟。该值间接地表明了端点内部缓存的数量。电源管理软件利用该值比较这个端点到它的父根端口之间所有组件所报告的L0退出延迟,以确定是否能在不损失性能的情况下使用ASPM L0条目。 000b=小于64ns; 001b=不小于64ns,不大于128ns; 010b=不小于128ns,不大于256ns; 011b=不小于256ns,不大于512ns; 100b=不小于512ns,不大于1us; 101b=不小于1us,不大于2us; 110b=2us~4us; 110b=大于4us |

| 11:9 |

端点L1可接受延迟,表明一个端点从L1状态转换到L0状态所能接受的总延迟。该值间接地表明了端点内部缓存的数量。电源管理软件利用该值比较这个端点到它的父根端口之间所有组件所报告的L1退出延迟,以确定是否能在不损失性能的情况下使用ASPM L1条目。 000b=小于1us; 001b=不小于1us,不大于2us; 010b=不小于2us,不大于4us; 011b=不小于4us,不大于8us; 100b=不小于8us,不大于16us; 101b=不小于16us,不大于32us; 110b=32us~64us; 110b=大于64us |

| 12 |

警告按钮存在,设置为1时,表示该卡或者模块上有一个警告按钮 |

| 13 |

警搞指示器存在,设为1时,表示该卡或者模块上有一个警告指示器 |

| 14 |

电源指示器存在,设为1时,表示该卡或者模块上有一个电源指示器 |

| 25:18 |

捕获的插槽功率极限值,与插槽功率极限因子一起使用,指定插槽所供应的功率上限。 |

| 27:26 |

捕获的插槽功率极限因子,指定功率极限计算所用的因子 00b=1.0x;01b=0.1x;10b=0.01x;11b=0.001x |

1.12.5.5 设备控制寄存器

| 比特 |

说明 |

| 0 |

可修正错误报告启用,对于多功能设备,该比特控制所有功能的错误报告。对根联合体,报告根联合体内部发生了可修正错误。不产生外部ERR_COR消息。默认值为0。 |

| 1 |

非致命错误报告启用,该比特控制非致命错误的报告。对于多功能设备,它控制所有功能的错误报告。对根端口,报告根联合体内部发生的非致命错误,不产生外部ERR_NONFATAL消息,默认值为0。 |

| 2 |

致命错误报告启用,该比特控制致命错误的报告。对于多功能设备,它控制设备内所有功能的错误报告。对根联合体,报告根联合体内部发生的致命错误。不产生外部ERR_NONFATAL消息,默认值为0。 |

| 3 |

未受支持请求报告启用。当设定为1时,它对未受支持的请求予以报告。对于多功能设备,它控制所有功能的UR报告。是否报告根端口收到的错误消息完全由根控制寄存器控制。 |

| 4 |

启用灵活的顺序,设定为1时,表示对于发起写顺序要求不严格的请求,允许设备设置其属性字段中灵活的顺序比特。默认值为1。 |

| 7:5 |

最大有效载荷(Max Payload Size),设置设备TLP数据的最大有效载荷。作为接收者,该设备处理的TLP必须同设置值一样大;作为发送者,该设备产生的TLP不能超过该设置值。其许可值由设备功能寄存器中的最大有效载荷支持字段控制,并可通过程序修改。 000b=128B;001b=256B;010b=512B;011b=1024B;100b=2048B;101=4096B;110b、111b保留 |

| 8 |

扩展标记字段允许,设置为1时,表示设备可以将一个8bits的标记字段用作请求者。如果清0,则设备限定到一个5bits的标记字段。默认值为0 |

| 9 |

仿真功能允许,默认值为0 |

| 10 |

辅助电源PM允许,设为1时,表示设备可启用与PME Aux电源无关的Aux电源。 |

| 11 |

启用无侦测 |

| 14:12 |

最大读请求的大小(Max_Read_Request_Size),表示设备作为请求者时最大的读请求大小。 000b=128B;001b=256B;010b=512B;011b=1024B;100b=2048B;101=4096B;110b、111b保留 |

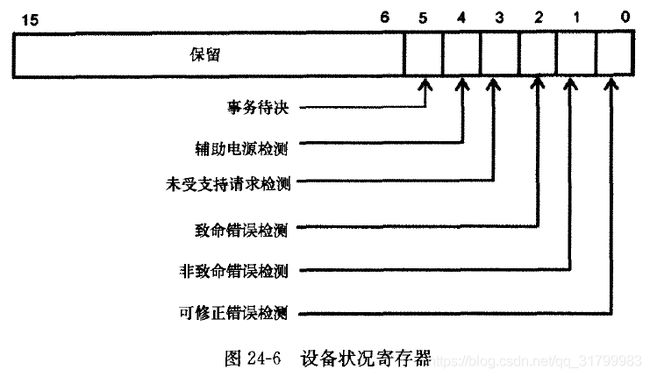

1.12.5.6 设备状况寄存器

| 比特 |

类型 |

说明 |

| 0 |

RW1C |

可修正错误检测,若为1,表示自软件上次清除该比特之后,又发现了一个或多个可修正错误,不管是否启用了设备控制寄存器中的错误报告机制,该比特均反映了可修正错误的发生。在多功能设备中,每种功能都利用该比特表示是否检测到可修正错误。默认值为0 |

| 1 |

RW1C |

非致命错误检测,若为1,表示自软件上次清除该比特之后,又发现了一个或多个非致命错误。不管是否启用了设备控制寄存器中的错误报告机制,该比特均反映了非致命错误的发生。在多功能设备中,每种功能都利用该比特表示是否检测到了非致命错误。默认值为0 |

| 2 |

RW1C |

致命错误检测,若为1,表示自软件上次清除该比特之后,又发现了一个或多个致命错误。不管是否启用了设备控制寄存器中的错误报告机制,该比特均反映了致命错误的发生。在多功能设备中,每种功能都利用该比特表示是否检测到了致命错误。默认值为0 |

| 3 |

RW1C |

未受支持请求检测,当设置为1时,表示该功能接收到未受支持的请求。不管是否启用了设备控制寄存器中的错误报告机制,该比特均反映了错误的发生,在多功能设备中,每种功能都利用该比特表示是否检测到了UR错误。默认值为0 |

| 4 |

RO |

辅助电源检测,需要辅助电源的设备如果检测到辅助电源,就将该比特设置为1 |

| 5 |

RO |

事务待决,设置为1时,表示该功能发布了一个尚未处理完成的非报告请求数据包。仅当所有未完成的非报告请求处理完毕或被完成超时机制终止后,功能才报告该比特已清除。 |

1.12.5.7 链路寄存器

共有3个与链路有关的寄存器:链路功能寄存器、链路控制寄存器、链路状况寄存器。

链路功能寄存器:

| 比特 |

类型 |

说明 |

| 3:0 |

RO |

最大链路速度 |

| 9:4 |

RO |

最大链路宽度: 000000b=保留;000001b=x1;000010b=x2;000100b=x4; 001000b=x8;001100b=x12;010000b=x16;100000b=x32; 其他保留 |

| 11:10 |

RO |

活动状态电源管理(ASPM),表示这条链路所支持的ASPM级别: 00b=保留;01b=支持L0;10b=保留;11b=支持L0和L1 |

| 14:12 |

RO |

L0s退出延迟,表示链路的L0s退出延迟 |

| 17:15 |

RO |

L1退出延迟,表示该链路的L1退出延迟 |

| 31:24 |

HWIint |

端口号,表示与这条链路有关的端口号 |

链路控制寄存器:

| 比特 |

类型 |

说明 |

| 1:0 |

RW |

活动状态电源(ASPM)管理控制,它控制链路所支持的ASPM水平: 00b=禁用;01b=L0s进入启用,表示支持发送器进入L0s,但是当该字段被禁用时,接收器必须能进入L0s; 10b=L1进入启用;11b=L0s和L1进入启用 |

| 3 |

对根端口和交换器端口为RO;对端点为RW |

读完成边界(RCB) 根端口:硬连线,表示根端口的RCB值,只读:0b=64B;1b=128B 端点:由配置软件设定,表示端点上游根端口的RCB值。没有实现该特征的设备必须硬连线为0:0b=64B;1b=128B 交换器端口:保留,硬连线为0 |

| 4 |

RW |

链路禁用,1=禁用该链路。端点设备和交换器上游端口的该字段均保留。在链路的状态实际改变之前,可立即读取写入该字段的值,默认值为0b |

| 5 |

RW |

链路重新定向:1=通过将物理层LTSSM改变到恢复状态来重新定向链路;读该比特返回的总是0b;端点设备和交换器上游端口的该比特均保留 |

| 6 |

RW |

公共始终配置:1表示这个组件和本链路另一端的组件正在共用一个公共参考时钟;0表示这个和本链路另一端的组件分别使用不同的参考时钟。组件将该比特引用的参考时钟与链路功能寄存器所报告的L0s和L1退出延迟相乘;只要链路两端的组件中有一个改变了该比特,软件就必须将该寄存器中的链路重新定向比特设置为1,从而重新定向该链路,默认值为0 |

| 7 |

RW |

扩展同步。该比特若设置为1,则:在L0s状态期间,必须传输4096个FTS有序集;进入L0状态前必须紧随一个SKP有序集;进入恢复状态前,在L1状态期间必须传输1024个TS1有序集。默认值为0 |

链路状况寄存器:

| 比特 |

类型 |

说明 |

| 3:0 |

RO |

链路速度,表示协商后的链路速度 0001b=2.5Gb/s;其它保留 |

| 9:4 |

RO |

协商链路带宽,表示协商后的链路带宽 000001b=x1;000010b=x2;000100b=x4;0010000=x8; 010000b=x16;100000b=x32;其它保留 |

| 10 |

RO |

定向错误,1表示发生链路定向错误 端点设备和交换器上游端口上的该比特均保留。在成功定向链路到L0链路状态后,软件将该比特清除 |

| 11 |

RO |

链路定性,为1时表示链路定向正在进行之中,或表示链路重新定向比特已设为1,但链路定向该没有开始。链路一旦定向,硬件便将该比特清除;端点设备和交换器上游端口的该比特不可用,均保留 |

| 12 |

HWInit |

插槽始终配置,该比特表示连接器上的组件使用平台所提供的同一物理参考时钟。如果设备使用的始终与连接器上的参考始终无关,则该比特必须清零 |

更多内容欢迎关注公众号:FPGA训练营。