平头哥(T-Head )开源RISCV处理器OpenC906 RTL仿真

在过去的几年里,阿里集团平头哥陆续推出了几款RISCV处理器,有些处理器已经在产业界得到了应用,比如在某志的D1处理器中,就嵌入了平头哥的玄铁C906内核为 “芯”。RISCV虽然是一个开放标准,并且网络上也不乏一些开源核的RTL实现,但是商用的RISCV内核一般都是闭源的。不过令人惊喜的是,在今年十月,平头哥将其设计的四款RISCV内核开源,这其中就包括D1使用的C906核心。

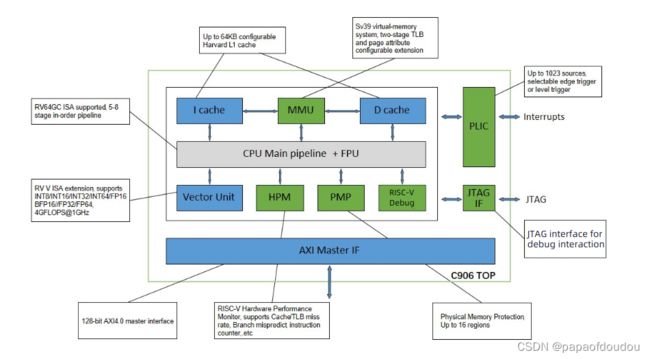

玄铁 C906 是阿里巴巴平头哥半导体有限公司开发的低成本 64 位 RISC-V 架构处理器核,玄铁 C906 基于 64 位 RISC-V 架构,并对 RISC-V 架构进行了扩展增强。扩展增强包括:

1.指令集增强:重点针对内存访问、算术运算、位操作、Cache 操作四个方面进行增强,总计扩展130 条指令。同时,玄铁处理器开发团队在编译器层面对这些指令进行支持,除 Cache 操作指令外这些指令均可编译产生,包括 GCC 和 LLVM 编译.

2.内存模型增强:扩展内存页面属性,支持 Cacheable、Strong order 等页面属性,并在 Linux 内核上进行支持.

- 玄铁 C906 的主要体系结构参数包括:

- RV64IMA[FD]C[V]架构

- 平头哥指令扩展增强技术

- 平头哥内存模型增强技术

- 5 级整型流水线,单发按序执行

- 128 位的向量计算单元,支持 FP16/FP32/INT8/INT16/INT32 的 SIMD 计算.

C906是RV64位指令集,5 级按序单发射,8KB-64KB L1 Cache支持,不支持L2 Cache,支持半/单/双精度,VIPT四路组联L1数据缓存.

C906框图

开源地址:T-Head Semiconductor Co., Ltd. · GitHub

下面以openC906为例,介绍如何基于开源项目搭建一个处理器内核仿真平台。通过仿真平台可以获得CPU内部时钟级的运行信息,捕捉到程序运行任意时刻的信号,这对于一名系统工程师来讲,意义重大。下面开始。

环境准备

- ubuntu18.04

- iverilog,vvp,gtkwave工具

- 平头哥裸机GCC编译器

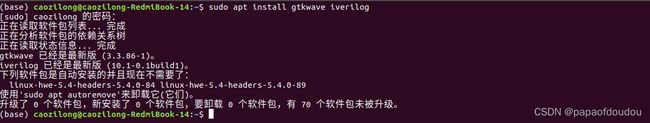

iverilog(vvp), gtkwave安装:

gcc:

平头哥芯片开放社区(OCC)

我选择的包为:Xuantie-900-gcc-elf-newlib-x86_64-V2.0.3-20210806.tar.gz,下载后解压:

获取RTL代码

git clone https://github.com/T-head-Semi/openc906.git配置&修改

代码下来,不能直接仿真运行,必须要做一些修改。感觉平头哥在文档方面做得很差劲,比较不注意细节,GITHUB上文档就三言两语,即便为社区做了好事,在一些细节上不注意,也会遭到埋怨。下面就将这些平头哥文档中没有说明,但是必须要解决的问题列举出来。

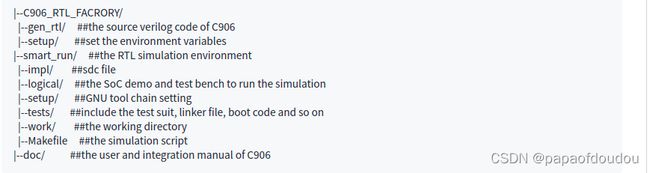

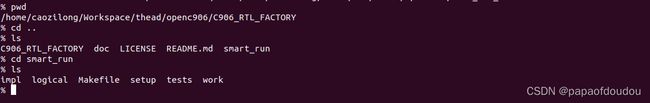

首先看一下目录结构:

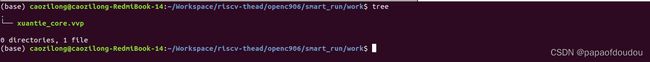

这个目录结构和GITHUB文档中给出的结构有所不同,sdk中缺少smart_run目录下的work目录。

work目录需要手工创建,而文档中并没有说明,这是第一个问题, 没有work目录会导致后面运行make 失败,我们手工创建,创建之后目录列表是下面的样子:

其余问题我们在具体操作步骤中解决。

综合

RTL环境需要在csh中运行,csh有一些不便,比如不支持自动补全等等,不知道为何T-HEAD一定要将配置脚本写为.csh格式。

首先,配置工程路径环境变量,执行以下命令序列:

$ csh

% cd C906_RTL_FACTORY

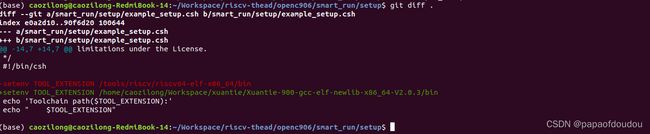

% source setup/setup.csh然后将工具链路径替换为真实的编译器路径:openc906/smart_run/setup/example_setup.csh

之后切换到smart_run目录

初始化工具链环境变量:

% source./smart_run/setup/example_setup.csh 可以看出这里除了问题,这就是第二个平头哥文档没有注意的问题,解决方式是删除example_setup.csh头部的版权声明部分,不知道平头哥怎么发布的,难道发布之前都没有测试么?基本的语法错误都会犯?

可以看出这里除了问题,这就是第二个平头哥文档没有注意的问题,解决方式是删除example_setup.csh头部的版权声明部分,不知道平头哥怎么发布的,难道发布之前都没有测试么?基本的语法错误都会犯?

删除之后,再次运行,这次成功:

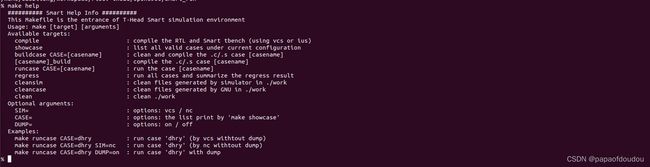

之后是综合,进入到openc906/smart_run目录,执行make help:

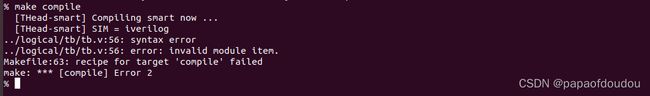

综合的话,执行命令make compile

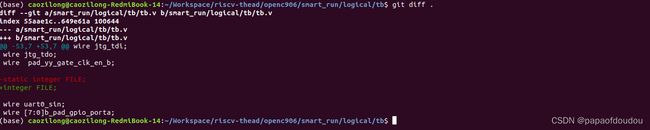

这个错误,经过请教群友(GITHUB上有钉钉群),他经历过同样的问题,修改方式如下:将56行的static integer FILE修改为integer FILE.

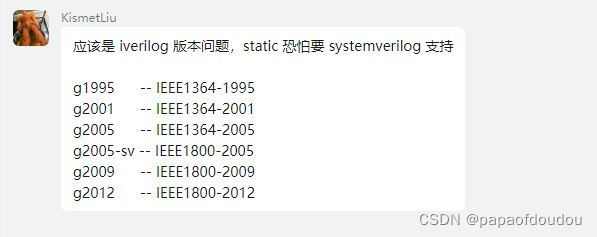

怀疑这个问题和iverilog的版本有关,在群里得到确认,还是那句话,既然构建系统中指定iverilog为默认的综合工具,在发布之前都没有验证么?对于这么大一家公司来讲感觉有些不可思议。

不管怎样,流程还要继续,再次编译,这次成功执行:

执行 make showcase,查看有哪些用例可以跑:

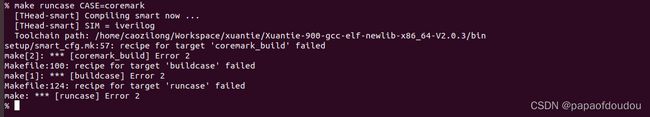

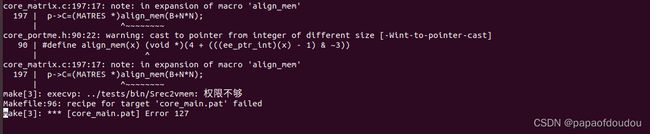

我们执行其中一个,执行make runcase CASE=coremark,又出错:

我们执行其中一个,执行make runcase CASE=coremark,又出错:

这次出错的改法是,拷贝命令添加 -fr 选项:

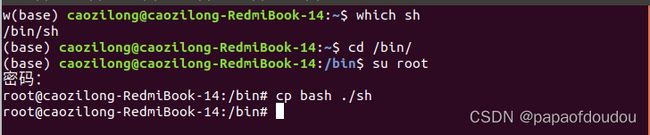

仍然有错误,看到了/bin/sh提示,想到莫非是shell解释其不对,修改/bin/sh指向bash

这样做果然可以解决这个问题,不过新问题又来了,如下图,没关系,兵来将挡,水来土掩。

可以看到编译过程会以LOG文件的形式被记录下来:coremark_build.case.log

在work目录中果然有同名文件:

我们打开这个文件,看里面有没有记录出错信息,找到最后,一条错误赫然出现在眼前:

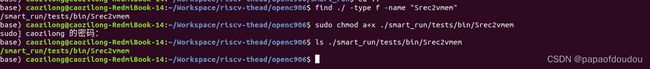

Srec2vmem是什么鬼?看名字,猜测它可能是将ELF的BINARY 转换为仿真TB可以加载的数据格式的工具,根据经验,如果它属于SDK中的工具,是由可能下载下来后不带有可执行属性,这也是LINUX的安全策略,我们强制修改其为可执行:

Srec2vmem是什么鬼?看名字,猜测它可能是将ELF的BINARY 转换为仿真TB可以加载的数据格式的工具,根据经验,如果它属于SDK中的工具,是由可能下载下来后不带有可执行属性,这也是LINUX的安全策略,我们强制修改其为可执行:

至此,修改的文件包括:

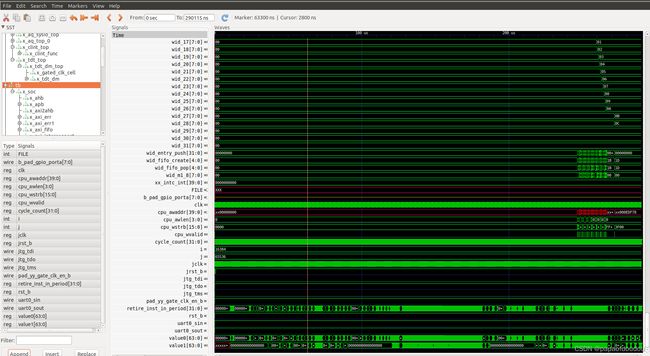

之后再次执行make runcase CASE=coremark DUMP=on

DUMP=on表示我们需要生成VCD文件查看waveform.

Binggo! 错误尽除,VVP执行仿真产生波形VCD文件中,倒上一杯咖啡慢慢等吧!

查看波形:

CPU内部对你已经毫无秘密可言了,用这种方法分析系统,只要你肯投入,相信没有解决不了的问题。

quartus ii综合仿真

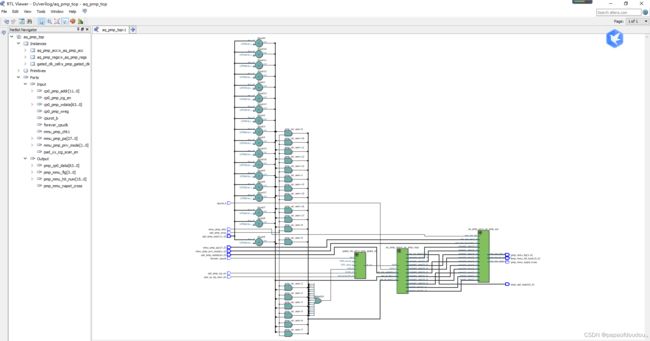

C906是用Verilog开发的,可以用altera的综合仿真工具quartus ii进行布局布线综合仿真,并且得到方框图。

建立综合工程File->New Project Winzard .....解决编译错误,综合仿真,综合成功即可,不用关心布局布线失败,因为我也不清楚目标FPGA应该选择哪个。

上一步成功后,点击菜单Tools->NetList Viewers->RTL Viewer 打开综合方框图即可查看。

要注意,工程的名字要和你想要查看的顶层wrapper的名字相同,比如下图我需要看MMU的顶层结果,就选择对应的aq_mmu_top.v文件的模块aq_mmu_top作为工程名进行综合。

TLB wrapper结构翻译过来如下图,根据THEAD文档描述,C906 MMU采用两级TLB,第一级为uTLB,分别为指令I-uTLB和数据D-uTLB,第二级为jTLB,在处理器reset后,硬件会将uTLB和jTLB的所有表项进行无效化操作,软件无需初始化操作。

I-uTLB有10个全相联表项,每个表项可以混合存储4K,2M和1G三种大小的页面,取址请求命中I-uTLB时,当拍可以得到物理地址和相应权限属性。

D-uTLB有10个全相联表项,可以混合存储4K,2M,1G三种大小的页面,加载和存储请求命中D-uTLB时,当拍可以得到物理地址和相应权限属性。

jTLB为指令和数据共用,两路组相联结果,表项大小为128/256/512可配,可以混合存储4K,2M和1G三种大小的页面,u-TLB缺失,j-TLB命中时,最快3个cycle返回物理地址和相应权限属性。

pmp wrapper 结构