武汉理工大学-并行计算-2020年期末复习指南

并行计算-2020-复习指南

制作:纪元

本提纲遵循CC-BY-NC-SA协议

(署名-非商业性-相同方式共享)文章目录

-

- 并行计算机系统及其结构模型

-

- 存储墙

- 互联网络

-

- 网络性能指标

- 静态互连网络

- 动态互连网络

- 并行计算机结构

-

- 定义

- 图示

- 并行计算机访存模型

-

- 概念

- 小结

- 当代并行计算机系统介绍

-

- 共享存储的对称多处理机SMP

-

- 结构特性:

- 问题:

- 分布存储的大规模并行处理机 MPP

-

- MPP公共结构

- MPP设计问题

- 差别

- 工作站机群COW

-

- 定义

- 优势

- 并行计算性能评测

-

- 工作负载

- 并行执行时间

- 存储器性能

-

- 存储器的层次结构

- 存储器带宽的估算

-

- 公式

- 例:RISC加法指令带宽估算

- 三大定律

-

- 简称定义

- Amdahl定律 - 固定负载的加速公式

-

- 原公式

- 归一化的公式

- 修正的公式

- 极限情况与条件

- 出发点

- 含义

- Gustafson加速定律

-

- 原公式

- 归一化公式

- 修正的公式

- 极限情况与条件

- 出发点

- 含义

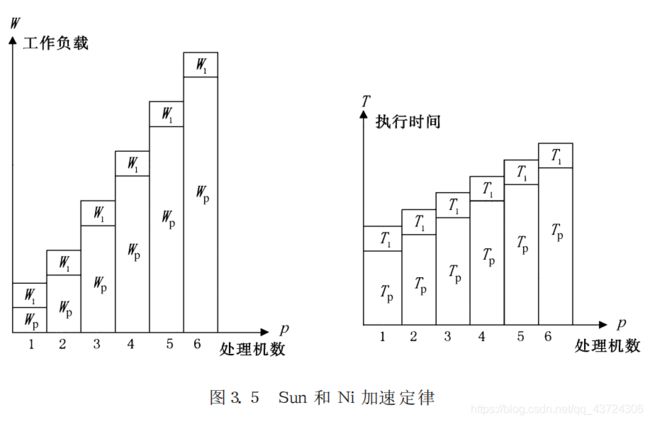

- Sun和Ni定律 - 存储受限的加速定律

-

- 原公式

- 归一化公式

- 修正的公式

- 极限情况与条件

- 基本思想

- 并行算法的设计基础

-

- 并行算法基本概念

- 并行计算模型基本概念

-

- PRAM(ParallelRandomAccessMachine)模型

-

- 分类

- 优点

- 缺点

- 推广

- 异步PRAM模型

-

- 特点

- 指令类型

- BSP(BulkSynchronousParallel)模型

-

- 性质和特点

- logP模型(logPModel)

-

- 参数

- 并行算法的一般设计策略

-

- 串行算法直接并行化

- 从问题描述开始设计并行算法

- 借用已有算法求解新问题

- 并行算法的基本设计技术

-

- 划分求解的基本步骤

- 均匀划分技术

- 对数划分技术

- 功能划分技术

- 并行算法的一般设计过程

-

- PCAM基本步骤

- 划 分

- 通 信

-

- 通信模式

- 组 合

- 映 射

-

- 基本策略

- 算法编写

-

- 矩阵相乘、线性方程组求解(稠密)、快速傅里叶变换

符号释义

- ⌊ ⌋ \lfloor \rfloor ⌊⌋:向下取整数

- ⌈ ⌉ \lceil \rceil ⌈⌉:向上取整数

题型设置

- 选择 20x2

- 填空 10x2

- 简答 2x10

- 编程 2*10

并行计算机系统及其结构模型

存储墙

内存墙,指的是内存性能严重限制CPU性能发挥的现象。

在过去的20多年中,处理器的性能以每年大约55%速度快速提升,而内存性能的提升速度则只有每年10%左右。长期累积下来,不均衡的发展速度造成了当前内存的存取速度严重滞后于处理器的计算速度,内存瓶颈导致高性能处理器难以发挥出应有的功效,这对日益增长的高性能计算(High Performance Computing,HPC)形成了极大的制约。事实上,早在1994年就有科学家分析和预测了这一问题,并将这种严重阻碍处理器性能发挥的内存瓶颈命名为"内存墙"(Memorya Wall)。

![]()

互联网络

网络性能指标

- 节点度(Node Degree):射入或射出一个节点的边数。在单向网络中,入射和出射边之和称为节点度。

- 网络直径(Network Diameter): 网络中任何两个节点之间的最长距离,即最大路径数。

- 对剖宽度(Bisection Width) :对分网络各半所必须移去的最少边数

- 对剖带宽( Bisection Bandwidth):每秒钟内,在最小的对剖平面上通过所有连线的最大信息位(或字节)数

- 对称(Symmetry):从任一节点观看网络都一样

静态互连网络

- 静态互连网络:处理单元间有着固定连接的一类网络,在程序执行期间,这种点到点的链接保持不变;典型的静态网络有一维线性阵列、二维网孔、树连接、超立方网络、立方环、洗牌交换网、蝶形网络等。

- 嵌入(Embedding):指将网络中的各节点映射到另一个网络中去。

- 膨胀(Dilation):系数来描述嵌入的质量,它是指被嵌入网络中的一条链路在所要嵌入的网络中对应所需的最大链路数。如果该系数为1,则称为完美嵌入。

- 例如,一个环网可完美嵌入到2-D 环绕网中。同样,一个超立方网也可以完美嵌入到2-D环绕网中。并非所有网络之间均可实现完美嵌入。

- 一般而言,对于高度为 h 的完全二叉树,其膨胀系数为 ⌈ h / 2 ⌉ \lceil{h/2}\rceil ⌈h/2⌉ 。

| 网络名称 | 网络规模 | 节点度 | 网络直径 | 对剖宽度 | 对称 | 链路数 |

|---|---|---|---|---|---|---|

| 线性阵列 | N N N | 2 2 2 | N − 1 N-1 N−1 | 1 1 1 | 非 | N − 1 N-1 N−1 |

| 环形 | N N N | 2 2 2 | N − 1 ( 单 向 ) ⌊ N / 2 ⌋ ( 双 向 ) N-1(单向)\\\lfloor{N}/2\rfloor(双向) N−1(单向)⌊N/2⌋(双向) | 2 2 2 | 是 | N N N |

| 2-D网孔 | ( N × N ) (\sqrt{N}\times\sqrt{N}) (N×N) | 4 4 4 | 2 ( N − 1 ) 2(\sqrt{N}-1) 2(N−1) | N \sqrt{N} N | 非 | 2 ( N − N ) 2(N-\sqrt{N}) 2(N−N) |

| Illiac网孔 | ( N × N ) (\sqrt{N}\times\sqrt{N}) (N×N) | 4 4 4 | N − 1 \sqrt{N}-1 N−1 | 2 N 2\sqrt{N} 2N | 非 | 2 N 2N 2N |

| 2-D环绕 | ( N × N ) (\sqrt{N}\times\sqrt{N}) (N×N) | 4 4 4 | 2 ( ⌊ N / 2 ⌋ ) 2(\lfloor\sqrt{N}/2\rfloor) 2(⌊N/2⌋) | 2 N 2\sqrt{N} 2N | 是 | 2 N 2N 2N |

| 二叉树 | N N N | 3 3 3 | 2 ⌈ log N ⌉ − 1 2\lceil\log{N}\rceil-1 2⌈logN⌉−1 | 1 1 1 | 非 | N − 1 N-1 N−1 |

| 星形 | N N N | N − 1 N-1 N−1 | 2 2 2 | ⌊ N / 2 ⌋ \lfloor{N/2}\rfloor ⌊N/2⌋ | 非 | N − 1 N-1 N−1 |

| 超立方 | N = 2 n N=2^n N=2n | n n n | n n n | N / 2 N/2 N/2 | 是 | n N / 2 nN/2 nN/2 |

| 立方环 | N = k × 2 k N=k\times2^k N=k×2k | 3 3 3 | 2 k − 1 + ⌊ k / 2 ⌋ 2k-1+\lfloor{k/2}\rfloor 2k−1+⌊k/2⌋ | N / ( 2 k ) N/{(2k)} N/(2k) | 是 | 3 N / 2 3N/2 3N/2 |

完美嵌入(膨胀系数=1)

不完美嵌入(膨胀系数=2)

动态互连网络

-

动态网络:用交换开关构成的,可按应用程序的要求动态地改变连接组态;典型的动态网络包括总线、交叉开关和多级互连网络等。

-

总线(Bus)实际上是连接处理器、存储模块和I/O 外围设备等的一组导线和插座。总线系统用以主设备(如处理器)和从设备(如存储器)之间的数据传输。公用总线以分时工作为基础,在多个请求情况下,总线的仲裁是重要的。

-

局部/本地总线(Local Bus):在印刷电路板上实现的总线

-

本地总线:CPU板级上的总线(习惯叫法)

-

存储器总线:存储器板级上的总线

-

数据总线:I/O 板级和通信板级上的总线。

-

系统总线:在底板上实现的,它为所有插入板之间的通信提供了通路。

-

-

局部/本地总线+存储器总线,将处理器与存储模块相连;

-

I/O总线+系统总线,将I/O设备、网卡等连接起来。

- I/O总线有时也叫作小型机系统接口SCSI(Small Computer System Interface)总线。

-

绝大多数标准总线都可低价构造单一处理系统(Unity Processor System)。在构造多处理器系统时,常使用多总线和层状总线。

板级、底板级和I/O级总线系统:

- 总线系统造价最低,但易冲突;

- 交叉开关造价最高,但带宽和选路性能最好;

- 多级互连网络是总线与交叉开关的折衷

- 主要优点采用模块结构,可扩展性好

- 但延迟随网络尺寸对数增长。

并行计算机结构

定义

大型并行机系统一般可分为6类机器,SIMD计算机多为专用,其余的5种均属于多指令多数据流MIMD计算机。

- 单指令多数据流SIMD

- 并行向量处理机PVP

- 多为定制,通常不使用高速缓存,而是使用大量的向量寄存器和指令缓冲器

- 对称多处理机SMP

- 系统对称,每个处理器可等同的访问共享存储器、I/O设备和操作系统服务。能开拓较高的并行度

- 是共享存储,限制系统中的处理器不能太多(一般少于64个),同时总线和交叉开关互连一旦作成也难于扩展。

- 大规模并行处理机MPP

- 处理节点采用商品微处理器;

- 系统中有物理上的分布式存储器;

- 采用高通信带宽和低延迟的互连网络(专门设计和定制的);

- 能扩放至成百上千乃至上万个处理器;

- 它是一种异步的MIMD机器,程序系由多个进程组成,每个都有其私有地址空间,进程间采用传递消息相互作用。

- 工作站机群COW

- COW的每个节点都是一个完整的工作站(不包括监视器、键盘、鼠标等),也可以是一台PC或SMP;

- 各节点通过一种低成本的商品(标准)网络(如以太网、FDDI和ATM开关等)互连(有的商用机群也使用定做的网络);

- 各节点内总是有本地磁盘,而MPP节点内却没有;

- 节点内的网络接口是松散耦合到I/O 总线上的,而MPP内的网络接口是连到处理节点的存储总线上的,因而可谓是紧耦合式的;

- 一个完整的操作系统驻留在每个节点中,而MPP中通常只是个微核,COW的操作系统是工作站UNIX,加上一个附加的软件层以支持单一系统映像、并行度、通信和负载平衡等

- 分布共享存储DSM多处理机。

- DSM在物理上有分布在各节点中的局部存储,从而形成了一个共享的存储器。对用户而言,系统硬件和软件提供了一个单地址的编程空间。DSM相对于MPP的优越性是编程较容易。

| 属性 | PVP | SMP | MPP | DSM | cow |

|---|---|---|---|---|---|

| 结构类型 | MIMD | MIMD | MIMD | MIMD | MIMD |

| 处理器类型 | 专用 | 定制 | 商用 | 商用 | 商用 |

| 互连网络 | 定制交叉开关 | 总线、交叉开关 | 定制网络 | 定制网络 | 商用网络(以太ATM) |

| 通信机制 | 共享变量 | 共享变量 | 消息传递 | 共享变量 | 消息传递 |

| 地址空间 | 单地址空间 | 单地址空间 | 多地址空间 | 单地址空间 | 多地址空间 |

| 系统存储器 | 集中共享 | 集中共享 | 分布非共享 | 分布共享 | 分布非共享 |

| 访存模型 | UMA | UMA | NORMA | NUMA | NORMA |

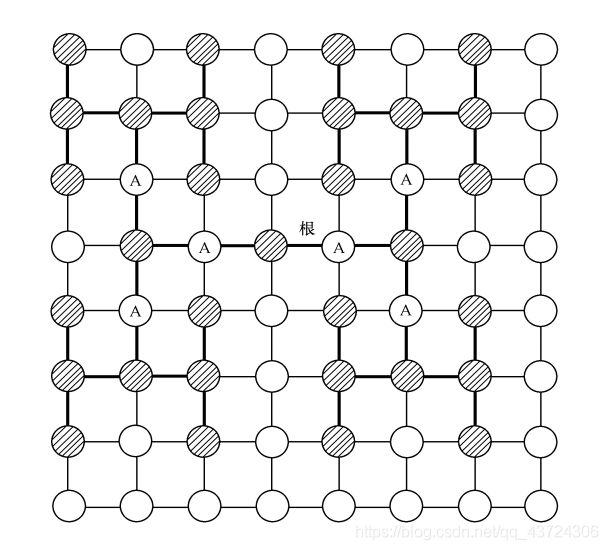

图示

- B(Bridge)是存储总线和I/O总线间的接口

- DIR(CacheDirectory)是 高速缓存目录

- IOB(I/O Bus)是I/O 总线

- NIC(InterfaceCircuitry)是网络接口电路(网卡)

- P/C(MicroprocessorandCache)是微处理器和高速缓存

- VP(Vector Processor)向量处理器

- SM(SharedMemory)是共享存储器。

- LM(Local Memory)本地/局部存储

- LD(LocalDisk)是 本 地 磁 盘

- RC(RemoteCatch)远程高速缓存

并行计算机访存模型

概念

-

UMA(Uniform MemoryAccess)模型是均匀存储访问模型的简称,适于通用或分时应用。

-

对称多处理机SMP(SymmetricMultiprocessor):所有的处理器都能等同地访问所有I/O设备、能同样地运行执行程序(如操作系统内核和I/O服务程序等)时称为

-

非对称多处理机:只有一台 或一组处理器(称为主处理器),它能执行操作系统并能操纵I/O,而其余的处理器无I/O 能力(称为从处理器),只在主处理器的监控之下执行用户代码。

其特点是:

- 物理存储器被所有处理器均匀共享;

- 所有处理器访问任何存储单元取相同的时间(此即均匀存储访问名称的由来);

- 每台处理器可带私有高速缓存;

- 外围设备也可以一定形式共享。这种系统由于高度共享资源而称为紧耦合系统(TightlyCoupledSystem)。

-

- NUMA(Nonuniform MemoryAccess)模型是非均匀存储访问模型的简称。特点是:

- 被共享的存储器在物理上是分布在所有的处理器中的,其所有本地存储器的集合就组成了全局地址空间;

- 处理器访问存储器的时间是不一样的:访问本地存储器LM 或群内共享存储器CSM较快,而访问外地的存储器或全局共享存储器 GSM较慢(此即非均匀存储访问名称的由来);

- 每台处理器照例可带私有高速缓存,且外设也可以某种形式共享。

- COMA(Cach-OnlyMemoryAccess)模型是全高速缓存存储访问的简称。是 NUMA 的一种特例。其特点是:

- 各处理器节点中没有存储层次结构,全部高速缓存组成了全局地址空间;

- 利用分布的高速缓存目录D进行远程高速缓存的访问;

- COMA中的高速缓存容量一般都大于2级高速缓存容量;

- 使用COMA时,数据开始时可任意分配,因为在运行时它最终会被迁移到要用到它的地方。

![]()

- CC-NUMA(Coherent-CacheNonuniform MemoryAccess)模型是高速缓存一致性非均匀存储访问模型的简称。它实际上是将一些SMP机器作为一个单节点而彼此连接起来所形成的一个较大的系统。其特点是:

- 绝大多数商用 CC-NUMA多处理机系统都使用基于目录的高速缓存一致性协议;

- 它在保留SMP结构易于编程的优点的同时,也改善了常规 SMP 的可扩 放性问题;

- CC-NUMA 实际上是一个分布共享存 储的DSM多处理机系统;

- 它最显着的优点是程序员无需明确地在节点上分配数据,系统的硬件和软件开始时自动在各节点分配数据,在运行期间,高速缓存一致性硬件会自动地将数据移至要用到它的地方。

-

NORMA(No-RemoteMemoryAccess)模型是非远程存储访问模型的简称。在一个分布存储的多计算机系统中,如果所有的存储器都是私有的、仅能由其处理器所访问时就称为 NORMA。系统由多个计算节点通过消息传递互连网络连接而成,每个节点都是一台由处理器、本地存储器和/或I/O 外设组成的自治计算机。NORMA的特点是:

- 所有存储器均是私有的;

- 绝大多数 NUMA都不支持远程存储器的访问;

- 在DSM中,NORMA 就消失了。

小结

物理上分布的存储器从编程的观点看可以是共享的或非共享的

- 共享存储结构(多处理机)可同时支持共享存储和消息传递编程模型

- 共享存储的编程模型可同时执行于共享存储结构和分布式存储结构(多计算机)上。

当代并行计算机系统介绍

共享存储的对称多处理机SMP

- SMP系统属于UMA(Uniform MemoryAccess)机器

- NUMA(Nonuniform MemoryAccess)机器是SMP系统的自然推广

- CC-NUMA (Coherent-CacheNUMA)实际上是将一些SMP作为单节点而彼此连接起来所构成的分布共享存储系统

结构特性:

-

对称性:系统中任何处理器均可访问任何存储单元和I/O设备;

-

单地址空间: 单地址空间有很多好处,例如因为只有一个OS和DB等副本驻留在共享存储器中,所以OS可按工作负载情况在多个处理器上调度进程从而易达到动态负载平衡,又如因为所有数据均驻留在同一共享存储器中,所以用户不必担心数据的分配和再分配;

-

高速缓存及其一致性:多级高速缓存可支持数据的局部性,而其一致性可由硬件来增强;

-

低通信延迟:处理器间的通信可用简单的读/写指令来完成(而多计算机系统中处理器间的通信要用多条指令才能完成发送/接收操作)。目前大多数商用SMP系统都是基于总线连接的,占了并行计算机很大的市场

问题:

- 欠可靠:总线、存储器或OS失效均会造成系统崩溃,这是SMP系统的最大问题;

- 可观的延迟:尽管SMP比MPP通信延迟要小,但相对处理器速度而言仍相当可观(竞争会加剧延迟),一般为数百个处理器周期,长者可达数千个指令周期;

- 慢速增加的带宽:有人估计,主存和磁盘容量每3年增加4倍,而SMP存储器总线带宽每3年只增加2倍,I/O 总线带宽增加速率则更慢,这样存储器带宽的增长跟不上处理器速度或存储容量的步伐;

- 不可扩放性:总线是不可扩放的,这就限制最大的处理器数一般不能超过10。为了增大系统的规模,可改用交叉开关连接,或改用CC-NUMA或机群结构。

分布存储的大规模并行处理机 MPP

MPP公共结构

所有的 MPP均使用物理上分布的存储器,且使用分布的I/O也渐渐变多。节点间通过高速网络HSN(HighSpeedNetwork)相连。 每个节点包括:

- 一个或多个处理器和高速缓存(P/C)

- 一个局部 存储

- 有或没有磁盘和网络接口电路 NIC(NetworkInterfaceCircuitry),它们均连向本地互连网络(早期多为总线而近期多为交叉开关)

MPP设计问题

- 可扩放性:MPP著名特性就是系统能扩展至成千上万个处理器,而存储器和I/O 的容量及带宽亦能按比例的增加。为此,采用物理上分布的存储器结构,它能提供比集中存储器结构更高的总计存储带宽,因此有潜在的高可扩放性;

- 要平衡处理能力与存储和I/O 的能力,因为存储器和I/O 子系统的速度不可能与处理器成比例地提高;

- 要平衡计算能力与交互能力,因为进程/线程的管理、通信与同步等都相当费时间。

- 系统成本:因为 MPP系统中包含大量的元件,为了保证系统的低成本应确保每个元件的低成本。为此,

- 应采用现有的商用 CMOS微处理器

- 要采用相对稳定的结构,

- 要使用物理上分布的存储器结构,它比同规模机器的中央(集中)存储器结构要便宜;

- 要采用SMP节点方式以削减互连规模。

- 设计者必须加入专门硬件以扩大物理地址空间规模

- 通用性和可用性:

- MPP要支持异步 MIMD模式;

- 要支持流行的标准编程模式;

- 诸节点应能按大、小作业要求进行不同的组合以支持交互和批处理模式;

- 互连拓扑应对用户透明,看到的是一组全连接的节点;

- MPP应在不同层次上支持单一系统映像SSI(Single-SystemImage)

- MPP必须使用高可用性的技术。

- 通信要求:MPP和 COW 的关键差别是节点间的通信,COW 使用标准的LAN,而 MPP使用高速、专用高带宽、低延迟的互连网络,无疑在通信方面优于 COW。

- 存储器和I/O 能力:因为 MPP是可扩放系统,所以就要求非常大的总计存储器和I/O 设备容量,目前I/O方面的进展仍落后于系统中的其余部分。

差别

MPP和 COW 的关键差别是节点间的通信,COW 使用标准的LAN,而 MPP使用高速、专用高带宽、低延迟的互连网络,无疑在通信方面优于 COW。

工作站机群COW

定义

工作站机群COW(ClusterofWorkstations)是实现并行计算的一种新主流技术,是属于分布式存储的 MIMD并行计算机结构,系由工作站和互连网络两部分组成。由于这种结构用于并行计算的主要资源是工作站,所以工作站机群的名称便由此产生。工作站机群COW 这一名称,在早期的研究阶段,也曾被称为工作站网络NOW(NetworkofWorkstations)。

- 从用户、程序员和系统管理员的角度看,COW 相当于单一并行系统,感觉不到多个工作站的实际存在;

- 从程序设计模式的角度看,它与 MPP一样可采用面向消息传递的SPMD(SingleProgramMultipleData)编程方式,即各个工作站均运行同一个程序,但分别加载不同的数据,从而可支持粗粒度的并行应用程序。

优势

- 投资风险小

- 编程方便

- 系统结构灵活

- 性能/价格比高

- 能充分利用分散的计算资源

- 可扩放性好

并行计算性能评测

| 名称 | 符号 | 含意 | 单位 |

|---|---|---|---|

| 机器规模 | n n n | 处理器的数目 | 无量纲 |

| 时钟速率 | f f f | 时钟周期长度的倒数 | M H z MHz MHz |

| 工作负载 | W W W | 计算操作的数目 | M f l o p Mflop Mflop |

| 顺序执行时间 | T i T_i Ti | 程序在单处理机上的运行时间 | s ( 秒 ) s(秒) s(秒) |

| 并行执行时间 | T n T_n Tn | 程序在并行机上的运行时间 | s ( 秒 ) s(秒) s(秒) |

| 速度 | R n = W / T n R_n=W/T_n Rn=W/Tn | 每秒百万次浮点运算 | M f l o p s Mflops Mflops |

| 加速 | S n = T 1 / T n S_n=T_1/T_n Sn=T1/Tn | 衡量并行机有多快 | 无量纲 |

| 效率 | E n = S n / n En=S_n/n En=Sn/n | 衡量处理器的利用率 | 无量纲 |

| 峰值速度 | R p e a k = n R ’ p e a k R_{peak}=nR’_{peak} Rpeak=nR’peak | 所有处理器峰值速度之积, R p e a k ′ R'_{peak} Rpeak′为一个处理器的峰值速度 | M f l o p s Mflops Mflops |

| 利用率 | U = R n / R p e a k U=R_n/R_{peak} U=Rn/Rpeak | 可达速度与峰值速度之比 | 无量纲 |

| 通信延迟 | t 0 t_0 t0 | 传送0一字节或单字的时间 | μ s \mu{s} μs |

| 渐近带宽 | r ∞ r_\infty r∞ | 传送长消息通信速率 | M B / s MB/s MB/s |

工作负载

所谓工作负载(荷),就是计算操作的数目,通常可用执行时间、所执行的指令数目和所完成的浮点运算数三个物理量来度量它。

- 执行时间:它可定义为在特定的计算机系统上的一个给定的应用所占用的总时间,系指应用程序从开始到结束所掠过时间(ElapsedTime),它不只是CPU时间,还包括了访问存储器、磁盘、I/O 通道的时间和 OS开销等。

- 浮点运算:对于大型科学与工程计算问题,使用所执行的浮点运算数目来表示工作负载是很自然的。对于程序中的其他类型的运算,可按如下经验规则折算成浮点运算(Flop)数:在运算表达式中的赋值操作、变址计算等均不单独考虑(即它们被折算成0Flop);单独赋值操作、加法、减法、乘法、比较、数据类型转换等运算均各折算成1Flop;除法和开平方运算各折算成4Flop;正(余)弦、指数类运算各折算成8Flop;其他类运算,可按其复杂程度,参照上述经验数据进行折算之。

- 指令数目:对于任何给定的应用,它所执行的指令条数就可视为工作负载,常以百万条指令为计算单位,与其相应的速度单位就是MIPS(每秒百万条指令)。

并行执行时间

在无重叠操作的假定下,并行程序的执行时间 T n T_n Tn为:

T n = T c o m p u t + T p a r o + T c o m m T_n=T_{comput}+T_{paro}+T_{comm} Tn=Tcomput+Tparo+Tcomm

- Tcomput为计算时间

- Tparo为并行开销时间

- 包括进程管理(如进程生成、结束和切换等)时间,组操作(如进程组的生成与消亡等)时间和进程查寻(如询问进程的标志、等级、组标志和组大小等)时间;

- Tcomm为相互通信时间。

- 包括同步(如路障、锁、临界区、事件等)时间,通信(如点到点通信、整体通信、读/写共享变量等)时间和聚合操作(如归约、前缀运算等)时间。

存储器性能

存储器的层次结构

- 容量C:表示各层的物理存储器件能保存多少字节的数据;

- 延迟L:表示读取各层物理器件中一个字所需的时间;

- 带宽B:表示在1秒钟内各层的物理器件中能传送多少个字节。

存储器带宽的估算

公式

带 宽 = 操 作 的 存 储 长 度 × 时 钟 频 率 带宽=操作的存储长度\times时钟频率 带宽=操作的存储长度×时钟频率

较快的时钟频率和处理器中较高的并行操作,可获得较宽的带宽

例:RISC加法指令带宽估算

条件:字长64位(8字节),时钟频率100MHz,单拍内可完成指令

指令流程:取2个字a,b,执行操作后送回寄存器,共涉及3个字(24字节)

三大定律

简称定义

- 是并行系统中处理器数;

- W是问题规模(下文中也常叫作计算负载、工作负载,它定义为给定问题的总计算量),

- Ws 是应用程序中的串行分量,

- Wp是W中可并行化部分(显然 Ws+Wp= W);

- Wo为额外开销

- f是串行分量比例(f= Ws/W,Ws= W1),

- 1-f为并行分量比例(显然 f+(1-f)=1);

- Ts=T1 为串行执行时间,

- Tp 为并行执行时间;

- S为加速(比),

- E为效率。

- G(p)反映存储容量增加到p倍时工作负载的增加量

Amdahl定律 - 固定负载的加速公式

原公式

S = W s + W p W s + W p p S=\frac{W_s+W_p}{W_s+\frac{W_p}{p}} S=Ws+pWpWs+Wp

归一化的公式

将 W s + W p W_s+W_p Ws+Wp表示为 f + ( 1 − f ) f+(1-f) f+(1−f)得:

S = f + ( 1 − f ) f + 1 − f p = p 1 + f ( p − 1 ) S=\frac{f+(1-f)}{f+\frac{1-f}{p}}=\frac{p}{1+f(p-1)} S=f+p1−ff+(1−f)=1+f(p−1)p

修正的公式

上并行加速不仅受限于程序的串行分量,而且也受并行程序运行时的额外开销影响

极限情况与条件

- 对于理想情况:当 p → ∞ p\to\infty p→∞时取极限

S = 1 f S=\frac{1}{f} S=f1

- 对于实际情况:当 p → ∞ p\to\infty p→∞时取极限

S = 1 f + W o W S=\frac{1}{f+\frac{W_o}{W}} S=f+WWo1

出发点

- 对于很多科学计算,实时性要求很高,即在此类应用中时间是个关键因素,而计算负载是固定不变的。为此在一定的计算负载下,为达到实时性可利用增加处理器数来提高计算速度;

- 因为固定的计算负载是可分布在多个处理器上的,这样增加了处理器就加快了执行速度,从而达到了加速的目的。

含义

它意味着随着处理器数目的无限增大,并行系统所能达到的加速之上限为 1 f \frac{1}{f} f1

Gustafson加速定律

原公式

归一化公式

修正的公式

极限情况与条件

当 p充分大时,S′与p几乎成线性关系,其斜率为1-f。

出发点

- 对于很多大型计算,精度要求很高,即在此类应用中精度是个关键因素,而计算时间是固定不变的。此时为了提高精度,必须加大计算量,相应地亦必须增多处理器数才能维持时间不变;

- 除非学术研究,在实际应用中没有必要固定工作负载而使计算程序运行在不同数目的处理器上,增多处理 器必须相应地增大问题规模才有实际意义。

含义

意味着随着处理器数目的增加,加速几乎与处理器数成比例的线性增加,串行比例 f不再是程序的瓶颈。

注意,Wo是p的函数,它可能随 p增大、减小或不变。一般化的 Gustafson 定律欲达到线性加速必须使 Wo随 p减小,但这常常是困难的。

Sun和Ni定律 - 存储受限的加速定律

原公式

S ′ ′ = f W + ( 1 − f ) G ( p ) W f W + ( 1 − f ) G ( p ) W p S''=\frac{fW+(1-f)G(p)W}{fW+(1-f)G(p)\frac{W}{p}} S′′=fW+(1−f)G(p)pWfW+(1−f)G(p)W

归一化公式

S ′ ′ = f + ( 1 − f ) G ( p ) f + ( 1 − f ) G ( p ) p S''=\frac{f+(1-f)G(p)}{f+(1-f)\frac{G(p)}{{p}}} S′′=f+(1−f)pG(p)f+(1−f)G(p)

修正的公式

极限情况与条件

- 当 G ( p ) = 1 G(p)=1 G(p)=1时:变为 1 f + ( 1 − f ) p \frac{1}{f+\frac{(1-f)}{p}} f+p(1−f)1( Amdahl加速定律)

- 当 G ( p ) = p G(p)=p G(p)=p时:变为 f + p ( 1 − f ) f+p(1-f) f+p(1−f)(Gustafson加速定律;当 G(p)>p时,它相应于计算负载比存储要求增加得快)

基本思想

其基本思想是只要存储空间许可,应尽量增大问题规模以产生更好或更精确的解(此时可能使执行时间略有增加)。换句话说,假若有足够的存储容量,并且规模可扩放的问题满足 Gustafson定律规定的时间要求,那么就有可能进一步增大问题规模求得更好或更精确的解。 ,它相应于计算负载比存储要求增加得快,此时Sun和Ni加速均比 Amdahl加速和 Gustafson加速为高。

并行算法的设计基础

并行算法基本概念

- 并行算法(ParallelAlgorithm)是一些可同时执行的诸进程的集合,这些进程互相作用和协调动作从而达到给定问题的求解。

- 数值计算是指基于代数关系运算的一类诸如矩阵运算、多项式求值、求解线性方程组等数值计算问题。求解数值计算问题的算法称为数值算法(NumericalAlgorithm)。

- 非数值计算是指基于比较关系运算的一类诸如排序、选择、搜索、匹配等 符号 处 理 问 题。求 解 非 数 值 计 算 问 题 的 算 法 称 为 非 数 值 算 法(Non_NumericalAlgorithm)。

- 同步算法(SynchronizedAlgorithm)是指算法的诸进程的执行必须相互等待的一类并行算法。

- 异步算法(ASynchronizedAlgorithm)是指算法的诸进程的执行不必相互等待的一类并行算法。

- 分布算法(DistributedAlgorithm)是指由通信链路连接的多个场点(Site)或节点,协同完成问题求解的一类并行算法。

- 在 局 网 环 境 下 进 行 的 计 算 称 为 分 布 计 算(Distributed Computing)。

- 把 工 作 站 机 群 COW(ClusterofWorkstations)环境下进行的计算称为网络计算(NetworkComputing)。

- 把基于Internet的计算则称为元计算(MetaComputing)。

- 确定算法(DeterministicAlgorithm)是指算法的每一步都能明确地指明下一步应该如何行进的一种算法。

- 随机算法(RandomizedAlgorithm)是指算法的每一步,随机地从指定范围内选取若干参数,由其来确定算法的下一步走向的一种算法。

并行计算模型基本概念

所谓计算模型实际上就是硬件和软件之间的一种桥梁,使用它能够设计分析算法,在其上高级语言能被有效地编译且能够用硬件来实现。

PRAM(ParallelRandomAccessMachine)模型

并行随机存取机器,也称之为共享存储的SIMD模型,是一种抽象的并行计算模型。在这种模型中,假定存在着一个容量无限大的共享存储器;有有限或无限个功能相同的处理器,且其均具有简单的算术运算和逻辑判断功能;在任何时刻各处理器均可通过共享存储单元相互交换数据。

分类

根据处理器对共享存储单元同时读、同时写的限制,PRAM 模型又可分为:

- 不允许同时读和同时写(Exclusive_ReadandExclusive_Write)的 PRAM 模 型,简 记之 为 PRAM_EREW;(最弱计算模型)

- 允许同 时读 不 允 许同 时 写(Concurrent_ReadandExclusive_Write)的 PRAM 模型,简记之为 PRAM_CREW。

- 允许同时读和同时写(Concurrent_ReadandConcurrent_Write)的PRAM 模型,简记之为PRAM_CRCW。(最强计算模型)

- 只允许所有的处理器 同时写相同的数,此时称为 公共(Common)的PRAM_CRCW,简记之为CPRAM_CRCW;

- 只允许最优先的处理器先写,此时称为优先(Priority)的PRAM_CRCW,简记之为PPRAM_CRCW;

- 允许任意 处 理 器 自 由 写,此 时 称 为 任 意(Arbitrary)的 PRAM_CRCW,简 记 之 为APRAM_CRCW。

优点

- 特别适合于并行算法的表达、分析和比较;

- 使用简单,很多诸如处理器间通信、存储管理和进程同步等并行机的低级细节均隐含于模型中;

- 易于设计算法和稍加修改便可运行在不同的并行机上;

- 有可能在 PRAM 模型中加入一些诸如同步和通信等需要考虑的问题。

缺点

- PRAM 是一个同步模型,这就意味着所有的指令均按锁步方式操作,用户虽感觉不到同步的存在,但它的确是很费时的;

- 共享单一存储器的假定,显然不适合于分布存储的异步的 MIMD机器;

- 假定每个处理器均可在单位时间内访问任何存储单元而略去存取竞争和有限带宽等是不现实的。

推广

- 存储竞争模型,它将存储器分成一些模块,每个模块一次均可处理一个访问,从而可在模块级处理存储器的竞争;延迟模型,它考虑了信息的产生和能够使用之间的通信延迟;

- 局部 PRAM 模型,此模型考虑到了通信带宽,它假定每个处理器均有无限的局存,而访问全局存储器是较昂贵的;

- 分层存储模型,它将存储器视为分层的存储模块,每个模块由其大小和传送时间表征,多处理机由模块树表示,叶为处理器;

- 异步PRAM模型

异步PRAM模型

分相(Phase)PRAM 模型是一个异步的 PRAM 模型,简记之为APRAM,系由p个处理器组成,其特点是每个处理器都有其局存、局部时钟和局部程序;

特点

- 处理器间的通信经过共享全局存储器;无全局时钟,各处理器异步地独立执行各自的指令;

- 处理器任何时间依赖关系需明确地在各处理器的程序中加入同步(路)障(SynchronizationBarrier);

- 一条指令可在非确定(无界)但有限的时间内完成。

指令类型

- 全局读:将全局存储单元中的内容读入局存单元中;

- 局部操作:对局存中的数执行操作,其结果存入局存中;

- 全局写:将局存单元中的内容写入全局存储单元中;

- 同步:同步是计算中的一个逻辑点,在该点各处理器均需等待别的处理器到达后才能继续执行其局部程序。

BSP(BulkSynchronousParallel)模型

性质和特点

- 将处理器和选路器分开,强调了计算任务和通信任务的分开,而选路器仅施行点到点的消息传递,不提供组合、复制或广播等功能

- 将处理器和选路器分开,强调了计算任务和通信任务的分开,而选路器仅施行点到点的消息传递,不提供组合、复制或广播等功能

- 如果能合适地平衡计算和通信,则 BSP模型在可编程性方面具有主要的优点

- 为PRAM 模型所设计的算法,均可采用在每个BSP处理器上模拟一些PRAM 处理器的方法实现之。

logP模型(logPModel)

是一种分布存储的、点到点通信的多处理机模型,其中通信网络由一组参数来描述,但它并不涉及到具体的网络结构,也不假定算法一定要用显式的消息传递操作进行描述。

参数

- l(Latency)表示在网络中消息从源到目的地所遭到的延迟;

- o(Overhead)表示处理器发送或接收一条消息所需的额外开销(包含操作系统核心开销和网络软件开销),在此期间内它不能进行其它的操作;

- g(Gap)表示处理器可连续进行消息发送或接收的最小时间间隔;

- P(Processor)表示处理器/存储器模块数。

并行算法的一般设计策略

串行算法直接并行化

- 对于一类具有内在顺序性的串行算法,则恐难于直接并行化。

- 并非任何优秀的串行算法都可以产生好的并行算法,相反一个不好的串行算法则有可能产生很优秀的并行算法。

从问题描述开始设计并行算法

对于有些问题,现有的串行算法恐难直接将其并行化,此时要从问题的描述出发,寻求可能的新途径,设计出一个新的并行算法。但这并不是说完全排除某些串行算法设计的基本思想,而是更着重从并行化的具体实现上开辟新的设计方法。

借用已有算法求解新问题

所谓“借用法”是指借用已知的某类问题的求解算法来求解另一类问题。不但要从问题求解方法的相似性方面仔细观察,寻求问题解法的共同点;而且所借来的方法要用得合算,效率要高,从而能达借用的目的。

并行算法的基本设计技术

划分时关键在于如何将问题进行分组,使得子问题较容易并行求解,或者子问题的解较容易被组合成原问题的解。

划分求解的基本步骤

- 将给定的问题劈成p个独立的几乎等尺寸的子问题;

- 用p台处理器并行求解诸子问题。

均匀划分技术

假定待处理的序列长为n,现有p台处理器,一种最基本的划分方法就是均分划分(UniformPartition),系将n个元素分割成p段,每段含有n/p个元素且分配给一台处理器。

对数划分技术

假定待处理的序列长为n,现欲将其分段处理。取每第ilogn(i=1,2,…)个元素作为划分元素,而将序列划分成若干段,然后分段处理之。

功能划分技术

欲从长为n的序列中选取前m个最小者,可以将长为n的序列划分成等长的一些组,每组中的元素数应大于或等于m(最后一组除外)。然后各组并行处理。

并行算法的一般设计过程

PCAM基本步骤

- 划分:将整个计算分解成一些小的任务,其目的是尽量开拓并行执行的机会。

- 通信:确定诸任务执行中所需交换的数据和协调诸任务的执行,由此可检测上述划分的合理性。

- 组合:按性能要求和实现的代价来考察前两阶段的结果,必要时可将一些小的任务组合成更大的任务以提高性能或减少通信开销。

- 映射:将每个任务分配到一个处理器上,其目的是最小化全局执行时间和通信成本以及最大化处理器的利用率。

划 分

所谓划分,就是使用域分解或功能分解的办法将原计算问题分割成一些小的计算任务,以充分揭示并行执行的机会。

- 目的:充分开拓算法的并发性和可扩放性;

- 方法:先集中数据的分解(称域分解),然后是计算功能的分解(称功能分解),两者互为补充;

- 要点:力图避免数据和计算的复制,应使数据集和计算集互不相交。

通 信

由划分所产生的诸并行执行的任务,一般而言都不能完全独立执行,一个任务中的计算可能需要用到另一个任务中的数据,从而就产生了通信要求。所谓通信,就是为了进行并行计算,诸任务之间所需进行的数据传输。

通信模式

- 局部/全局通信:局部通信时,每个任务只与较少的几个近邻通信;全局通信中,每个任务与很多别的任务通信。

- 结构化/非结构化通信:结构化通信时,一个任务和其近邻形成规整结构(如树、网格等);非结构化通信中,通信网则可能是任意图。

- 静态/动态通信:静态通信,通信伙伴的身份不随时间改变,动态通信中,通信伙伴的身份则可能由运行时所计算的数据决定且是可变的。

- 同步/异步通信:同步通信时,接收方和发送方协同操作;异步通信中,接收方获取数据无需与发送方协同。

组 合

从抽象转到具体,即重新考察在划分和通信阶段所作的抉择,力图得到一个在某一类并行机上能有效执行的并行算法。 目的是通过合并小尺寸的任务来减少任务数,但它仍可能多于处理器的数目。

映 射

在设计的最后阶段,我们要指定每个任务到哪里去执行,此即映射(Mapping)。开发映射的主要目的是减少算法的总的执行时间。

基本策略

- 把那些能够并发执行的任务放在不同的处理器上以增强并行度

- 把那些需频繁通信的任务置于同一个处理器上以提高局部性。