数字电路(一)

1、例题

1、进行DA数模转换器选型时,一般要选择主要参数有( A)、转换精度和转换速度。

A、分辨率

B、输出电流

C、输出电阻

D、模拟开关

2、下图所示电路的逻辑功能为( B)

A、与门

B、或门

C、与非门

D、或非门

分析该电路,P=A·B,Q=A+B,故F=A+B,即该电路进行的是或运算,~ (~A & ~B) = A + B

3、下面哪个操作符的优先级最低(A)?

A、&&

B、&

C、|

D、^

对于优先级,条件操作符的优先级最低,其次是逻辑操作符,因此&&的优先级在选项中是最低的。优先级:&>^>|>&&

4、在多谐振荡器、单稳态触发器、施密特触发器,(C)中常用于波形的变换和整形?

A、多谐振荡器

B、单稳态触发器

C、施密特触发器

5、下面的代码表示的是(A)?

always @(e or d)

begin

if(e)

Q=d;

end

A、锁存器

B、触发器

6、现在有assign sum=a[4:0]+b[4:0]+c[4:0]+d[4:0]+e[4:0]+f[4:0],为了保证sum不溢出,sum的最小位宽需要多少位( C )?

A、6

B、7

C、8

D、9

官方解析:a[4:0]+b[4:0]需要6位,c[4:0]+d[4:0]需要6位,e[4:0]+f[4:0]需要6位;

a[4:0]+b[4:0]+c[4:0]+d[4:0]需要7位,因此sum最少需要8位。

7、现有一片32×8位的RAM,若想用这片RAM构成一个1K×32位的RAM,需要用到几片( C )?

A、32

B、64

C、128

D、256

需要用到(1000/32)*(32/8)=125 <128片

8、下面哪个选项中,不会综合出latch (C )?

A、always后面的信号列表中,所列出的信号不完整

B、使用casez语句

C、if-else语句中缺少else语句

D、case语句中缺乏default,或未列出所有可能的情况

官方解析: 对于if-else和always后面的信号列表所列的信号不完整,都可能导致会为了维持原来的电路的电路状态,从而生成锁存器。对于case,当出现case分支中没有列出的情况时,电路状态保持原来的状态不变,于是就会生成锁存器来保存状态。

9、下面哪个选项中哪些是可编程逻辑器件(A、B、C)?

A、FPLA

B、PLA

C、FPGA

D、TTL

官方解析:可编程逻辑器件有FPLA、PAL、GAL、EPLD、CPLD、FPGA、GDS

10、下列能够将数据串延时8个CP时间的是( B )。

A、8位加法器

B、8位移位寄存器

C、8位并行寄存器

D、8位乘法器

官方解析:【分析】具有数据串延时作用的电路是移位寄存器。选择B。

11、以下错误的是(B )

A、数字比较器可以比较数字大小

B、实现两个一位二进制数相加的电路叫全加器

C、实现两个一位二进制数和来自低位的进位相加的电路叫全加器

D、编码器可分为普通全加器和优先编码器

这里选的是错误的,请注意。

12、下列器件中,能够用于串并转换的是(C)

A、编码器

B、译码器

C、移位寄存器

D、累加器

官方解析:【分析】移位寄存器输入方式是串行输入,输出方式可以串行也可以并行。选择C。

13、下列选项中,数值最小的是(A)

A、十六进制数0.16

B、八进制数0.22

C、十进制数0.14

D、二进制数0.01

解析:在任意进制中,每一位的权值是其进制值的幂次方,小数点后的权值为进制值的-1次方,-2次方,-3次方,所以十六进制0.16换为十进制就是116-1次方+616-2次方等于0.0859375最小

14、12位D/A转换器当输入数字量只有最低位为1时,输出电压为0.001V,若输入数字量只有最高位为1时,则输出电压为( C )V。

A、0.0257

B、2.058

C、2.048

D、都不是

官方解析:【分析】Vo=2048*0.001V=2.048V。选择C。

15、8位DAC转换器对应的分辨率为( )。

A、0.0013

B、0.0025

C、0.0094

D、0.0039

16、将二进制数1111转换为格雷码形式为(B)

A、1001

B、1000

C、1010

D、1100

17、相对于静态存储器来说,动态存储器消耗的功耗更(C),存取速度更(C)。

A、小,慢

B、小,快

C、大,慢

D、大,快

18、在A/D和D/A转换器中,位数越高,分辨率(A)。

A、越高

B、越低

C、一样

D、不确定

官方解析:【分析】D/A和AD转换器,位数越高,分辨率越高

19、在Verilog语言中,module和endmodule之间是(C)的;begin和end之间的内部语句是(C)的。

A、顺序执行,顺序执行

B、顺序执行,并行执行

C、并行执行,顺序执行

D、并行执行,并行执行

20、与数据分配器有着相同的基本电路结构形式的是( D )。

A、减法器

B、编码器

C、加法器

D、译码器

官方解析:【分析】数据分配器和译码器有着相同的基本电路结构形式。选择D。

21、下列关于进制转换的说法中错误的是(B)

A、任何二进制数都可以精准转换为等值的十进制数

B、任何十进制数都可以精准转换为等值的二进制数

C、任何二进制数都可以精准转换为等值的十六进制数

D、任何十六进制数都可以精准转换为等值的二进制数

官方解析:二进制能够精准的转换为十进制,但是十进制不能精准的转换为二进制,如(0.1)10,便不能精准转换为二进制数。十六进制数与二进制数可以精确地相互转换,故B错误。

22、数字信号时间上是(A)的,数量上是(A)的

A、离散,离散

B、连续,离散

C、离散,连续

D、连续,连续

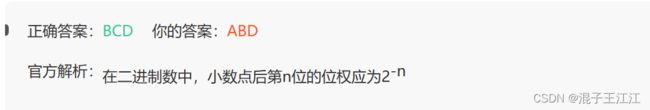

23、下列说法中正确的是(B、C、D)

A、在二进制数中,小数点后第n位的位权是2-(n-1)

B、在二进制数中,小数点前第n位的位权是2n-1

C、二进制数最多需要两种数字符号进行表示

D、28)16=(50)8

2、参考资料

牛客