SOC FPGA之流水灯设计

一、DS-5简介

Altera Soc EDS开发套件的核心是Altera版ARM Development Studio 5(DS-5)工具包,为SoC器件提供了完整的嵌入式开发环境、FPGA自适应调试和对Altera工具的兼容。

1.1 DS-5 eclipse破解

首先下载破解器

然后进入cmd运行,进入到破解器所在文件夹

然后输入patcher.exe --license ?:licensepath

最后显示.dat文件即可,将license添加到eclipse中就好了

1.2 ARM编译器

ARM编译器用于生成面向ARM、Thumb、Thumb22、VFP和NEON指令集的应用程序。

ARM编译器工具链可用于编译由C、C++或ARM汇编语言源代码编写的程序,可以为32位ARM、16位Thumb和Thumb-2指令集生成优化代码,并支持完整的符号ISO标准的C和C++代码,通过向量化NEON编译器支持NEON SIMD指令集。

1.3 GNU编译器

Altera Soc EDS自带的裸机GNU编译工具是基于ARM架构的处理器,用于编译Linux应用程序,可以直接从命令行直接启动,也可以在Eclipse中创建Linux可执行程序项目从而调用此套编译器。

二、基于ARM编译器的流水灯实例

2.1 创建项目

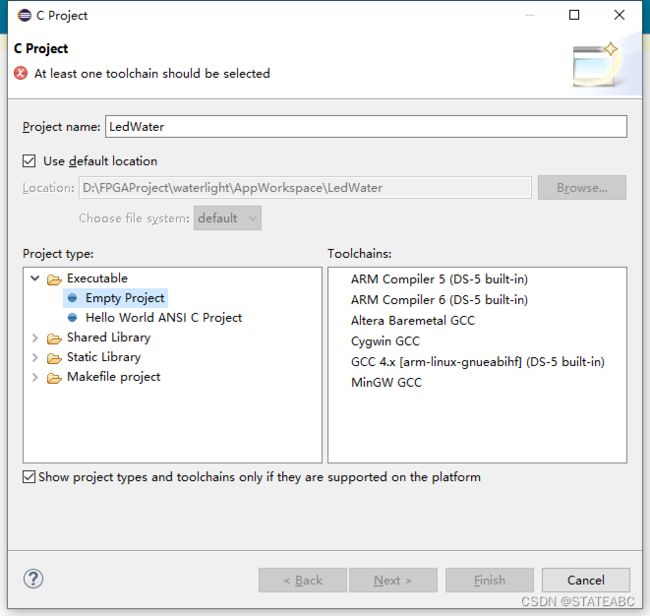

新建C Project

用SOC EDS提供的HALIB中给的API访问板上硬件,所以需要在项目编译选项中添加HWLIB路径

选择主菜单Project->Properties,在弹出的Properties for LedWater对话框中点击Includes

本实例要添加的是项目编译时需要包含的HALIB路径,点击Include path(-I),通过File system选择

在C项目中添加主程序main.c,File->New->Source File

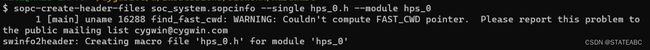

创建硬件设备描述头文件hps_0.h

SOC EDS提供了由Qsys硬件系统信息转换为软件开发所需设备描述头文件的工具swinfo2header,通过Shell进入Qsys工程所在目录并输入

sopc-create-header-files soc_system.sopcinfo -single hps_0.h -module hps_0根据.sopcinfo文件生成hps_0.h文件,并将其拷贝至Eclipse当前项目目录中

另一种生成hps_0.h文件是编写Shell脚本generate_hps_qsys_header.sh

#!/bin/sh

sopc-create-header-files\

"/cygdrive/d/chapter7/Hardware/soc_system.sopcinfo"

--single hps_0.h

--module hps_0脚本文件编译完成后将其保存在当前项目目录中,在命令行中切换到当前项目目录,然后执行哎脚本,即可在当前项目目录下生成 hps_0.h

在Eclipse中右键点击项目名称选择Refresh就可以看到hps_0.h文件已经被添加至当前项目

将

#include

#include

#include "socal/hps.h"

#include "socal/socal.h"

#include "socal/alt_rstmgr.h"

#include "socal/alt_l4wd.h"

#include "hwlib.h"

#include "alt_mpu_registers.h"

#include "alt_watchdog.h"

#include "alt_clock_manager.h"

#define WDOG_RESET_KEY 0x00000076

#define ALT_WDOG_RST_WIDTH 8 //8个或更多MPU时钟周期

bool cpu_wdog_in_gpt_mode(void)

{

return !(alt_read_word(CPU_WDTGPT_TMR_BASE + WDOG_CTRL_REG_OFFSET) & WDOG_WDT_MODE);

}

/****************************************************************************************/

/* 启动指定看门狗定时器 */

/****************************************************************************************/

ALT_STATUS_CODE alt_wdog_start(ALT_WDOG_TIMER_t tmr_id)

{

ALT_STATUS_CODE ret = ALT_E_BAD_ARG; //返回值

uint32_t regdata; //定义数据变量

if (tmr_id == ALT_WDOG_CPU)

{

regdata = alt_read_word(CPU_WDTGPT_TMR_BASE + WDOG_CTRL_REG_OFFSET);

alt_write_word(CPU_WDTGPT_TMR_BASE + WDOG_CTRL_REG_OFFSET, regdata | WDOG_TMR_ENABLE);

ret = ALT_E_SUCCESS;

}

else if ((tmr_id == ALT_WDOG0) || (tmr_id == ALT_WDOG0_INIT))

{

regdata = alt_read_word(ALT_L4WD0_WDT_CR_ADDR);

alt_write_word(ALT_L4WD0_WDT_CR_ADDR, regdata | ALT_L4WD_CR_WDT_EN_SET_MSK);

ret = ALT_E_SUCCESS;

}

else if ((tmr_id == ALT_WDOG1) || (tmr_id == ALT_WDOG1_INIT))

{

regdata = alt_read_word(ALT_L4WD1_WDT_CR_ADDR);

alt_write_word(ALT_L4WD1_WDT_CR_ADDR, regdata | ALT_L4WD_CR_WDT_EN_SET_MSK);

ret = ALT_E_SUCCESS;

}

return ret;

}

/****************************************************************************************/

/* 重新加载计数器的倒数计时器,并重启看门狗定时器 */

/* 可以在看门狗定时器计数结束前任意时刻重启定时器 */

/* 本质上是清除中断 */

/****************************************************************************************/

ALT_STATUS_CODE alt_wdog_reset(ALT_WDOG_TIMER_t tmr_id)

{

uint32_t regdata; //定义读数据

if (tmr_id == ALT_WDOG_CPU)

{

regdata = alt_read_word(CPU_WDTGPT_TMR_BASE + WDOG_LOAD_REG_OFFSET);

alt_write_word(CPU_WDTGPT_TMR_BASE + WDOG_LOAD_REG_OFFSET, regdata); //验证硬件操作

if (cpu_wdog_in_wdt_mode())

{

alt_write_word((CPU_WDTGPT_TMR_BASE + WDOG_RSTSTAT_REG_OFFSET), WDOG_RST_STAT_BIT); //根据当前模式,清除复位位

}

else

{

alt_write_word((CPU_WDTGPT_TMR_BASE + WDOG_INTSTAT_REG_OFFSET), WDOG_INT_STAT_BIT); //清除中断状态位

}

}

else if ((tmr_id == ALT_WDOG0) || (tmr_id == ALT_WDOG0_INIT))

{

alt_write_word(ALT_L4WD0_WDT_CRR_ADDR, WDOG_RESET_KEY); //重启计数器,清除看门狗0定时器中断

}

else if ((tmr_id == ALT_WDOG1) || (tmr_id == ALT_WDOG1_INIT)) //重启计数器,清除看门狗1定时器中断

{

alt_write_word(ALT_L4WD1_WDT_CRR_ADDR, WDOG_RESET_KEY);

}

else { return ALT_E_BAD_ARG; }

return ALT_E_SUCCESS;

} ARM链接器支持分散加载机制,可通过一个描述性分散文件(*.scat)指定链接生成可执行影响存储器映射情况,使开发人员完全控制映像各部分的组织、布局情况。分散文件通常用于控制需要复杂存储器映射的映像。

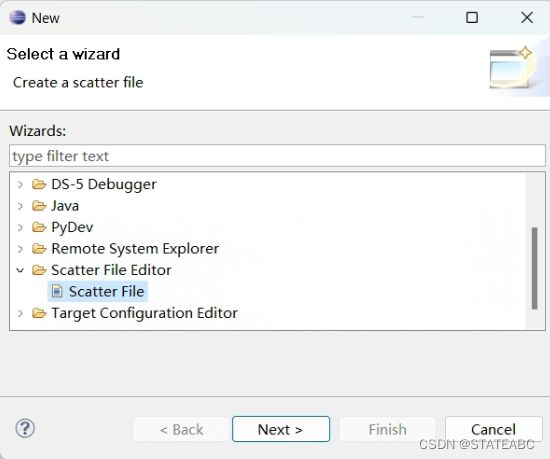

创建分散文件OnchiioRAM.scat,选择File->New->Other ,在Scatter File Editor中选择Scatter File

流水灯仅需对映像存储器映射进行控制,控制映像在片内65KB的OnchipRAM连续的存储区域加载执行,地址映射为0xFFFF0000~0xFFFFFFFF,编辑该分散文件内容如下:

PCRAM 0xFFFF0000 0x10000

{

;APP code region

APP_CODE +0

{

*(+RO,+RW,+ZI)

}

;Application heap and stack

ARM_LIB_STACKHEAP 0xFFFF8000 EMPTY 0x8000

{}

}保存编辑好的Scatter文件并保存该文件,再次打开该文件即可看到映像加载区和执行区两种存储器映像视图

编辑主程序文件main.c,使板上LED呈现流水灯实验现象

/************/

/*LedWater example*/

/************/

#include

#include "hwlib.h"

#include "alt_watchdog.h"

#include "socal\socal.h"

#include "socal\hps.h"

#include "socal\alt_gpio.h"

#include "socal\alt_rstmgr.h"

#include "socal\alt_l4wd.h"

#include "hps_0.h"

void delay(int time); //delay function declaration

int main()

{

int i = 0x01000000;

int j = 0x00000001;

alt_wdog_start (ALT_WDOG0); //start the watchdog

alt_write_word(ALT_RSTMGR_BRGMODRST_ADDR, 0x00000000); //remove bridge reset mode

alt_write_word(ALT_GPIO1_SWPORTA_DDR_ADDR,0x0F000000); //set GPIO1 direction as output

while( 1 )

{

alt_write_word(ALT_GPIO1_SWPORTA_DR_ADDR, i); //update led state controled by GPIO1 value

alt_write_word(ALT_LWFPGASLVS_OFST + LED_PIO_BASE, j); //update led state controled by FPGA peripheral

if ( (i & 0x0F000000) == 0x08000000 )i = 0x01000000;

else

i = i << 1;

if ( (j & 0x0000000F) == 0x00000008 )j = 0x00000001;

else

j = j << 1;

delay(100000000); //delay

alt_wdog_reset(ALT_WDOG0); //kick the watchdog

}

return 1;

}

void delay(int time)

{

int k;

for( k=0; k 2.2 项目编译

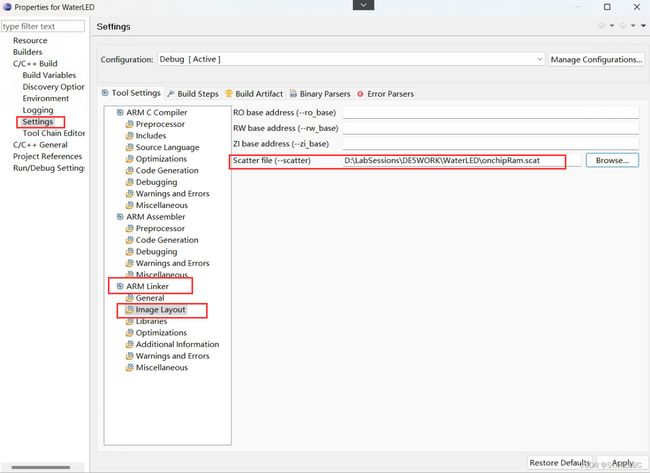

在编译之前需要为ARM Linker指定生成可执行程序所需的分散文件OnchiioRAM.scat

在Properties中选择ARM Linker->Image Layout,选择文件

在注册单选择Project->Build Project或者工程名右键Build Project

编译过程中可在Console窗口查看相关信息,整个编译过程为先启动ARM C Compiler进行编译生成目标文件,再启动ARM C Linker链接为可执行程序,最后生成LedWater.axf可执行程序映象

将之前生成的software\spb_bsp\uboot-socfpga\spl\u-boot-spl拷贝至当前目录,将.sof文件下载之FPGA中即可。