FPGA----IP核float(定点数转浮点数)使用

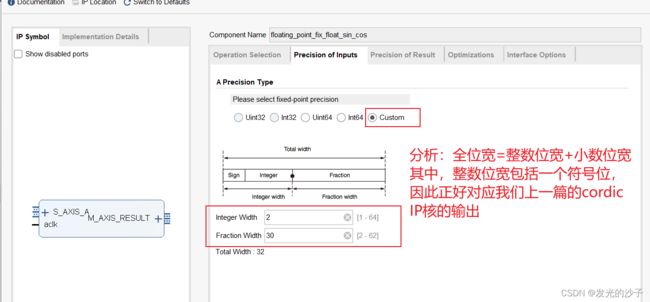

1、本文紧接上一篇文章,因为我们计算设定的32位的单精度浮点数,但是cordic IP核输出的是32位定点数x(符号位)_x(整数位)_xx,xxxx,xxxx,xxxx,xxxx,xxxx,xxxx,xxxx(小数位),为了方便使用float IP核的计算,因此我们需要将定点数转为浮点数。本片文章为全网第一篇带小数的定点数转浮点数的例程。

2、Floating-point IP核使用

实验任务:实现sin(±120°)32位定点数转浮点数操作,具体值怎么算的请参考上一篇文章

实验软硬件:ZCU106、Vivado 2019.1

实验过程:

①建立test_fix_to_float项目,并添加top、testbench文件,添加Floating-point IP核(这一步如果还不会,真别往下看了,好好复习以下前面的东西)

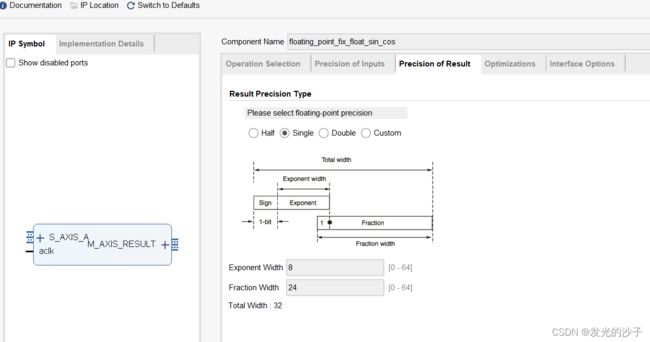

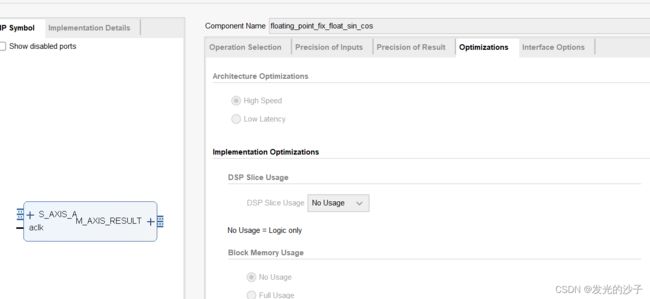

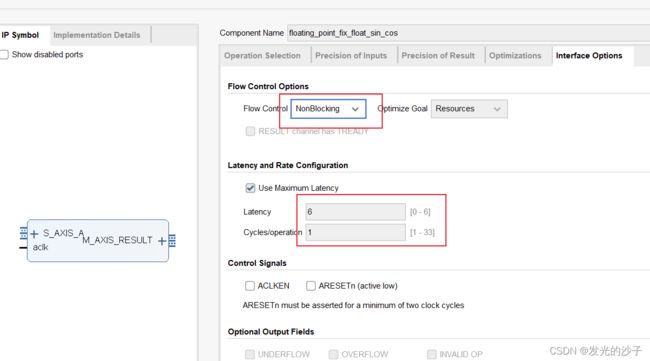

②Floating-point IP核做如下设置

`timescale 1ns / 1ps

//

// Company: 东北电力大学

// Engineer: Yang Zheng

//

// Create Date: 2021/12/31 22:57:23

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module top(

input clk,

input [31:0] s_axis_a_tdata_sin_cos_a,

input s_axis_a_tvalid_sin_cos_a,

output [31:0] m_axis_result_tdata_sin_cos_a,

input [31:0] s_axis_a_tdata_sin_cos_b,

input s_axis_a_tvalid_sin_cos_b,

output [31:0] m_axis_result_tdata_sin_cos_b,

input [31:0] s_axis_a_tdata_sin_cos_c,

input s_axis_a_tvalid_sin_cos_c,

output [31:0] m_axis_result_tdata_sin_cos_c,

output m_axis_result_tvalid_sin_cos_a,

output m_axis_result_tvalid_sin_cos_b,

output m_axis_result_tvalid_sin_cos_c

);

floating_point_fix_float_sin_cos uut_floating_point_fix_float_sin_cos_a(

.aclk(clk),

.s_axis_a_tvalid(s_axis_a_tvalid_sin_cos_a),

.s_axis_a_tdata(s_axis_a_tdata_sin_cos_a),

.m_axis_result_tvalid(m_axis_result_tvalid_sin_cos_a),

.m_axis_result_tdata(m_axis_result_tdata_sin_cos_a)

);

floating_point_fix_float_sin_cos uut_floating_point_fix_float_sin_cos_b(

.aclk(clk),

.s_axis_a_tvalid(s_axis_a_tvalid_sin_cos_b),

.s_axis_a_tdata(s_axis_a_tdata_sin_cos_b),

.m_axis_result_tvalid(m_axis_result_tvalid_sin_cos_b),

.m_axis_result_tdata(m_axis_result_tdata_sin_cos_b)

);

floating_point_fix_float_sin_cos uut_floating_point_fix_float_sin_cos_c(

.aclk(clk),

.s_axis_a_tvalid(s_axis_a_tvalid_sin_cos_c),

.s_axis_a_tdata(s_axis_a_tdata_sin_cos_c),

.m_axis_result_tvalid(m_axis_result_tvalid_sin_cos_c),

.m_axis_result_tdata(m_axis_result_tdata_sin_cos_c)

);

endmodule

`timescale 1ns / 1ps

//

// Company: 东北电力大学

// Engineer: Yang Zheng

//

// Create Date: 2021/12/31 23:00:20

// Design Name:

// Module Name: testbench

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module testbench(

);

reg clk;

reg a_valid_a = 1'b0;

reg [31:0] a_a = 32'b0;

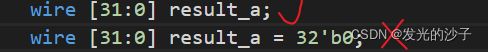

wire [31:0] result_a;

reg a_valid_b = 1'b0;

reg [31:0] a_b = 32'b0;

wire [31:0] result_b;

reg a_valid_c = 1'b0;

reg [31:0] a_c = 32'b0;

wire [31:0] result_c;

top uut_top(

.clk(clk),

.s_axis_a_tdata_sin_cos_a(a_a),

.s_axis_a_tvalid_sin_cos_a(a_valid_a),

.m_axis_result_tdata_sin_cos_a(result_a),

.s_axis_a_tdata_sin_cos_b(a_b),

.s_axis_a_tvalid_sin_cos_b(a_valid_b),

.m_axis_result_tdata_sin_cos_b(result_b),

.s_axis_a_tdata_sin_cos_c(a_c),

.s_axis_a_tvalid_sin_cos_c(a_valid_c),

.m_axis_result_tdata_sin_cos_c(result_c),

.m_axis_result_tvalid_sin_cos_a(m_axis_result_tvalid_sin_cos_a),

.m_axis_result_tvalid_sin_cos_b(m_axis_result_tvalid_sin_cos_b),

.m_axis_result_tvalid_sin_cos_c(m_axis_result_tvalid_sin_cos_c)

);

always #5 clk=~clk;

initial begin

clk = 1'b0;

#100;

a_valid_a <= 1'b1;

a_a <= 32'h376CF5D0;

a_valid_b <= 1'b1;

a_b <= 32'h376CF5D0;

a_valid_c <= 1'b1;

a_c <= 32'h376CF5D0;

#500;

a_valid_a <= 1'b1;

a_a <= 32'hc8930a30;

a_valid_b <= 1'b1;

a_b <= 32'hc8930a30;

a_valid_c <= 1'b1;

a_c <= 32'hc8930a30;

end

always @(posedge clk) begin

if (m_axis_result_tvalid_sin_cos_a == 1'b1

&& m_axis_result_tvalid_sin_cos_b == 1'b1

&& m_axis_result_tvalid_sin_cos_c == 1'b1) begin

a_valid_a <= 1'b0;

a_valid_b <= 1'b0;

a_valid_c <= 1'b0;

end

end

endmodule

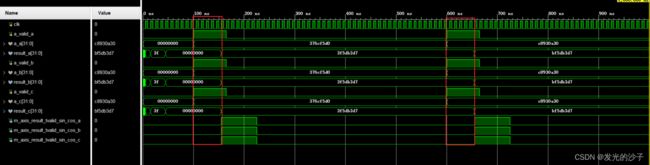

④结果分析

可以看到,结果在6个周期后输出