Type-C 接口为什么在不同的协议下带宽不同(引脚定义、协议等)

ThunderBolt 3/4 和 USB Type-C 有什么区别

其实 Thunderbolt 3是一个扩展集解决方案,它包括了 USB 3.1(10Gbps),并在单个 Type-C 接口中增加了 40Gbps 的 Thunderbolt 3/4 和 DisplayPort 1.2,还有PCIe。

也就是说,Type-C 是一个接口类型,而ThunderBolt 3/4 是 USB 的一个超集。

引脚定义

| 引脚(pin) | 信号 | 引脚(pin) | 信号 |

|---|---|---|---|

| A1 | GND | B12 | GND |

| A2 | SSTX+ | B11 | SSRX+ |

| A3 | SSTX- | B10 | SSRX- |

| A4 | VBUS | B9 | VBUS |

| A5 | CC1 | B8 | SBU2 |

| A6 | D+ | B7 | D- |

| A7 | D- | B6 | D+ |

| A8 | SBU1 | B5 | CC2 |

| A9 | VBUS | B4 | VBUS |

| A10 | SSRX- | B3 | SSTX- |

| A11 | SSRX+ | B2 | SSTX+ |

| A12 | GND | B1 | GND |

GND 是地线。

SSTX 和 SSRX 是差分高速线,用于 USB 3.x 或者 TBT/DP 备用模式(Alt-Mode),一共有 4 对。这里的“SS”是 SuperSpeed 的缩写,不过有时候会忽略掉直接叫 TX 和 RX。TX 是 数据发送端,RX 是 数据接收端,一般一个 TX 会连接到另外一个设备的 RX 端,反向亦然。需要注意的是,差分线传输速率和很多原因有关,例如数据处理芯片等

VBUS 是面向上游端口(Power Upstream Facing Port,UFP)供电,也就是对于接到接口上的设备供电,有 2 对。

CC 是 Configuration Channel 的缩写。例如可以用于传输 Power Delivery Protocol 的信号,实现例如 PD 协议。其他功能还有:检测线缆是否插入,检测线缆的方向等。更多信息可以看:https://www.microchipdeveloper.com/usb:tc-pins

D+/D- 是 USB 2.0 传统信号,也用于 USB 3.x,有 2 对。需要注意的是,如果是呼叫方(就是发送端),只有 a6 和 a7 两个会被使用,但是接收方 a6、a7、b6、b7 都会使用,如下(下图是一个被动线缆的公头插到一个PCB上的母口):

SBU 是 Sideband Use 的缩写,USB 不会使用这两个接口,仅被用于备用模式(Alt-modes)。SBU 在 DP Alt 模式时,会作为 DP 协议中 AUX_P/AUX_N 差分线(它的极性是可以根据正反插方向修改的),负责传输设备的 DPCD,EDID 等关键信息。

看上图可以发现,CC2 的引脚在发送端 VCONN,被用于电子标记电缆供电(Plug power)。CC1 和 CC2 都需要支持 CC(Configuration Channel)和 VCONN。

在技术意义上来说,Type-C 是分正面的,虽然用户插入的时候不分正反面,但是接口自身其实是分的。更多详情查看:https://www.microchipdeveloper.com/usb:type-c

以 NS 的电源适配器为例,NS 电源适配器支持 5V1.5A(7.5W)或 15V2.6A(39W)输出。下图是 Type-C 接头接线图:

可以看到接到了 G(地线)、cc(用于实现充电协议)和 V(传输电流的),然后这三个焊点通过 PCB 上的铜线连接到 Type-C 的引脚。

USB 数据流

USB 3.0 全名是Super Speed USB,最高支持 5 Gbps。(USB 3.0 现在也被叫做 USB 3.1 Gen 1)

USB 3.1 全名是 SuperSpeed Plus USB,最高支持 10 Gbps。(USB 3.1 现在也被叫做 USB 3.1 Gen 2)

这二者的数据信号是一样的:

- D+ 和 D- 差分半双工信号

- 两对全双工差分信号(SSTX-、SSTX+和SSRX-、SSRX+)

除了 USB 3.1 控制器支持的速率更高之外,还有一个不同之处在于全双工模式下编码不同:USB 3.0 是 8b/10b;USB 3.1 是 128b/132b。

简单来说:8b/10b 表示将 8 bit 的数据映射到 10 bit 上,支持编码流中 0 和 0 的均衡传输,还可以检测传输错误,损耗带宽 20%。128b/132b 也是一样的意思,只不过损耗降低到约 3%。

8b/10b 的实现和高速传输可以看这篇论文:《8B/10B Encoding and Decoding for High Speed Applications》

关于 USB 更多内容和对比可以看这篇文章:Understanding the USB 3.1 protocol

这里有个 PPT 有个不错的相关演示和总结:《TypeC (USB3.1/3.0) Introduction and Test solution》

DisplayPort 数据流

在 USB-C 的 DisplayPort Alt Mode 下(其他各种模式在 ThunderBolt 部分介绍)会占用 1、2 或者所有 4 对高速差分线。然后就要提到一个新的概念:HBR(DisplayPort High Bit Rate)。

HBR 决定了 DP 占用的每个高速差分线上的带宽。

- HBR 的带宽是 2.70 Gbps。

- HBR 2 的带宽是 5.40 Gbps。

- HBR 3 的带宽是 8.10 Gbps。

- UHBR 10 的带宽是 10.00 Gbps。

- UHBR 13.5 的带宽是 13.50 Gbps。

- UHBR 20 的带宽是 20.00 Gbps。

举个例子,DP 1.2 支持最高的是 HBR 2,所以最大带宽也就是 21.6 Gbps(5.40 Gbps x4),使用 8b/10b 编码,四通道最大数据速率也就是 17.28 Gbps。而 4k 60hz 10bit 每秒需要的带宽约为 14.93 Gbps,快占满了。所以 DP 1.2 最高支持 4k60hz。

HBR 版本取决于输出设备。例如 Intel 的核显从 Tiger Lake 开始才支持 HBR 3,这也是为什么例如 12600K 之类的新核显 CPU 支持的 DP 输出最大为 7680x4320@60hz,而 HDMI 都还是 4096x2160@60hz。

Dell 的这个文件说明了 Dell 支持 HBR 3 的设备:https://www.dell.com/support/kbdoc/zh-cn/000183937/dell-systems-support-hbr3-specifications

这里有个不错的 DP 的介绍和表格,讲的蛮清楚的:《DisplayPort Interface- What is DP?》

全功能 Type-C

在一根 Type-C 的线连接笔记本和 4K 显示器的时候,可能会遇到选择使用最高 4K 60hz 和 USB 2.0,还是使用最高 4K 30hz 和 USB 3.1(10 Gbps)的情况。这是为什么呢?

前文提到,USB 3.x 只用到 2 对高速差分线和 D+ 和 D- 差分半双工线,可以达到 10 Gbp 的速率。这样高速差分线就剩 2 对。 而 DisplayPort Alt Mode 可以占用 1/2/4 对高速差分线,那么也就刚好占用仅剩 2 条高速差分线(因为一般只占用 TX 引脚来发送显示信号和数据,所以是 2 条而不是 2 对 4 条),2 条高速差分线可以在 HBR 2 下实现 10.4 Gbps 的带宽。但是这满足不了 4k 60hz 10bit 每秒需要的带宽(约为 14.93 Gbps),所以只能实现 4k 30hz 10bit(约为 7.47 Gbps)。

这也是为什么 USB Type-C 单线只能做到 4k 30hz 10bit 和 USB 3.1 Gen2(10 Gbps)。

如果想要达到 4k 60hz 10bit,那么就得占用全部的 4 条高速差分线,那么 USB 就只能使用 D+ 和 D- 这两条差分半双工线,而这只能做到 USB 2.0。

所以想要 4k 60hz 10bit,那么 USB 只能有 USB 2.0。

ThunderBolt 3/4

首先需要知道,ThunderBolt 是双向双协议(PCIe 和 DisplayPort)。一个ThunderBolt 控制器会连接 4 条 PCIe 通道(最少 2 条),以及对应端口数量的 DP 数量(例如两个 ThunderBolt 接口,那么从视频输出设备,例如 CPU 核显或者间接通过 PCH,就会有两条 DP 线路连接到 ThunderBolt 控制器,一个 DP 线路占 4 条高速差分线)。

苹果有一个不错的文档来介绍 ThunderBolt 控制器的运行原理,可以看看:《Thunderbolt Technology Overview》

官方也有两个 PPT 来介绍 ThunderBolt 3,包括 ThunderBolt 3 控制器的运行原理:《ThunderBolt Update》和《ThunderboltTM 3 Technology and USB-C》

ThunderBolt 3/4 会用上全部的 4 对高速差分线。但是不同模式下,信号分配的不同。

- ThunderBolt Alt Mode(ThunderBolt 备用模式):使用支持 ThunderBolt 的线缆和设备之后,ThunderBolt 控制器将会在两个方向上各分配 2 对高速差分线,以此来创建两个完整的双工双向 40 Gbps 的通道(也有两个 ThunderBolt 3 端口共用一个 ThunderBolt 控制器的,或者带宽限制,这样一个接口的带宽只有 20 Gbps)。

- USB Only Mode(仅限 USB 模式):对于不支持 ThunderBolt 的 USB 设备或线缆,ThunderBolt 端口会激活 USB 控制器来支持 USB 3.x 或 2.0 信号。

- DisplayPort Alt Mode(DisplayPort 备用模式):当 DisplayPort 接口的显示器或适配器插入 ThunderBolt 接口时,控制器激活 DisplayPort Alt 模式。在这个模式下,4 对高速差分线会被指向同一个方向(也就是8 条线路同时输出),以此来支持高分辨率的输出(ThunderBolt 4 支持 DisplayPort 2.0,也就是最高 UHBR 20,最高带宽可以达到 80 Gbps(不算编码损耗),可以支持 3 台 10k 或者 1 台 16k 的显示器;ThunderBolt 3 支持 DP 1.2,也就是最高 HBR 2,最高带宽也就是 43.2 Gbps(不算编码损耗),可以支持 2 台 4k 60hz 10bit、1 台 4k 120hz 或者 1 台 5k 60hz的显示器)。

- USB/DP Combo Mode(USB/DP 混合模式):在这个模式下,控制器会自动调整 USB 和 DisplayPort 占用的通道,二者共同占用 4 对高速差分线。这是因为如此,支持雷电接口的显示器才可以做到 4K 甚至是 5K 60hz 的同时,还支持至少一个 USB 3.1 和千兆网口。

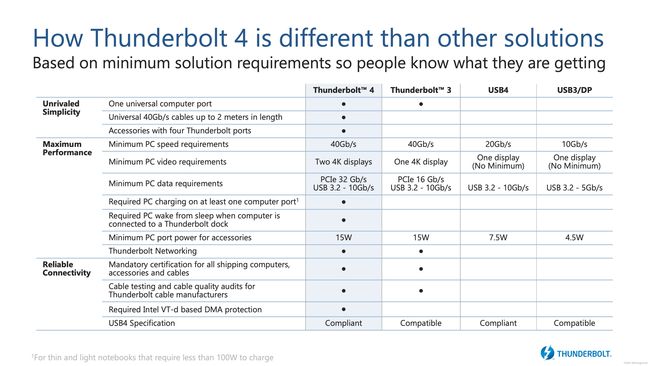

ThunderBolt 3 和 4 区别

如果查阅的话,会发现 ThunderBolt 4 与 3 相比有两个重大更新:

- 支持 DisplayPort 2.0(也就是说,支持 UHDR 20 了,这样 DP 带宽最高可以达到 80 Gbps,并且由于编码改为 128b/132b,损耗也更低了)

- 最低 PCIe 数据要求从 16 Gbps 增加到了 32 Gbps。

前者很容易理解,后者解释一下。首先需要知道 ThunderBolt 控制器和 PCIe 的关系。

一个 ThunderBolt 控制器至少要连接 2 条 PCIe 通道,最高 4 条。

为了性能最佳肯定是 4 条好,但是为什么要有两条的情况呢?

个人猜测,这是因为有些设备上 CPU 的 PCIe 通道不够用,所以不能强制每个 ThunderBolt 控制器都连接 4 条 PCIe 通道,从而来一一对应每条高速差分线。

比如 9900K 只有 16 条 PCIe 3.0,通过 DMI 3.0 连接芯片组(Platform Controller Hub,PCH),DMI 3.0 带宽只有 8 GT/s,相当于 4 条 PCIe 3.0(32 Gbps)。PCH 再扩展出 24 条 PCIe。

CPU 的这 16 条 PCIe 3.0 极少被用于连接 ThunderBolt 控制器。因为独立显卡、NVMe 硬盘、多余扩展 PCIe 插槽会占用完这部分。

再来看 PCH 部分,DMI 3.0 带宽只有 32 Gbps,而且要和声卡、网卡、无线网卡、硬盘等等设备共享带宽。所以通过 4 条 PCIe 接在 PCH 的 ThunderBolt 控制器虽然理论上可以达到 32 Gbps的带宽,但是极有可能会受 DMI 3.0 的带宽限制,很大的可能甚至会低于 2 条 PCIe 带来的 16 Gbps 带宽。而且因为多一步传递,延迟会高很多。

所以只有 Mac 和极少的 PC 上,ThunderBolt 控制器才会直接连接到 CPU。那么这部分设备的带宽比较稳定,也比较高,延迟也低。

那么 ThunderBolt 3 最低 PCIe 总带宽也就是 2 x 8 Gbps,也就是 16 Gbps,这也就是半速 ThunderBolt 3,一般标注带宽为 20 Gbps。连接了 4 条 PCIe 3.0 的带宽为 32 Gbps,也就是全速 ThunderBolt 3,一般标注带宽为 40 Gbps。

这里说明一下 ThunderBolt 的 20 Gbps 和 40 Gbps 的含义,这个含义并不是 PCIe 的带宽就是 20/40Gbps。而是传输任何类型的数据综合起来的一个最低带宽,包括视频信号、数据传输。

比如说 DP HBR2 模式下,4 条通道一共带宽就是 21.6 Gbps,两个显示器也就是 43.2 Gbps。

Dell 说实际 PCIe 带宽或者数据传输带宽只有 7-22 Gbps,而且是官方限制的)。另外在论坛上看到了相同的言论,只是说明了原因——因为有些控制器支持两个输出接口,所以留了 10 Gbps 给 USB 3.1 Gen 2。

也就是说 ThunderBolt 3 哪怕给了 4 条 PCIe 通道,直接连接在 CPU 上,也只能跑到 22 Gbps 左右。

ThunderBolt 4 的提升主要就是因为把最低 PCIe 带宽强制限制在 32 Gbps,这样对很多外接 PCIe 设备来说提升很多(而且可能移除了那 10 Gbps 的预留)。

需要注意的是,这个提升只是强制的,并不是因为 PCIe 升级了。

因为 Intel 从 Tiger Lake 开始就直接把 ThunderBolt 3/4 控制器放入 CPU 中,不占用任何可分配的 PCIe 通道。这样 Tiger Lake 的 ThunderBolt 3 就可以完整的使用 4 条 PCIe 3.0 的带宽了,也可以达到 32 Gbps。

而且如果查阅 ThunderBolt 4 的外置控制器,例如 Intel® JHL8540 Thunderbolt™ 4 Controller,会发现其是 PCIe 3.0 x4,如下图所示:

哦对这里还有一个帖子,里面介绍了一些显卡通过 ThunderBolt 连接的损耗:eGPU Performance Loss - PCI Express vs. Thunderbolt

希望可以帮到有需要的人~