PCIE常用缩写及含义

1.Egress和Ingress

在Switch中,数据流出的端口被称为Egress端口,Ingress指的数据流入Switch使用的端口。

2.DSP(Down Stream Port)和USP(Upper Stream Port)

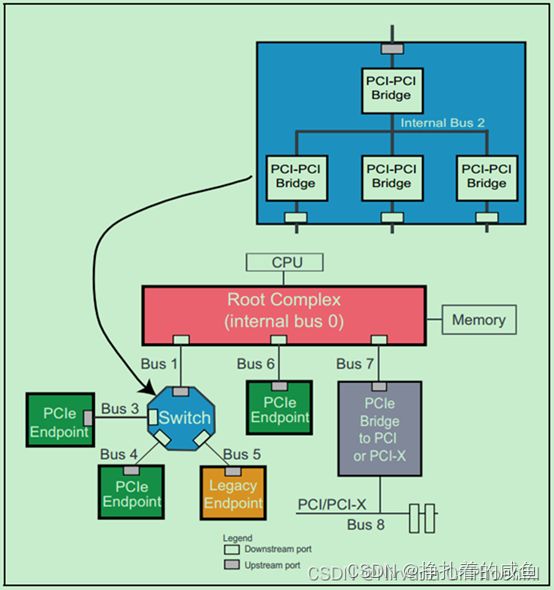

对每个功能设备来讲,用来连接上下游设备的端口统称为DSP或者USP(下图图例)。

在一个PCIe系统中,upstream port 和 downstream port是固定的,但是Ingress port 和 Egress port 是不固定的,和数据包的传输方向相关。

3.流量类别(TC)

TC 是在数据包内发送的一个 TLP 头字段,在端到端通过结构时没有改变。本地应用软件和系统软件应根据性能要求确定某个 TLP 使用什么样的 TC 标志。TC 字段是一个 3bits 长的字段,可以将不同的流量分成 8 种流量类别(TC0~TC7)。设备必须实现 VCO。设备或交换器要实现 TC-VC 映射逻辑,把给定 TC 号的 TLP 使用特定的 VC 号的缓冲区通过链路转发。PCIe 具有映射多个 TC到一个 VC 的能力,因而可通过提供有限数目的 VC 缓冲区支持来降低设备成本。

4.VC:虚拟通道

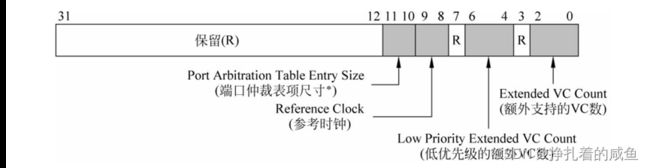

VC 是物理缓冲区,它通过使用发送和接收器虚拟信道缓冲区,提供一种在物理链路上支持多个独立逻辑数据流的手段。PCIe 设备可以最多实现 8 个 VC 缓冲区(VC0~VC7)。Extended VCCount字段的数值是除了 VC0以外所支持的 VC数量,为0时,表示仅支持 VC0;为 1~7时,表示额外支持1~7个 VC。

5.相位(Phase):

VC 仲裁表的每一项表示一个相位。规范定义了三种 WRR配置,分别有128、64、32个 表项数。具体设备所能支持的仲裁表项的个数由端口 VC能力寄存器2中的 VCArbitrationCapability字段 来报告,表的大小通过写入端口 VC控制寄存器中 VC ArbitrationSelect字段的值来选择(参见图下)。

8.LBC、DBI、ELBI和CDM

LBC(Local Bus Controller):

EP 的 LBC module 给对端 USP 或本地 CPU 提供一种通过 DBI 访问 CDM 内部寄存器及 ELBI 外部应用寄存器的机制。

DBI(data bus interface):

是synopsys定义的访问PCIe寄存器的接口,PCIe协议规定了两种配置空间:PCI Configuration Space和 PCIe Extend configuration Space。而往往IP的生成商,会加入一个属于自己的配置空间,synopsys添加的配置空间为:Port logic Synosys Register。

如下图,EP 侧的 CPU 可以通过 DBI 接口 PCIe Controller 的 CDM 内部寄存器,也可以访问 ELBI 外部应用寄存器。

ELBI(External Local Bus Interface):

把 PCIe Controller 收到的 Inbound 寄存器读写请求转发到外部应用寄存器。

CDM(Configuration-Dependent Module):含标准的 PCIe 配置空间及 PCIe Controller 指定的寄存器空间(端口逻辑寄存器)。

9.PCLE、VIP涉及的模块缩写&定义说明:

PMC: Power Management Controller

LBC : Local Bus Controller

DBI : Data Bus Interface

MSG_GEN: MessageGeneration Module

HOT PLUG:Hot Plug ControlModule

RBYP: Receive Bypass Interface

TRGT1: Receive Request Interface

ELBI: External Local Bus Interface

MSI: Message Signaled Interrupt (MSI) Interface,

MSI-X Interface,在DPDK中选择的中断模式,使用此接口。

XALI 0/1/2 : Transmit Interfaces 0/1/2

VMI : Vendor Message Interface

SII : System Information Interface

10.PCIE controller和PCIE PHY:

PIPE接口用于连接PCIE controller和PCIE PHY, controller用PIPE接口发送并行数给PHY用于并串转换等操作, PHY把串并转换得到的并行数通过PIPE接口送给controller。