FPGA 光纤传输IP核的使用

FPGA - Vivado - 光纤IP核的使用

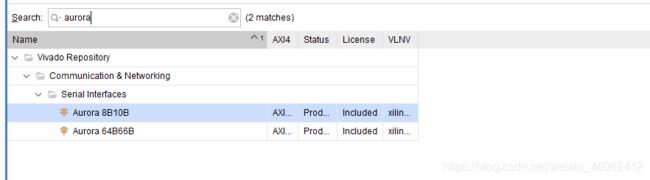

Vivado 的IP核一共分为两种, 一种是64B66B编码的,还有一种是8B10B编码的.

具体的区别感兴趣的小伙伴可以自己去查一下哈,64B66B的无法自己制定数据位宽的,8B10B是可以制定两种不同的位宽.(其实也没啥用)

我们使用的是IP核自己生成的示例代码进行光纤回环的操作哈.

这种东西较为复杂没有必要去自己写,了解其中原理拿来直接用即可,反正资源摆在那里不用白不用.

一、IP核的创建

可以看到哈是两个IP核,我们选择8B10B.

Lane Width (Bytes) : 选择位宽(数据位宽)

Line Rate (Gbps): 设置光纤的速度单位是G

GT Refclk (MHz): 参考时钟和开发板有关系的,开发板多少就选多少.

INIT clk (MHz) : 初始化的时钟

DRP Clk (in MHz) : DRP时钟

Dataflow Mode : 数据流模式.

Interface : 数据传输的用户接口协议选择.

Little Endian Support : 数据保存在高位还是地位(勾上保存地位)

Lanes : 光纤口的通道个数.

其他默认即可

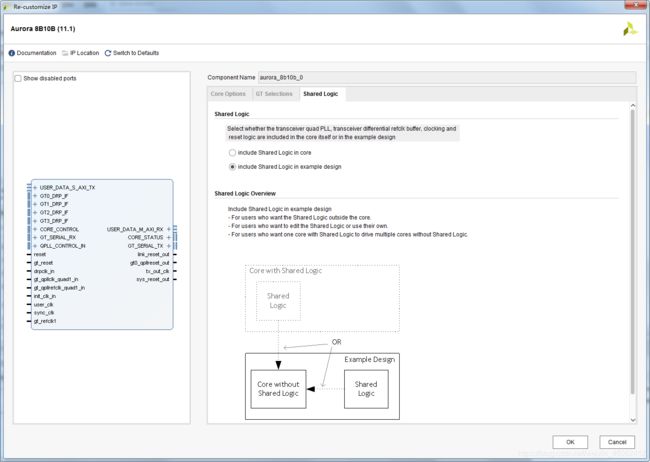

inclde Shared Logic in core : 不使用示例工程文件.

include Shared Logic in example design : 使用示例工程文件.

IP核建立完成 !

二、使用IP核示例代码

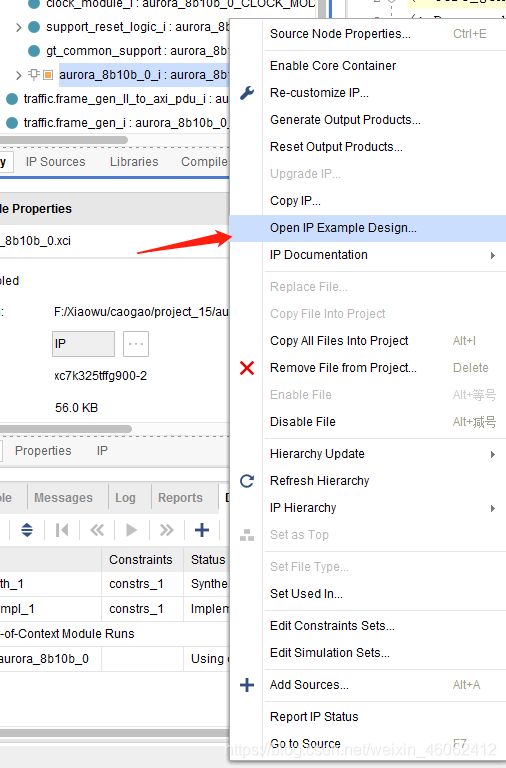

1.建立示例代码

建立完成后的样子 :

代码工程分析 :

aurora_8b10b_0_exdes : 顶层文件 .

aurora_module_i : 支持模块,如无特殊需求不需要修改.

clock_module_i : 将aurora的参考时钟,分频生成用户端需要使用的时钟.

suppor_reset_logic_i : 复位逻辑模块.

gt_common_support : 各个时钟处理,就是个pll.

traffic.frame_gen_ll_to_axi_pdu_i : 将用户输入输出的数据调整到AXI接口的数据(数据格式调整).

traffic.frame_gen_i : AXI的数据产生模块,产生随机数据. (修改非常方便)

traffic.frame_chk_axi_to_ll_pdu_i : 将AXI收到的接口数据,转换为用户可识别的数据. (无特殊需求不要修改)

traffic.frame_check_i : 错误识别模块,对错误的数据进行计数.(抓取信号的时候能看见错多少数据)

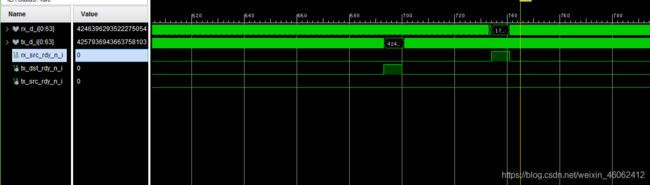

信号抓取 :

只要出数据就代表没错,一般示例文件都是官方调试完整的拿来直接用即可.

总结

Aurora 传输格式是 地位在前高位在后 !