总线基本概念

总线基本概念

为什么要用总线

总线是连接各个部件的信息传输线,是各个部件共享的传输介质。(如果没有总线,那么每新增一个组件,就需要增加若干线和其余组件相连)

在任何一个时刻,只能有一对设备(固件)使用总线,其余设备若想要使用则需要等待总线释放。(可拓展性强)

总线上信息的传送

串行(要传输的信息一位一位放到总线,接收方也是一位一位接收)

并行(要传输的数据多位同时放到总线,接收方也同时接收多位数据)需要多条数据线进行传输。如果传输距离长,数据线平行向外走,线和线之间会干扰,传输信号会变形,接收方很难接收到正确数据。通常并行传输距离短,集中在计算机机箱内部。

总线结构举例

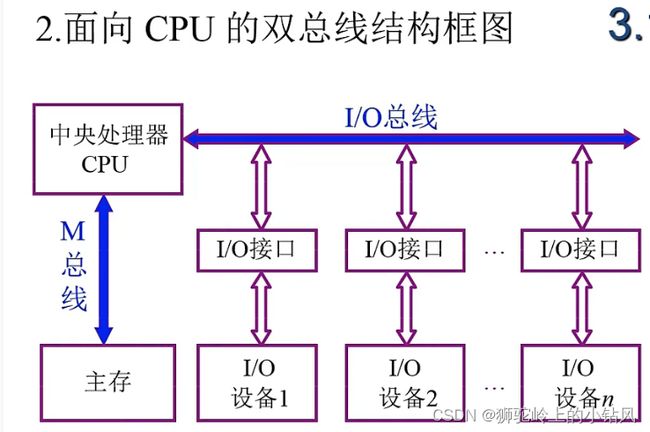

(假如主存和某一I/O设备在传输,那么CPU和主存之间就无法利用总线传输)

这里说的计数器是???

cpu运行程序时指令和数据都来自主存,两者信息交换非常繁忙。

这种处理方式弊端是主存和I/O设备没有直接信息通路。

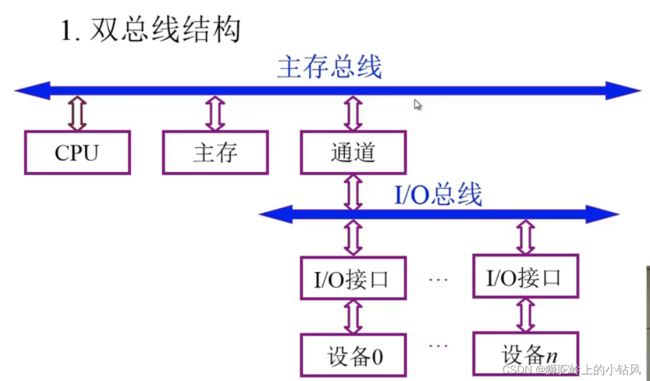

但是现在存储总线和系统总线依然不能同时工作。

总线的分类

- 片内总线 芯片内部总线(完成芯片内部不同部件的连接)

- 系统总线 芯片和芯片之间的连接,计算机各个部件的信息传输。分为以下三类

- 数据总线 一般是双向的,与机器字长,存储字长有关

- 地址总线 单向的,由cpu发出或主设备发出,与存储地址、I/O地址有关

- 控制总线 有出(存储器读写、总线允许,中断确认) 有入(中断请求、总线请求) (向系统各个部件传输控制信号,或系统各个部件把状态信号传出) 3. 通信总线 用于计算机系统之间或计算机系统和其他系统(如控制仪表、移动通信等)之间的通信。 传输方式分串行通信总线和并行通信总线。

总线结构

多总线结构

1.双总线结构

此处通道具有特殊功能的处理器,由通道对I/O统一处理(通道有自己的控制器和指令系统。能执行通道指令和通道程序)

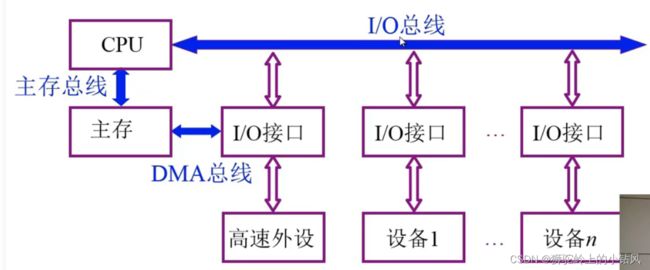

2.三总线结构

dma:外部设备直接访问系统内存

高速设备和主存信息交换用的DMA总线,低速设备依然使用I/O总线。

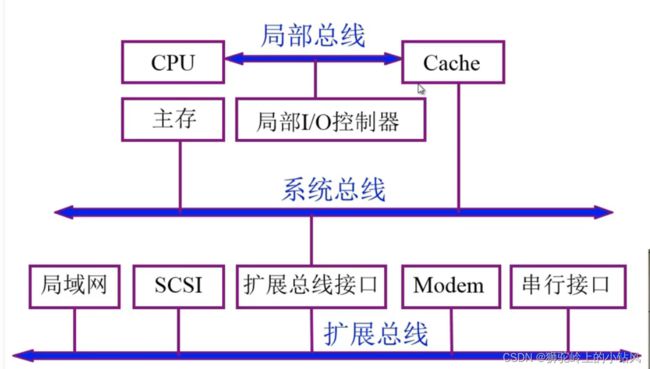

3.三总线结构的又一形式

cpu性能提高每年52%,内存每十年才会提升。内存速度是瓶颈。

小容量高速度cache,对主存数据进行缓存。cpu运行的指令和数据主要来自cache。

多种速度类型设备都连接到扩展总线上,会影响外部设备工作速度。

4.四总线结构

桥扩展出高速总线,低速设备连接到扩展总线上。

总线结构举例

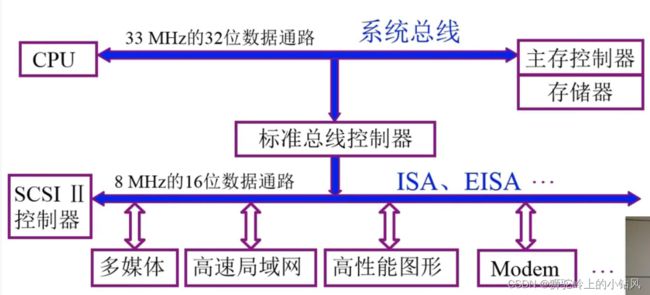

1.传统微型机总线结构

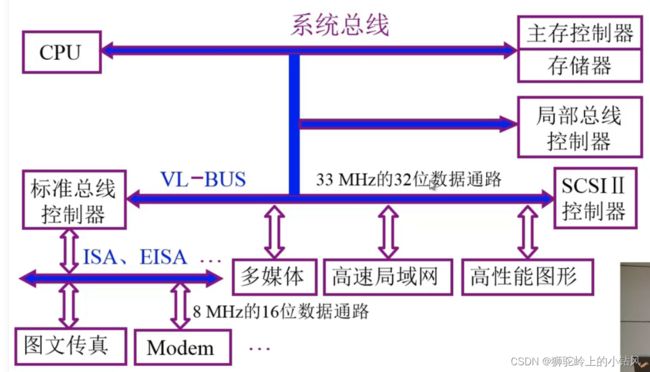

2. VL_BUS局部总线结构

VL_BUS是一条高速总线

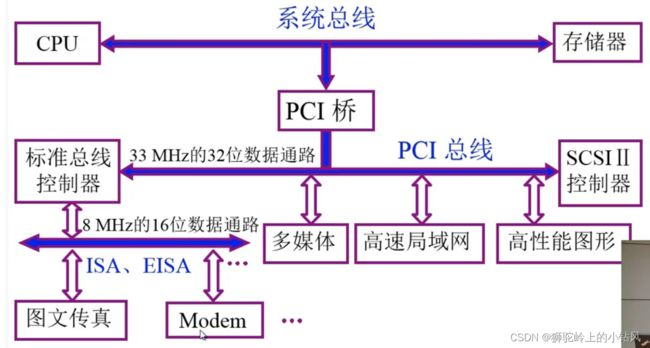

3.PCI总线结构

4.多层PCI总线结构

如果连接设备比较多,总线驱动能力不够,可通过PCI桥拓展。

总线控制

总线判优控制? 多个设备同时向总线发出占用总线请求,选择哪个设备使用总线?

占用总线后如何完成通讯过程,保证通讯过程正确性?

一,总线判优控制

1.基本概念

- 主设备(模块) 对总线有控制权 (提出总线占用申请,占用了总线后可以控制和另外一台设备工作)

- 从设备(模块) 响应从主设备发来的总线命令 (计算机系统中有设备既可以作为主设备又可以作为从设备)

总线判优控制

- 集中式 判优逻辑放在一个部件上,如放在cpu中 又分三种:1.链式查询 2.计数器定时查询 3.独立请求方式

- 分布式 判优逻辑放到各个设备或设备端口

链式查询方式

BR:所有部件都是通过一条线提出的总线请求,不知道哪个设备优先权更高。

BG:逐个查询。各个设备优先级和BG查询顺序有关。(对电路故障特别敏感,出现故障会无法向下传。速度慢,需要一直向下查询。但是该结构简单)

定时器定时查询方式

设备地址:地址由计数器给出。

也是先从接口0开始查询,若接口0无请求,计数器会加1。

计数器的启动值可以配置,比如配置为上一次停止计数值开始,则变成了循环优先级。

设备地址线位宽和外部设备数量有关。

独立请求方式

上面都是按顺序查找,

排队器:可预先设备优先级。还可以自适应优先级,重要设备给与高优先级。

二,总线通信控制

1.目的 解决通信双方协调配合问题

2.总线传输周期 主设备和从设备完成一次完整可靠的传输所需时间。

- 申请分配阶段 主模块申请,总线仲裁决定

- 寻址阶段 主模块向从模块给出地址和命令

- 传数阶段 主模块和从模块交换数据

- 结束阶段 主从模块撤销相关信息

3.总线通信的四种方式

- 同步通信 由统一(定宽定距)时标控制数据传送

- 异步通信 采用应答方式,没有公共时钟标准

- 半同步通信 同步、异步结合(主要解决不同速度设备之间的通信问题)

- 分离式通信 充分挖掘系统总线每一瞬间的潜力

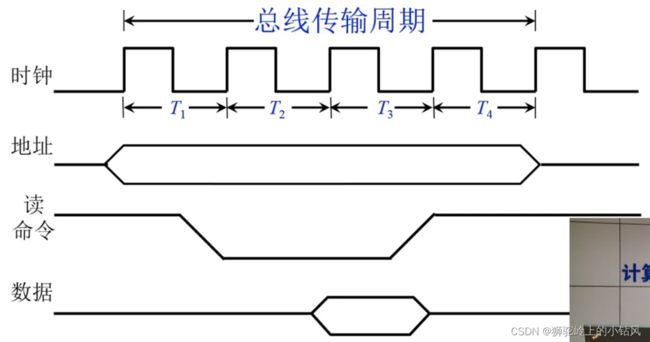

(1)同步式数据输入

固定时间点给出固定操作

t1时钟上升沿,必须给出地址信号。t2时钟上升沿,必须给出读命令信号。t3时钟上升沿之前,从设备必须给出数据信号。t4时钟周期上升沿,数据信号和控制信号撤销。

(2)同步式数据输出

强制同步,对多个不同的速度模块,必须选择速度最慢的模块作为统一时标。

(3)异步通信

和同步相比,不用定宽时标,增加了两条线。

主设备发出通信请求,从设备接收到通信请求后进行应答。之后主、从设备撤销请求、应答。在该过程中,主设备不管是否接收到应答信号,一段延时后都会撤销请求信号。从设备不管主设备是否接收到应答信号,都会撤销应答信号。(不互锁,通信可靠性有问题)

主设备发出通信请求,从设备接收到请求后,发出应答信号。主设备接收到应答信号后,撤销请求。如果接收不到,请求保持。 但是从设备不管总设备是否接收到应答信号。一段时间后都会撤销应答信号(半互锁,有可能导致请求信号一直保持)

主设备发出通信请求,从设备接收到请求后,发出应答信号。主设备接收到应答信号后,才会撤销请求。只有主设备请求撤销以后,从设备才会撤销自己的应答信号。 (全互锁)

(4)半同步通信(同步、异步结合)

同步 发送方用系统时钟前沿发信号

接收方用系统时钟后沿判断识别

异步 允许不同速度的模块和谐工作

增加一条“等待”响应信号 ~wait

以输入数据为例的半同步通信时序

t1 主模块发地址

t2 主模块发命令

tw 当~wait为低电平时,等待一个t (t3到来前,从模块发出wait信号。主设备如果检测到wait信号为低电平,就会插入一个t,等待wait信号。重复检测)

。。。。

(如cpu和主存之间,cpu速度快于主存,t3之前从模块无法提供数据)

t3上升沿到来之前,从模块必须提供数据

t4从模块撤销数据,主模块撤销命令

允许不同设备的主从设备进行交互。

以上三种通信的共同点

一个总线传输周期(以输入数据为例)

- 主模块发地址、命令 占用总线

- 从模块准备数据 不占用总线,总线空闲

- 从模块向主模块发数据 占用总线

(5)分离式通信

充分挖掘系统总线每一个瞬间的潜力

一个总线传输周期

- 子周期1 主模块申请占用总线,使用完后即放弃总线的请求

- 子周期2 从模块申请占用总线,将各种信息传送至总线上

主模块可以变成从模块

分离式通信特点

- 各模块有权申请占用总线(所有模块都可以从从模块变成主模块)

- 采用同步同步通信方式,不等对方回答

- 各模块准备数据时,不占用总线

- 总线被占用时,无空闲(一定在数据通信或传输命令)