一篇博客让你横扫数电常考所有集成电路芯片(已更新50%持续更新)

目录

前言:

一、TTL电路和CMOS电路的区别

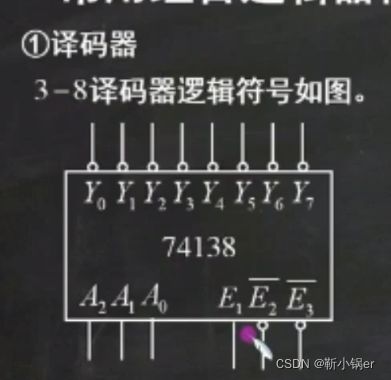

二、74LS138(74HC138)

1.两片3-8译码器级联成4-16译码器

2.用38芯片设计全加器

三、74LS48(74HC148)

1、74148芯片功能验证

2.74148芯片级联

四、74LS151(74HC151)和74LS153(74HC153)

1、74HC151功能验证

2.两片74HC151芯片级联

3.74hc151实现全加器

前言:

数电学习中我们经常会遇见很多令人烦恼的集成电路芯片,74系列芯片一度称为我数电仿真的噩梦,这里我们简单介绍一下数电学习中常见的芯片。但在此之前先简单说明一下ttl电路和cmos电路的区别,我们日常学习的芯片也多由有这两种电路组成,一样效果的芯片如果是CMOS电路的就是我们常见的HC系列,而如果是ttl电路的话就是LS系列芯片。

一、TTL电路和CMOS电路的区别

1) CMOS是场效应管构成(单极性电路),TTL为双极晶体管构成(双极性电路)

2)COMS的逻辑电平范围比较大(5~15V),TTL只能在5V下工作

3)CMOS的高低电平之间相差比较大、抗干扰性强,TTL则相差小,抗干扰能力差

4)CMOS功耗很小,TTL功耗较大(1~5mA/门)

5)CMOS的工作频率较TTL略低,但是高速CMOS速度与TTL差不多相当

6)CMOS的噪声容限比TTL噪声容限大

CMOS集成电路的输入阻抗很高,输入端悬空,会受到感应信号的干扰而误认为是有效输入信号,易出现错误的输出,故引脚不可悬空。且由于COMS的内部为MOS管,故电流非常小,所以引脚不论是接大电阻还是小电阻,都算低电平。

对TTL门电路来说具有输入特性和负载特性,存在开门电阻Ron和关门电阻Roff,若Ri小于关门电阻,则相当于引脚接了低电平;反之,若Ri大于开门电阻,则相当于引脚接了高电平。在使用TTL时,为了避免多余输入端拾取干扰,一般将多余输入端接高电平,或者与有用端并接。

所以ttl电路悬空时可以看作是输入端接一个无穷大的电阻,当输入电阻大于0.7KΩ时,输入电平就变为阈值电压UTH即为高电平,所以相当于逻辑1。

二、74LS138(74HC138)

38译码器最常见的译码器。

它有三根输入线,可以输入三位二进制数码,共有八种状态组合,即可译出 8 个输出信号。

具体看一下38译码器的相关效果验证已经考试常考点。

1.两片3-8译码器级联成4-16译码器

下面是仿真示意图

具体是如何实现两片38译码器的级联效果呢?

首先我们主观上思考一下如何由3-8译码器级联成4-16译码器,输出端不用考虑,8+8=16;那么我们需要重点考虑的是,如何实现这里的第四个输入,其实也很好理解,第四个输入的功能就是来控制上下两片3-8译码器该使能的是那块,这样就很好理解那就让第四输入的电平翻转来控制上下两块芯片的使能,如图我们可以得知第四个输入连接的是上面芯片使能端的G1(高电平有效)和下面芯片的G2A和G2B(低电平有效),所有这时候我们可以得到效果,当第四个输入为1时上面芯片工作,当第四个输入为0时下面芯片工作,因此我们就实现了相应的效果。

2.用38芯片设计全加器

这里先看一下全加器的真值表

如图所示, 若输出S为1,则此时的输入ABC为001(1),100(4),010(2),111(7)

所以S的最小项为1,2,4,7;输出的进位Ci为1时,则此时的输入ABC为101(5),011(3),110(6),111(7),所以Ci的最小项时3,5,6,7;这里我们要实现全加器效果的话只需要将38译码器的1,2,4,7和3,5,6,7分别接出即可。

三、74LS48(74HC148)

虽然74148叫148芯片,但是实际理解之后就会知道,其实74148芯片是8-3译码器,如果说74138的作用是把3位二进制输入信号译出 8 个输出信号。那么74148就是把8个输入信号译出位3位二进制。我更喜欢把它看作一个反向的3-8译码器。

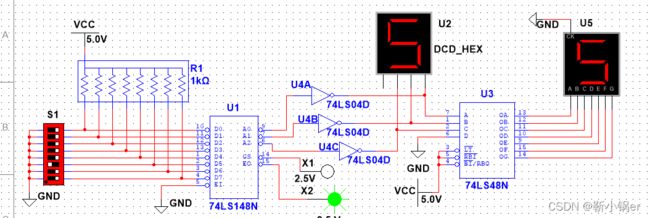

1、74148芯片功能验证

如图就是一个74LS148N(8-3编码器)和一个74LS48(4-7)译码器。

译码器有一个信号输入优先级的特性,如图我们可以得知此时第一个芯片74148的的输入为 1111 1100,此时输入信号最高的为D5,所以就算D0到D4全有信号输入,但最后的输出信号还是5(101),下一个芯片74LS48的输入端A B C D是8421码,D是高位,通过A B C D 的高低电平控制数码管的显示,如图D接低电平为0,此时的ABCD为1010,所以0101(5)输出为5

2.74148芯片级联

如图是个两个74148级联(8-3编码器)做16-4编码器,此时下面的芯片仍然是和原来一样从D0到D7作为前八个编码信号,而此时上面芯片的D0到D7作为后八个编码信号也就是D8到D15;

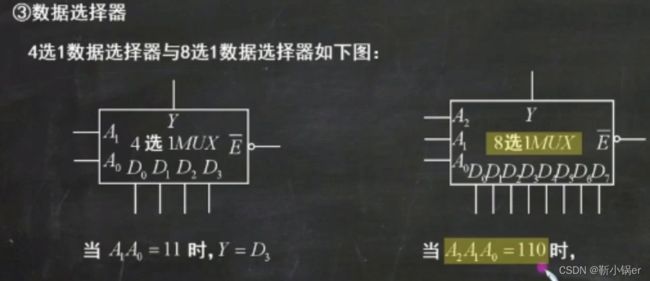

四、74LS151(74HC151)和74LS153(74HC153)

74151就是一个8选1数据选择器,数据选择器除了常规的数据输入端以外(D0到D7)以外还有数据选择端(ABC),由ABC选择出输出的信号端。

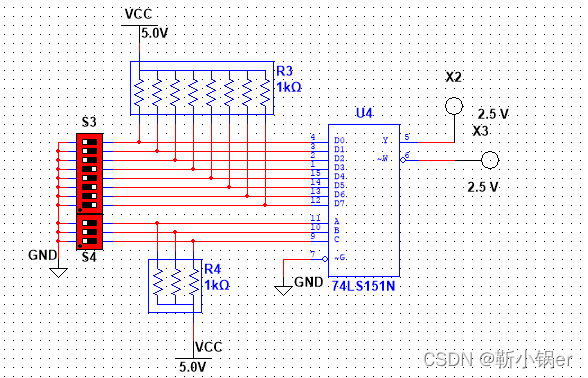

1、74HC151功能验证

如图ABC的输出为011, 所以输出的是D3,

2.两片74HC151芯片级联

两片74HC151芯片实现8选1数据选择器的功能,其主要方式其实是和138级联相类似的,1G为0使能的是74HC153上半部分的四选一数据选择器工作,2G工作使能的是74HC153下半部分的四选一数据选择器工作,所以实现8选1的数字选择器功能。

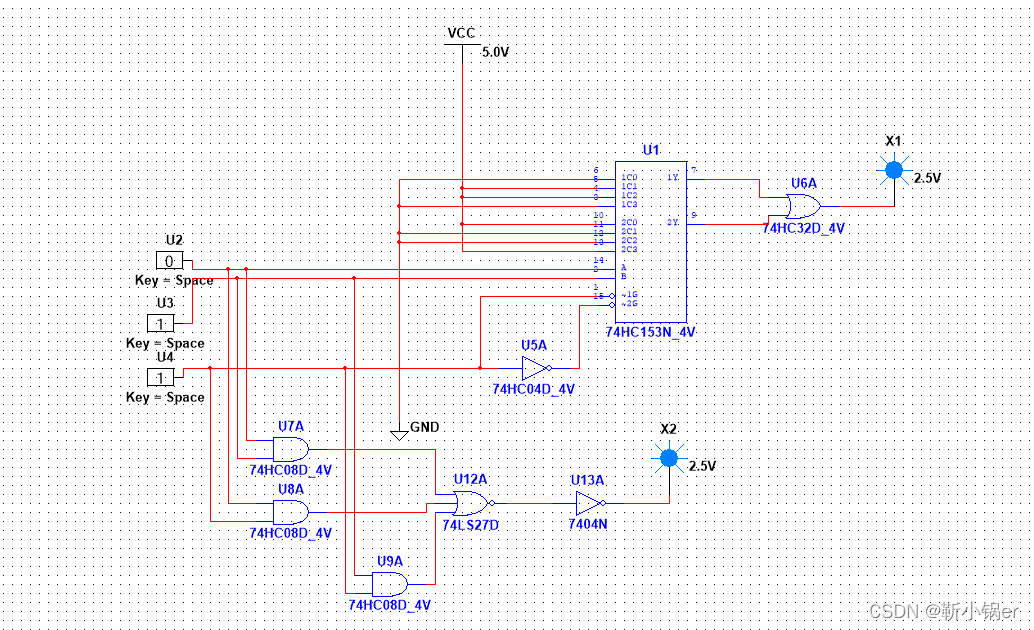

3.74hc151实现全加器

其实就是在上面构建出的8选1数字选择器的基础上进行改进,只不过根据全加器的原理,将1,2,4,7这四个输出端都接1,而进位端显示直接选用三人表决权的方式来显示进位。