电工学习笔记——DC/DC转换器回路设计指南

本资料为DC/DC转换器电路的设计提供一些提示,尽量用具体事例说明在各种制约条件下,怎样才能设计出最接近要求规格的DC/DC转换器电路。

DC/DC转换器电路的各种特性(效率、纹波、负载瞬态响应等)可根据外设元件的变更而变更,一般最佳外设元件因使用条件(输入输出规格)不同而不同,例如,当您问“怎样才能提高效率?”,回答“视使用条件而不同”或者“那要看具体情况啦”,感觉好像被巧妙地塘塞过去了,估计您也遇到过这样的情况吧。那么,为什么会出现这样的回答呢?其理由就是因为电源电路大多使用市售的商品作为电路的一部分,所以必须既要考虑大小、成本等的制约又要考虑电气要求规格来设计。

通常产品目录中的标准电路选定的元件大多是在标准使用条件下能发挥一般特性的元件,因而,并不一定能说在各种使用条件下都是最佳的元件选定。所以在各个设计中,必须根据各自的要求规格(效率、成本、贴装空间等)从标准电路进行设计变更。但要能设计出符合要求规格的电路,需要足够的知识和经验。

本资料就用具体的数值为不具备这些知识和经验的人说明哪些元件如何改变就能达到要求的动作,这样不需要进行复杂的电路计算就能快捷地使DC/DC转换器电路正常工作。至于正常工作后对设计的检验,可以自己以后细细地计算,也可以一开始就请具有丰富知识和经验的人进行检验。

DC/DC转换器的种类和特点

DC/DC转换器电路根据其电路方式主要有以下一些:

-

非绝缘型

-

基本(单线圈)型

-

电容耦合型双线圈SEPIC, Zeta,…

-

电荷泵(开关电容/无线圈)型

-

-

绝缘型

-

变压器耦合型 正向

-

变压器耦合型 回扫

-

基本型系指通过将电路工作限定为只升压或者只降压来最低限度地减少元件数目,输入侧和输出侧没有电气绝缘的类型。

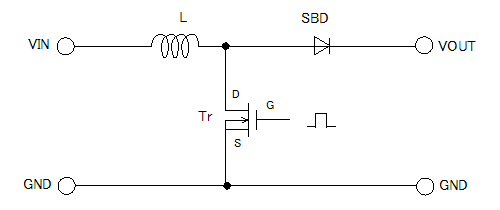

图1所示为升压电路

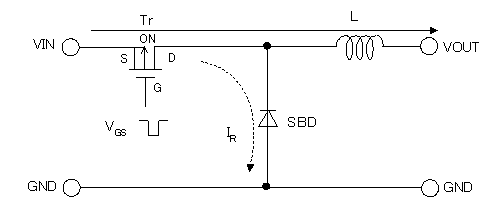

图2所示为降压电路

这些电路具有小型、便宜、纹波小等优点,随着设备的小型化对它们的需要在增加。

SEPIC、Zeta分别是在基本型的升压电路、降压电路的VIN-VOUT间插入电容器,并增加了一个线圈。而且,都可通过使用升压DC/DC转换器控制IC、降压DC/DC转换器控制IC构成升降压DC/DC转换器。但有些DC/DC转换器控制IC没有设计成用于这些电路方式,故在选用时需要注意。这些电容耦合双线圈型具有VIN-VOUT间能够绝缘的优点,但因增加线圈和电容器,效率会变低,尤其是降压时效率也大幅降低,是通常的70%~80%左右。

电荷泵型因为不需要线圈,所以其优点在于贴装面积、贴装高度都小,然而因其对多种输出电压和大电流不易制作效率好的电路,所以也有用途被限制在白LED驱动用和LCD用电源等的一面。

绝缘型的也被称为一次电源(主电源),主要被广泛用于从商用电源(AC100V~240V)变压为DC电源的AC/DC转换器、因去除噪声等理由输入侧和输出侧需要绝缘等时。因为它们使用变压器将输入侧和输出侧分离,故可以通过改变变压器的匝数比和二极管极性来构成升压/降压/反转等控制,从而,能从一个电源电路获得多个电源。尤其是使用回扫变压器的因能由较少的元件构成,有时也被用作二次电源(局部电源)电路。但是,由于回扫变压器需要用于防止内核磁饱和的空隙,所以外形尺寸较大。而正向变压器虽然易于获得大功率电源,但在一次侧需要用于防止内核磁化的复原电路,因而元件数目增加。变换器控制IC也需要输入侧和输出侧的GND分离的。

DC/DC转换器的基本工作原理

我们拿最基本的基本型来说明一下DC/DC转换器电路的升压和降压的工作原理。其它使用线圈的电路方式在升压电路和降压电路的组合或应用电路都可见到。

图3、图4说明了升压电路的工作。图3所示是FET为ON时的电流路径,虚线虽是微小的漏电流,但会使轻负载的效率变差。在FET为ON的时间里在L积蓄电流能。图4是FET为OFF时的电流路径,FET即便OFF,L也在工作要保持OFF前的电流值,线圈的左端被强制性固定于VIN,进行升压工作提供足以给VOUT接上电压的电源功率。

由此,FET的ON时间长L里积蓄的电流能越大,越能获得电源功率。但是,FET的ON时间太长的话,给输出侧供电的时间就极为短暂,FET为ON时的损失也就增大,变换效率变差。因而通常限制占空比的最大值以便不超过适宜的ON/OFF时间比(占空比)。

升压工作就是反复进行图3、图4的状态。

图3.升压电路中FET为ON时的电流路径

图4.升压电路中FET为OFF时的电流路径

图5、图6说明了降压电路的工作。图5所示是FET为ON时的电流路径,虚线虽是微小的漏电流,但会使轻负载时的效率变差。在FET为ON的时间里在L积蓄电流能的同时为输出供电。图6是FET为OFF时的电流路径。FET即便OFF,L也在工作要保持OFF前的电流值,使SBD为ON。此时,由于线圈的左端被强制性地降到0V以下,VOUT的电压下降。

由此,FET的ON时间长L里积蓄的电流能越大,越能获得大功率电源。降压时,由于FET为ON时也能给输出供电,所以不需要限制占空比的最大值,因而输入电压低于输出电压时,FET为常ON状态,不能进行升压工作,故输出电压也降低到输入电压以下。

降压工作就是反复进行图5和图6的状态。

图5.降压电路中FET为ON时的电流路径

图6.降压电路中FET为OFF时的电流路径

DC/DC转换器回路设计的4个要点

DC/DC转换器电路所要求的规格中应重视的项目如下:

-

稳定工作(=不会因异常振动等误动作、烧损、过电压而损坏)

-

效率大

-

输出纹波小

-

负载瞬态响应好

这些可通过变更DC/DC转换器IC和外设元件得到某种程度的改善。这4个项目的加权因各项具体应用而不同,下面从选择各元件的观点出发,以怎样才能改善这4个项目为中心进行说明。

DC/DC转换器开关频率的选择

DC/DC转换器IC具备固有的开关频率,频率的不同会对各种特性产生影响。一般来说,开关频率的不同会对表2中所示的各种特性产生影响。

表2 开关频率与各种特性的关系

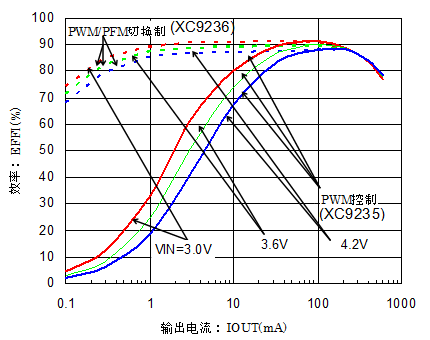

图7~图8以XC9235/XC9236(1.2MHz)和XC9235/XC9236(3MHz)为具体例子表明开关频率与效率的关系。效率明显呈现表2中所示的结果。效率最大的电流值不同是因为不同的开关频率适合的感应系数值也不同的缘故。对于结构相同的线圈,感应系数越大直流电阻越增加,重负载时的损失增加,由此,效率最大的电流值越是低频的越会向轻负载侧移动。相反,频率高则因FET的充放电次数增加和IC自身的静态消耗电流增大,3MHz产品比1.2MHz产品在轻负载时的效率大幅度变差。

综合来看这些影响,可知1.2MHz产品的效率最大值大(=效率图的峰值最大),效率最大的输出电流值小(=效率图的峰值偏左)。此外,PFM工作时,轻负载时的频率都进一步下降,效率明显得到改善。

图7.XC9235/XC9236

VOUT=1.8V设定(振荡频率1.2MHz)

图8.XC9235/XC9236

VOUT=1.8V设定(振荡频率3MHz)

图9.XC9235/XC9236

图7~图8的测试电路

场效应晶体管(FET)的选择

对电压・电流的绝对最大额定值,选择以减少开关时的尖峰噪声和脉冲噪声的故障率为目的的、额定值为使用电压的1.5倍~2倍左右、RDS和CISS引起的损失最小的产品,可构成效率好的DC/DC转换器电路。虽然RDS和CISS都是越小损失也越小,但因RDS和CISS成反比关系,改善损失大的一方效果更好。

CISS引起的损失是FET的栅源极间充放电时被丢弃的功率,可用CISSVGS2f/2来表示。驱动电压和开关频率越大损失就越大,由于重负载时和轻负载时损失值基本相同,所以会使轻负载时的效率大幅度变差。

而RDS引起的损失是作为因FET的漏源极间电阻成分发生的热而放出的,它的值用RDSID2来表示,负载越大其值越是增大。因此,可以说轻负载时减少CISS引起的损失对提高效率的效果较好,重负载时减少RDS引起的损失效果较好。将上述内容归纳于下面的表3中。

表3 选择FET之例

输入电流可用输出(负载)电流×输出电压÷输入电压÷效率来计算求出。效率未知时,可姑且升压时采用70%,降压时采用80%左右来计算。

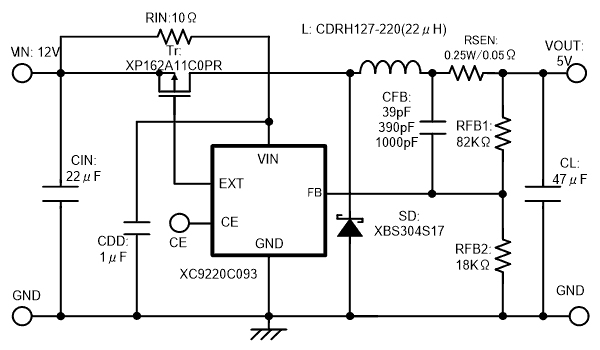

图10是图11所示的XC9220C093的外设元件中只更换了FET后测试的效率图。其中所用的各FET的规格值如表4中所示。

从图10来看,使用RDS小的FET(XP162A11C0)呈现能驱动更大电流,重负载时的效率得到若干改善的趋势。但也可知进一步大幅度降低轻负载时的效率,不必要地使用电流驱动能力大的FET是不适当的。

图10. XC9220C093

更换FET后的效率変化

图11. XC9220C093

图10的测试电路

表4 FET的各种特性

线圈的选择

开关频率不同的话,最佳L值也不同,因为线圈的电流与FET的ON时间成正比,与L值成反比。

线圈引起的损失表现为线圈的绕线电阻RDC、铁氧体磁心产生的损失等的合计值。不过对于2MHz左右的开关频率,可以认为线圈的大部分损失是RDC引起的损失,首先应选择RDC小的线圈。但是为了减小RDC而选择L值过小的线圈的话,在FET为ON的时间内电流值过大,FET、SBD、线圈产生的热损失变大,效率下降。而且,因电流增加,纹波也增大。

相反,L值过大的话,RDC变大,不仅重负载时的效率变差,而且铁氧体磁心发生磁饱和,L值急速减少,这样就不能发挥出线圈的性能,陷入电流过大引起发热的危险状态。因而,为了在L值大的线圈流经大电流,形状上必须有一定程度的大小,以避免磁饱和。

综上所述,从相对于开关频率的外形尺寸和效率两个方面来考虑的话,适当的L值已被限定。表5所示为各开关频率值的标准L值。为VIN,VOUT在6V 以下的参考数据。

图12、图13所示是图14所示的XC9104D093(升压)电路图12所示的是图13的XC9104D093升压电路的效率图, 出示只变更L值的效率变化。

同样,图14、图15所示是图16所示的XC9220A093(降压)电路的效率和纹波的实例。

两个实例都是线圈结构相同时,增大L值则最大输出电流值减少,轻负载时的效率增大,纹波减少。由此可知选择与输出电流相适应的L值是非常重要的。

图12. L值与效率的关系

(升压时:XC9104D093)

图13. XC9104D093

图12的测试电路

图14. L值与效率的关系

(降压时:XC9220A093)

图15. L值与纹波的关系

(降压时:XC9220A093)

图16. 图14、图15

XC9220A093的测试电路(PWM=CE=VIN)

肖特基势垒二极管(SBD)的选择

有关绝对最大额定值,根据与FET同样的理由,应选择相对于使用条件的1.5倍~2倍左右的产品。SBD的损失为正向热损失VF×IF和反向漏电流IR引起的热损失的合计值。因此,选择VF、IR都小的产品比较理想。但是,VF与IR成反比关系,一般要视负载电流而选用。VF在重负载时大,考虑到IR与负载无关为一定的值,所以轻负载时选择IR小的产品对提高效率的效果较好,重负载时选择VF小的产品效果较好。将上面的内容归纳于下面的表6中。

表6 选择SBD的要点

图17所示是图18所示的XC9220A093电路中只用表7所示的SBD变更时的效率变化。可看到与XBS203V17相比, XBS204S7的IR小,所以轻负载时的效率高,而因VF较大,所以重负载时效率低。

图17. XC9220A093

SBD的选择与效率的不同

图18. 图17的测试电路

XC9220A093(降压时)

表7 测试了图17的SBD的各种特性

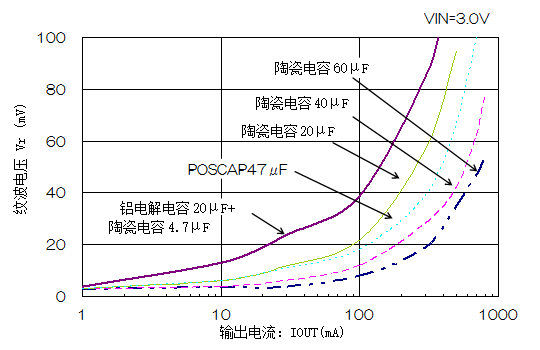

CL的选择

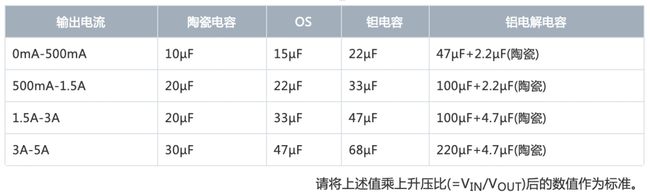

CL越大则纹波越小,但过分大的话,电容器的形状也大,成本提高。CL由所需的纹波大小而定。首先,大致以10mV~40mV的纹波大小为目标,升压时从表8的电容值开始,降压时从表9的电容值开始。但是,不支持低ESR电容器的DC/DC有异常振荡的危险,以连续模式使用时要想采用低ESR电容器的话,应预先检查负载瞬态响应,确认输出电压能否及时稳定(振荡大致在2次以内即收敛)。

图19是图20所示的XC9104D093中只更换了CL后测试的输出纹波变化。纹波与ESR成正比,与电容值成反比地增大。铝电解电容时,没有并联的陶瓷电容的话,ESR过大难以获得输出电流。

表8 升压时CL的标准

表9 降压时CL的标准

图19.随CL值变化的输出侧纹波例(XC9104D093)

图20. XC9104D093 图19的测试电路

CIN的选择

虽然不及CL对输出稳定性的影响大,但CIN也是电容值越大、ESR越小则输出稳定性越好,纹波也越小。大到某种程度,降低输出纹波的效果会变小,从防止对输入侧的电磁干扰(EMI)的意义上说,电容值应从CL的一半左右开始探讨较好。

图22同样显示了使图23中的CIN变化时输入侧纹波大小会发生怎样的变化。虽然是一般不常进行确认的数据,但对降低EMI是很重要的数据。CIN不会因ESR太小而输出振荡,所以尽量使用低ESR电容为宜。

RFB1, RFB2的选择

使用FB(反馈)产品时,RFB1、RFB2用于决定输出电压,对同一输出电压有时可考虑多种组合。此时选择RFB1+RFB2=150kΩ~500kΩ比较妥当。这里成为问题的是轻负载时的效率和重负载时的输出稳定性。因为流向RFB1、RFB2的电流没有被作为输出功率使用,而视作DC/DC转换器的损失,所以要想提高轻负载时的效率的话,要将RFB1、RFB2设定得大一些(RFB1+RFB2<1MΩ左右)。而要想提高重负载时的瞬态响应的话,则要做好轻负载时的效率差的准备。

CFB的选择

CFB是纹波反馈调整用电容器相位补偿电容,该值也会影响负载瞬态响应。根据L值,表10中的CFB值为最佳值。过小于该值或过大于该值工作稳定性都差。

图中以XC9220C093为例说明了CFB的影响。在图26的电路中,RFB1=82kΩ时,fZFB=10kHz的CFB为390pF左右。(图23=39pF)、(图24=390pF)和(图25=1000pF)是对改变CFB 时的负载瞬态响应的比较。39pF的话,负载变重时电压急剧下降,电压恢复到恒定状态的时间短,而1000pF的话,负载变重时的瞬间电压下降虽小,但电压恢复到恒定状态的时间长。

表10 决定最优CFB的标准fZFB

图21. XC9220C093负载瞬态响应(IOUT=0mA⇔200mA, CFB=39pF)

图22. XC9220C093负载瞬态响应(IOUT=0mA⇔00mA,CFB=390pF)

图23. XC9220C093负载瞬态响应(IOUT=0mA⇔200mA,CFB=1000pF)FB=1000pF)

图24. XC9220C093 图23~图25的测试电路

图25所示为加上RFB1和fZFB时标准CFB的值。