PCIE——第 9 章——流量控制

摘要:PCIE——第 9 章——流量控制

目录

第 9 章 流量控制

9. 1 流量控制的基本原理

9. 1. 1 Rate⁃Based 流量控制

9. 1. 2 Credit⁃Based 流量控制

9. 2 Credit⁃Based 机制使用的算法

9. 2. 1 N123 算法和 N123 + 算法

9. 2. 2 N23 算法

9. 2. 3 流量控制机制的缓冲管理

9. 3 PCIe 总线的流量控制

9. 3. 1 PCIe 总线流量控制的缓存管理

9. 3. 2 Current 节点的 Credit

9. 3. 3 VC 的初始化

9. 3. 4 PCIe 设备如何使用 FCP

9. 4 小结

参考文章:

第 9 章 流量控制

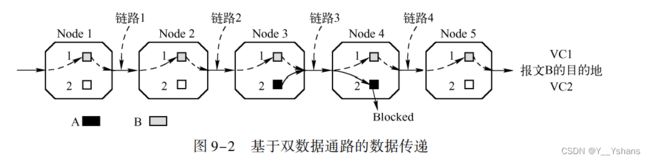

流量控制 ( Flow Control) 的概念起源于网络通信。 一个复杂的网络系统由各类设备 (如交换机、 路由器、 核心网) , 与这些设备之间的连接通路组成。 从数据传输的角度来看, 整个网络中具有两类资源, 一类是数据通路, 另一类是数据缓冲。

数据通路是网络上最珍贵的资源, 直接决定了数据链路可能的最大带宽; 而数据缓冲是 另外一个重要的资源。当节点3和4被占用的时候,B无法从节点1顺利传递到节点5。在现代网络节点中设置了多个虚通路 VC, 不同的数据报文可以使 用不同的通路进行传递, 从而有效解决了单数据通路带来的问题。

9. 1 流量控制的基本原理

流量控制的主要作用是在发送端和接收端进行数据传递时, 合理地使用物理链路, 避免 因为接收端缓冲区容量不足而丢弃来自发送端的数据, 从而要求发送端重新发送已经发送过 的报文, 并最终有效地利用网络带宽。

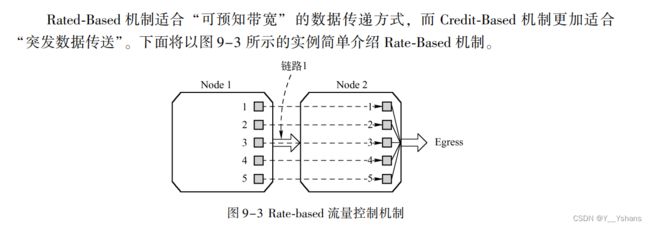

9. 1. 1 Rate⁃Based 流量控制

假设每个VC的传输速率是1/4 rate,那么5个VC就是5/4,超过了1。Rate⁃Based 机制 规定每一个 VC 在发送一定数量的报文后, 将主动地将相应 VC 的 Rate 调整为 Rate 减去 ADR (Additive Decrease Rate) , 直到 Rate 等于 MCR ( Minimum Cell Rate) ;

对于多数长度 “不可预知” 的突发数据传递, 该机制并不能完全适用。 因为 Rate⁃ Based 流量控制的实时性较弱, 当一个 VC 需要瞬间传递大量报文时, Rate⁃Bsed 机制不能及 时地为这条 VC 提供足够的数据传送率; 而当一个 VC 拥塞时, 也不能及时地降低数据传送 率。 因此使用 Rate⁃Based 机制并不能满足网络上突发数据传送的需要, 此时需要使用 Credit⁃ Based 机制对流量进行控制。

9. 1. 2 Credit⁃Based 流量控制

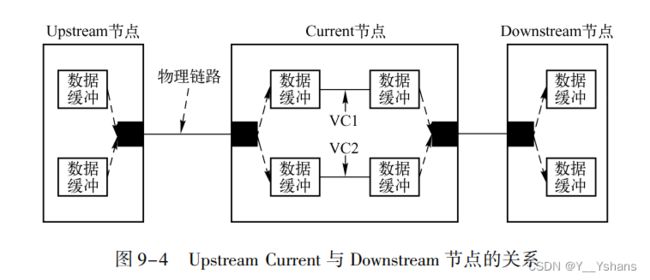

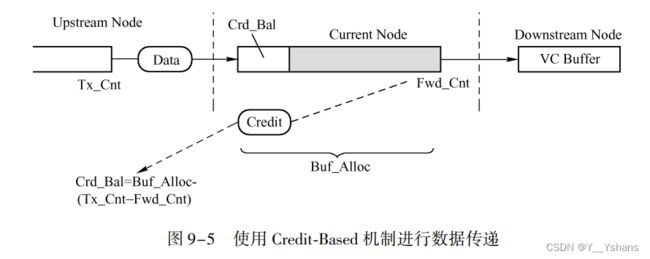

Credit⁃Based 机制需要使用以下参数进行报文传递。

● Buf_Alloc 参数。 该参数保存在 Current 节点中接收数据缓冲的总大小。 Upstream 节点 能够发送的数据报文总数不能大于该参数。

● Crd_Bal 参数。 该参数是 Upstream 节点可以发送的数据报文数, Current 节点需要定时 向 Upstream 节点发送 Credit 报文。 Upstream 节点收到该报文后, 使用该报文中的 “Credit” 同步 Crd_Bal 参数。 Upstream 节点可以发送的数据报文数不能超过 Credit_ Bal 参数。

● Tx_Cnt 参数。 该参数为 Upstream 节点已经发送的数据报文数。

● Fwd_Cnt 参数。 该参数为 Current 节点转发到 Downstream 节点的数据报文数。 Credit⁃Based 流量控制使用的各个参数之间的关系如图 9-5 所示。

9. 2 Credit⁃Based 机制使用的算法

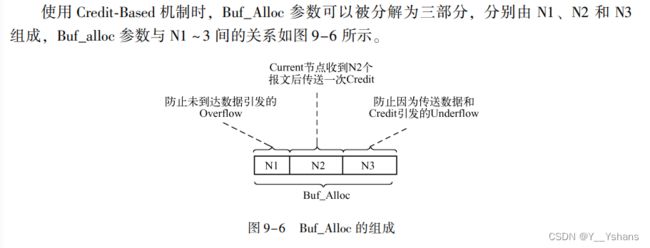

(1) N1 缓冲

该参数用来防止因为线路延时而造成的 Overrun

(2) N2 缓冲

N2 的值与 VC 的设置有相关。N2 的值越大, Buf_Alloc 参数的值也越大, 节点发送 Credit 报文的频率也越低, 从而 Credit 报文占用数据通路带宽的比例越小; N2 的值越小, 则 Buf_Alloc 的值也越小, 向 Up⁃ stream 节点发送的 Credit 报文的频率越高, Credit 报文占用数据通路带宽的比例也越大。

(3) N3 缓冲

N3 的容量可以影响数据通路 的有效带宽, 在流量控制机制的实现中, 如果 N3 过小, 那么 Current 节点将出现 Under⁃run 的现象, 从而影响数据通路的有效带宽。 根据上述数学模型, H. T. Kuang 与 Alan Chapman 提出了三种流量控制算法, 分别为 N123、 N123 + 和 N23 算法。

9. 2. 1 N123 算法和 N123 + 算法

了解即可

9. 2. 2 N23 算法

了解即可

9. 2. 3 流量控制机制的缓冲管理

上文讲述了基于单个 VC 的流控机制, 实际上在 Upstream、 Current 和 Downstream 节点 中一般含有多个 VC。 多个 VC 之间如何合理地使用缓存值得重点关注, 在实际设计中, 可 以为每一个 VC 设置独立接收缓存, 也可以使多个 VC 共享同一个接收缓存。 在 FCVC 的实 现中, 可以根据实际情况选择独立缓存或者共享缓存。

其中, 每一个 VC 都使用独立接收缓存的流量控制方法称为静态 ( Static) 流量控制;而使用共享缓存的流量控制方法称为自适应 (Adaptive) 流量控制。目前接收缓存的分配常使用两种算法, 分别是 Sender⁃Oriented 和 Receiver⁃Oriented 管理 算法。

9. 3 PCIe 总线的流量控制

PCIe 总线的流量控制机制由事务层和数据链路层协调实现, 而对系统软件透明。 PCIe 总线使用 Credit⁃Based 流量控制机制, 其中 Credit 报文以 DLLP 的形式从 Current 节点反馈到 Upstream 节点。 在 PCIe 总线中, 数据报文首先以 TLP 的形式通过数据链路层, 而到达数据 缓存时被分解为 Header 和 Data 两个部分, 分别存放到不同的接收缓存队列中。

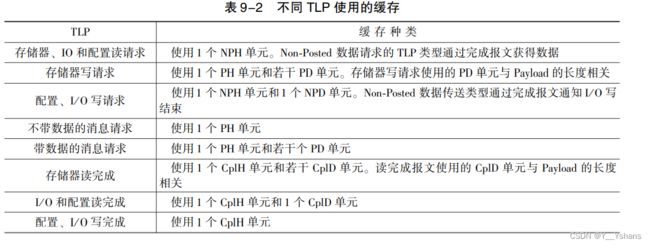

9. 3. 1 PCIe 总线流量控制的缓存管理

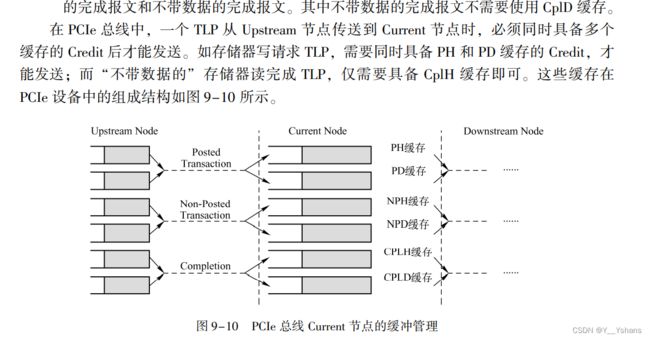

在 PCIe 总线的节点中, 一个 VC 的接收缓存由 PH ( Posted Header) 缓存、 PD ( Posted Data) 缓存、 NPH (Non⁃Posted Header) 缓存、 NPD (Non⁃Posted Data) 缓存、 CplH ( Com⁃ pletion Header) 缓存和 CplD (Completion Data) 缓存组成。

● PH 缓存存放存储器写请求 TLP 和 Message 报文使用的 TLP 头。

● PD 缓存存放存储器写请求 TLP 和 Message 报文使用的 Payload。

● NPH 缓存存放 Non⁃Posted 请求 TLP 使用的 TLP 头。

● NPD 缓存存放 Non⁃Posted 请求 TLP 使用的 Payload。 在 Non⁃Posted 请求 TLP 中, 如存 储器读请求 TLP 并不含有 Payload 字段, 但是 I / O 和配置写请求 TLP 使用 Payload 字段。

● CplH 缓存存放完成报文使用的 TLP 头。

● CplD 缓存存放完成报文使用的 Payload。

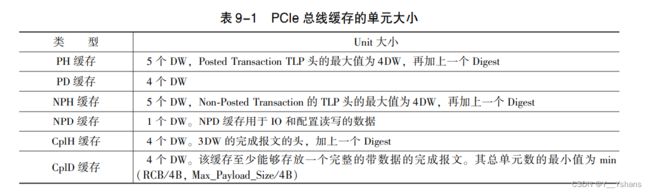

PCIe 总线规范将这些缓存使用的 Unit 统称为 FC (Flow Control) Unit, 下文将以 FC Unit 简称这些对应缓存的 Unit。 因为 Header 的大小固定, 所以 Header 缓存能够精确地预知可以 容纳几个 Header; 而由于 Data 的大小并不固定, Data 缓存无法精确预知可以存放几个 Data, 当然 Data 缓存也不可能将 Data 的基本单位设置为 Max_Payload_Size 参数。 因为这样做不仅 不合理, 而且非常浪费资源。 将 Header 和 Data 缓存分离, 有利于 Data 缓存使用类似 Adap⁃ tive 流量控制的方法使所有 Data 共用一个缓存, 从而提高了 Data 缓存的利用率。 但是也造 成 TLP 因为不能同时具有 Head 和 Data 缓存, 而无法传送。

PCIe 总线使用 Credit⁃Based 流控机制, Upstream 节点在发送 TLP 时, 必须首先获得 Cur⁃ rent 节点相应缓存的 Credit。 如 Upstream 节点发送存储器写请求时, 需要同时具有 Current 节 点中 PH 缓存和 PD 缓存的 Credit, 才能进行。

PCIe 总线使用 Credit⁃Based 流控机制, Upstream 节点在发送 TLP 时, 必须首先获得 Cur⁃ rent 节点相应缓存的 Credit。 如 Upstream 节点发送存储器写请求时, 需要同时具有 Current 节 点中 PH 缓存和 PD 缓存的 Credit, 才能进行。

9. 3. 2 Current 节点的 Credit

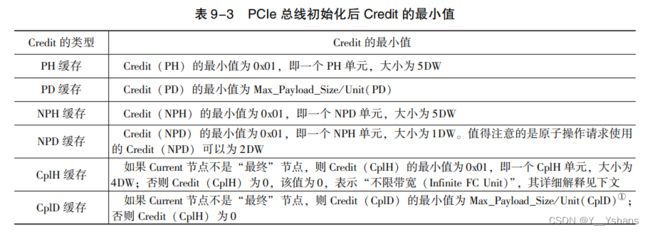

在 PCIe 总线中, Credit⁃Based 流量控制的数据传送规则仍然是 Upstream 节点获得 Credit, 之后向 Current 节点发送数据; 而 Current 节点将一定数量的报文 (N2) 转发到 Downstream 节点之后, 将向 Upstream 节点反馈 Credit。 PCIe 总线规范也将向 Upstream 节点反馈 Credit 的 过程称为 Advertisement。

9. 3. 3 VC 的初始化

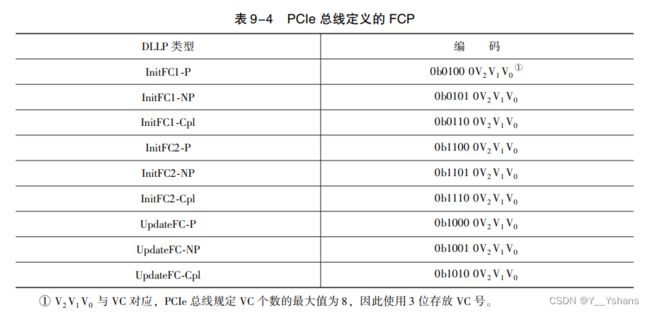

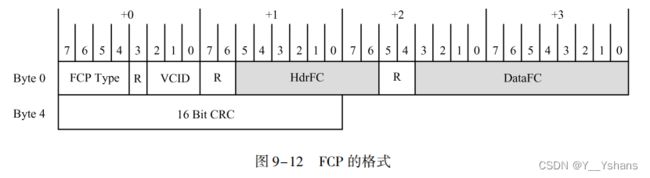

PCIe 总线使用 FCP (Flow Control Packets) 传递 Credit 信息, FCP 是一种 DLLP, 该报文 的使用与事务层的接收缓存直接相关, 但是对事务层透明, 该报文产生于数据链路层, 终止 于数据链路层。

由上表所示 FCP 共分为三大类 InitFC1、 InitFC2 和 UpdateFC。 在这三类报文中有 3 个重 要的字段。 其中 HdrFC 字段存放 Header 的 Credit; DataFC 字段存放 Data 的 Credit; 而 VC ID 字段存放不同的 VC 号。

9. 3. 4 PCIe 设备如何使用 FCP

PCIe 总线完成流量控制的初始化之后, Current 节点、 Upstream 节点和 Downstream 节点 通过发送 UpdateFC⁃P、 UpdateFC⁃NP 和 UpdateFC⁃Cpl 报文进行流量控制。P272

9. 4 小结

本章仅使用了较少的篇幅讲述 PCIe 总线的流量控制机制, 而重点讨论通用流量控制机 制的基本原理。 PCIe 总线由于强调与 PCI 总线的兼容, 流量控制机制的设计并不完美。 PCIe 总线的主要应用领域依然是 PC, 在这个领域中, 流量控制并不是最重要的。

参考文章:

PCI_Express_体系结构导读——王齐